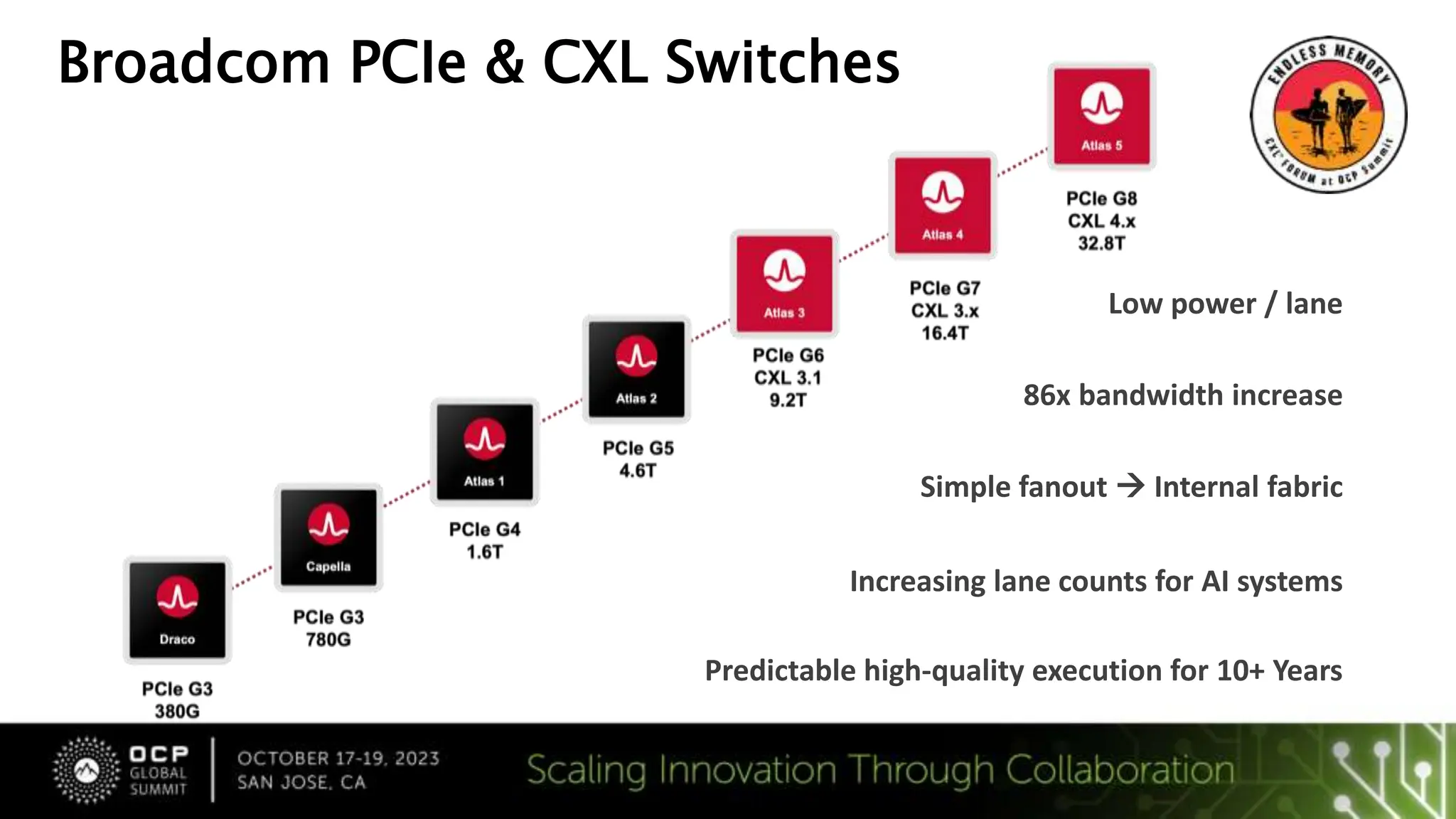

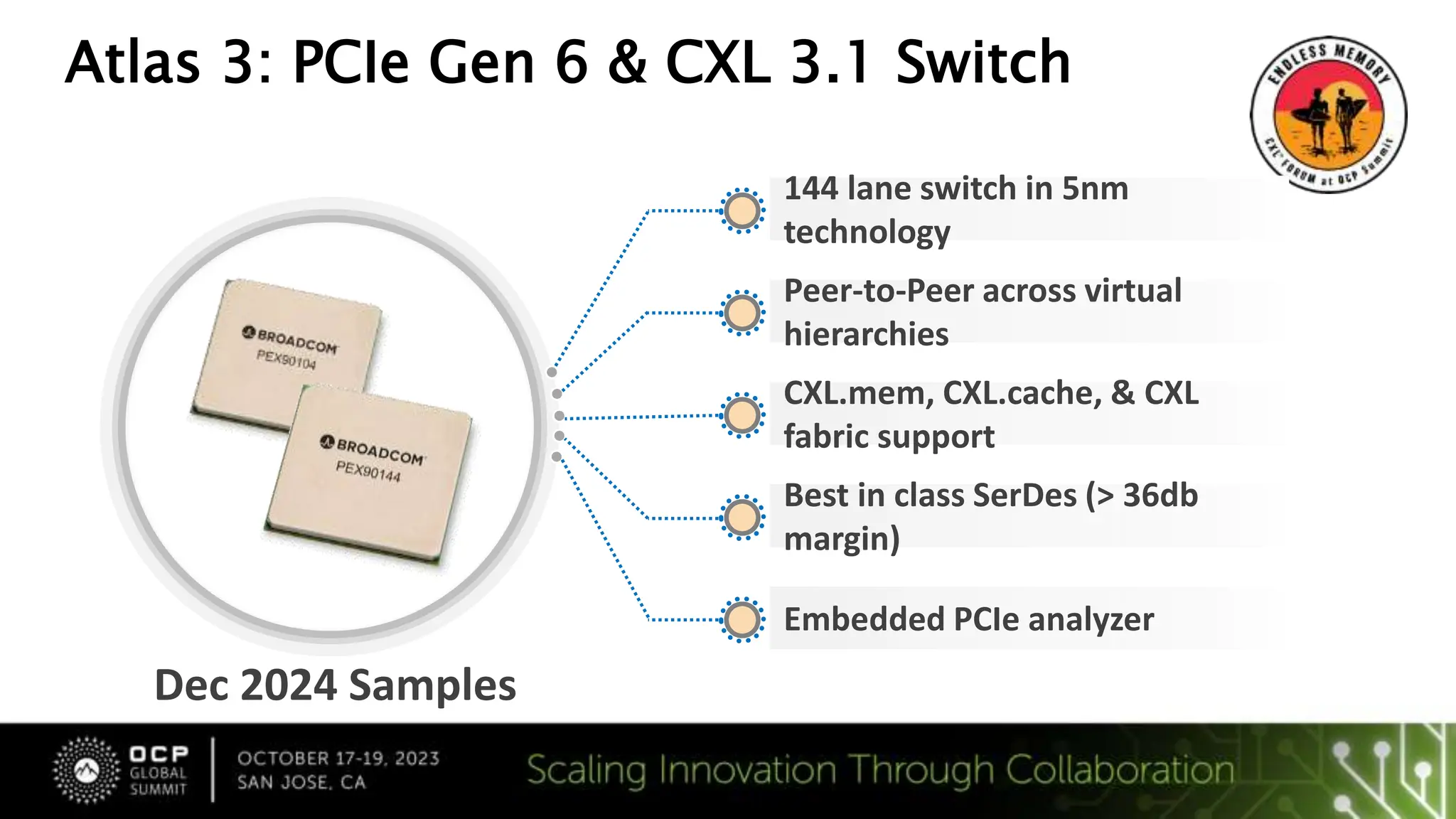

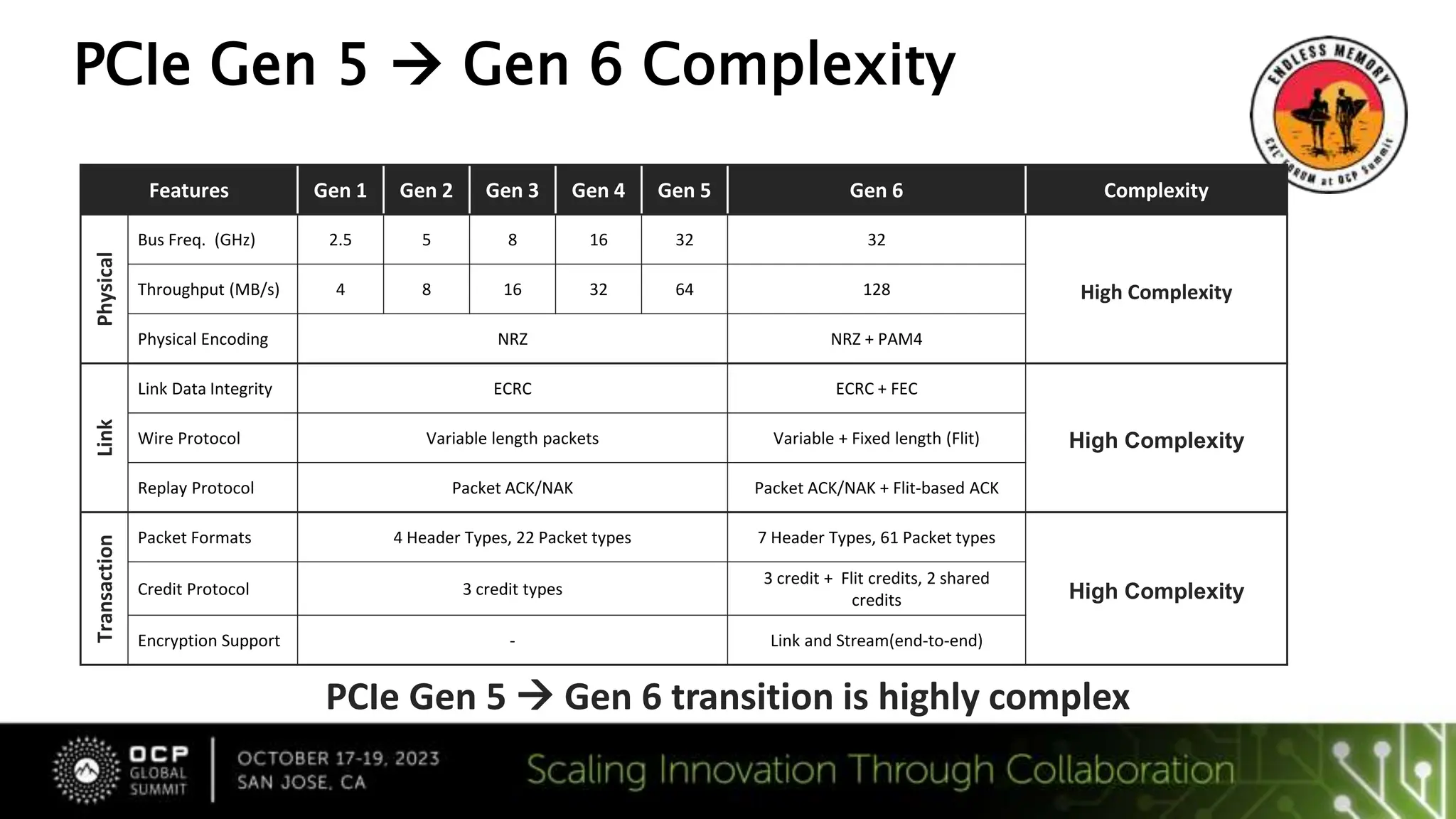

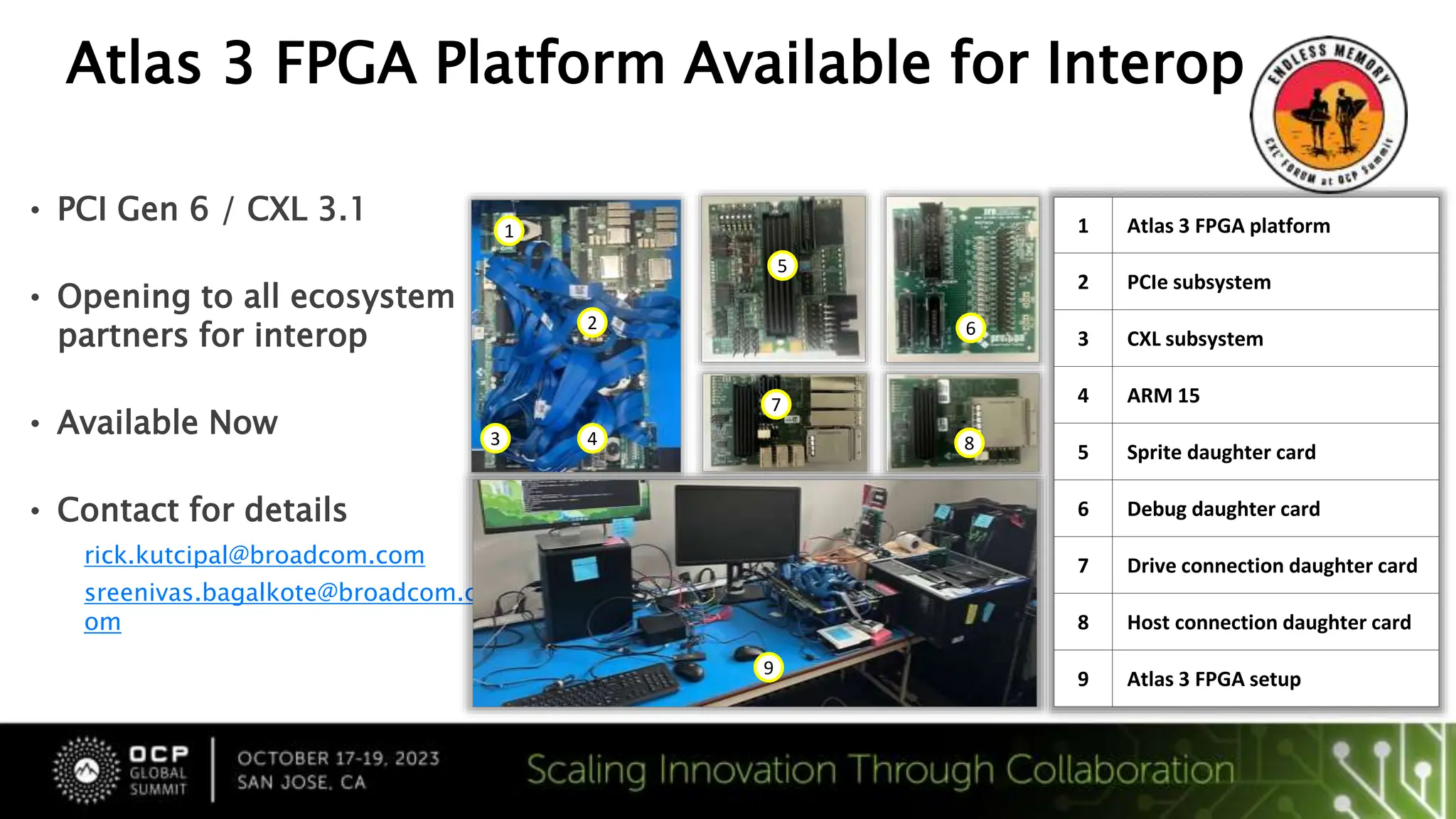

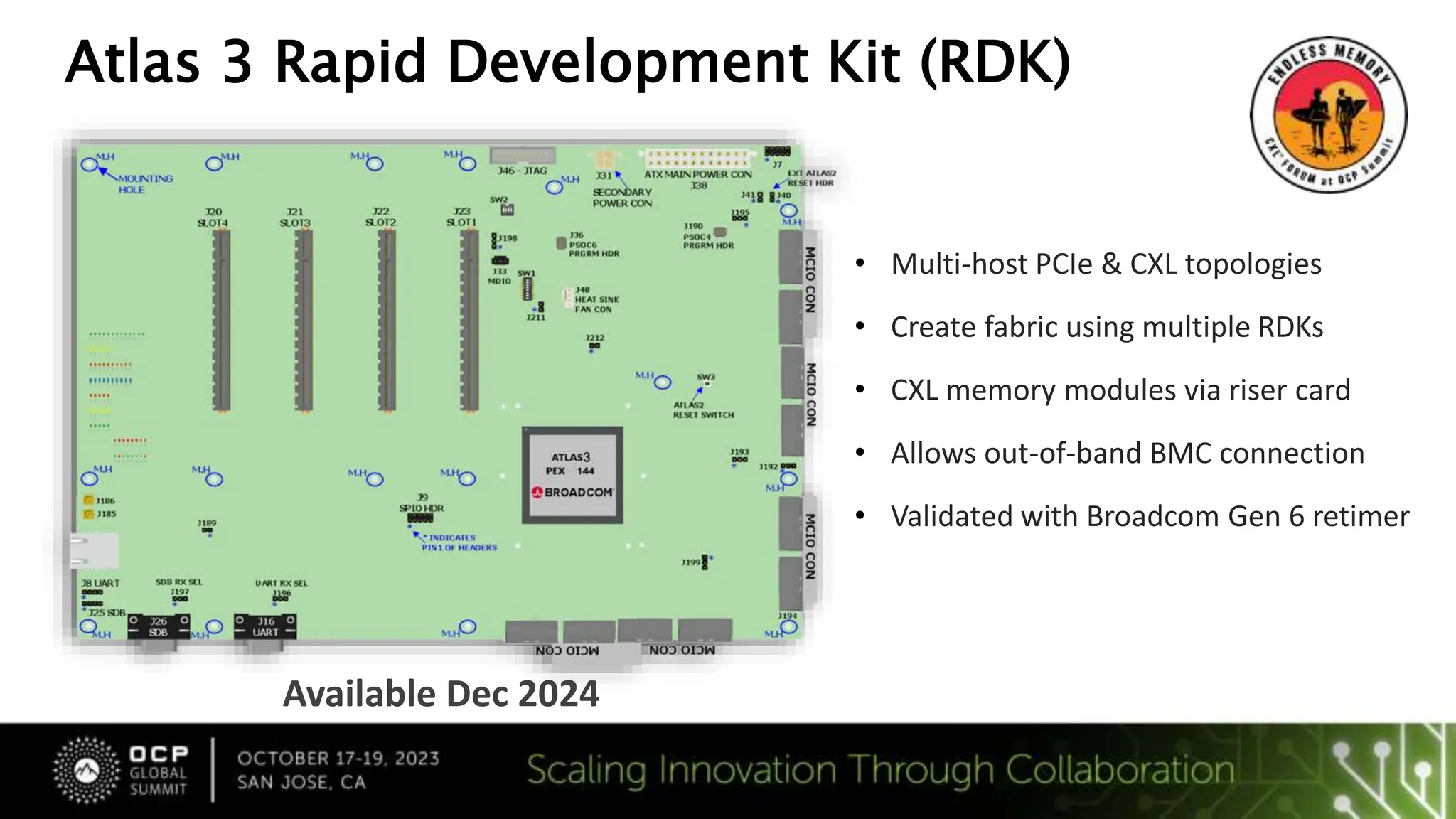

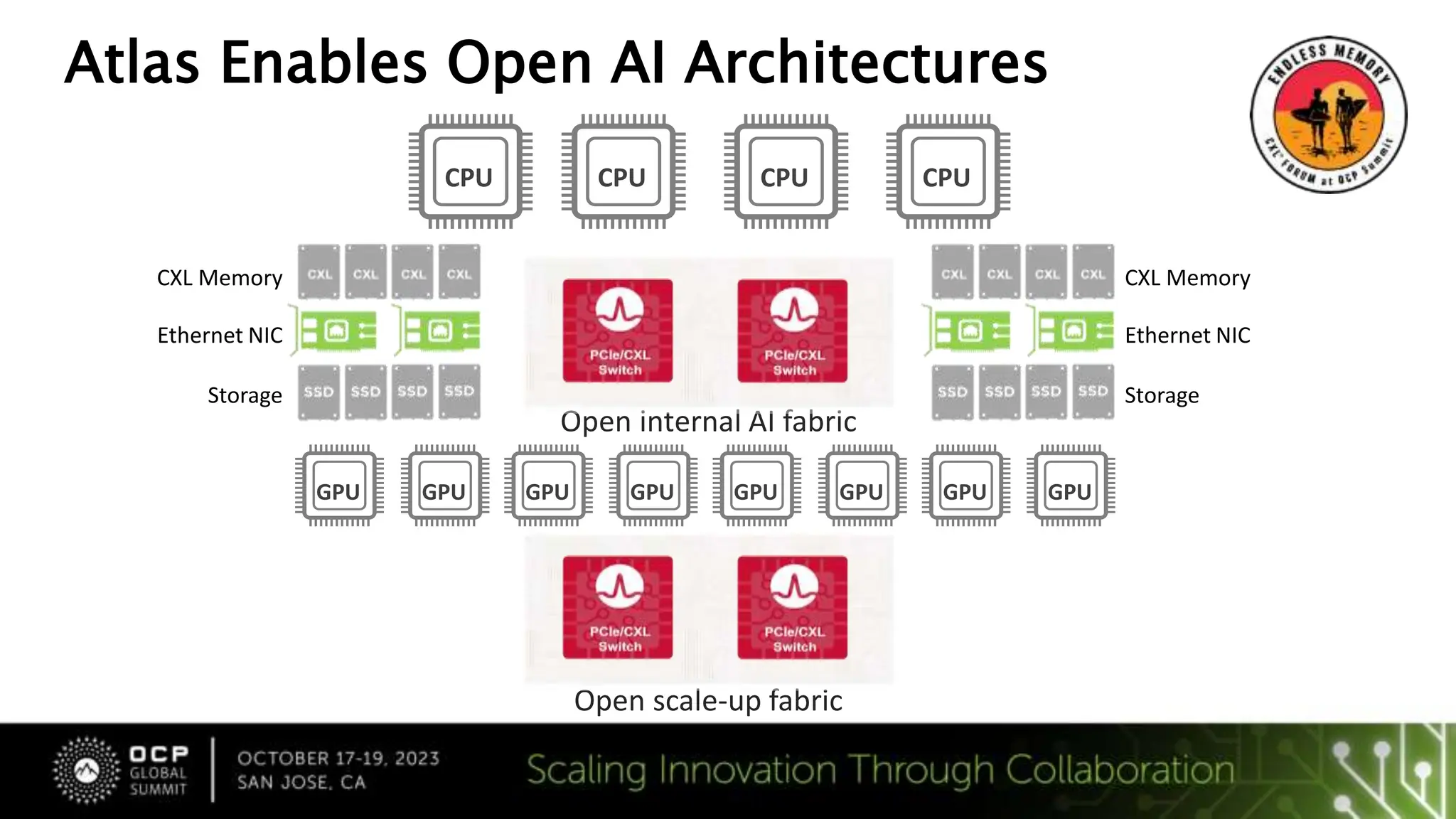

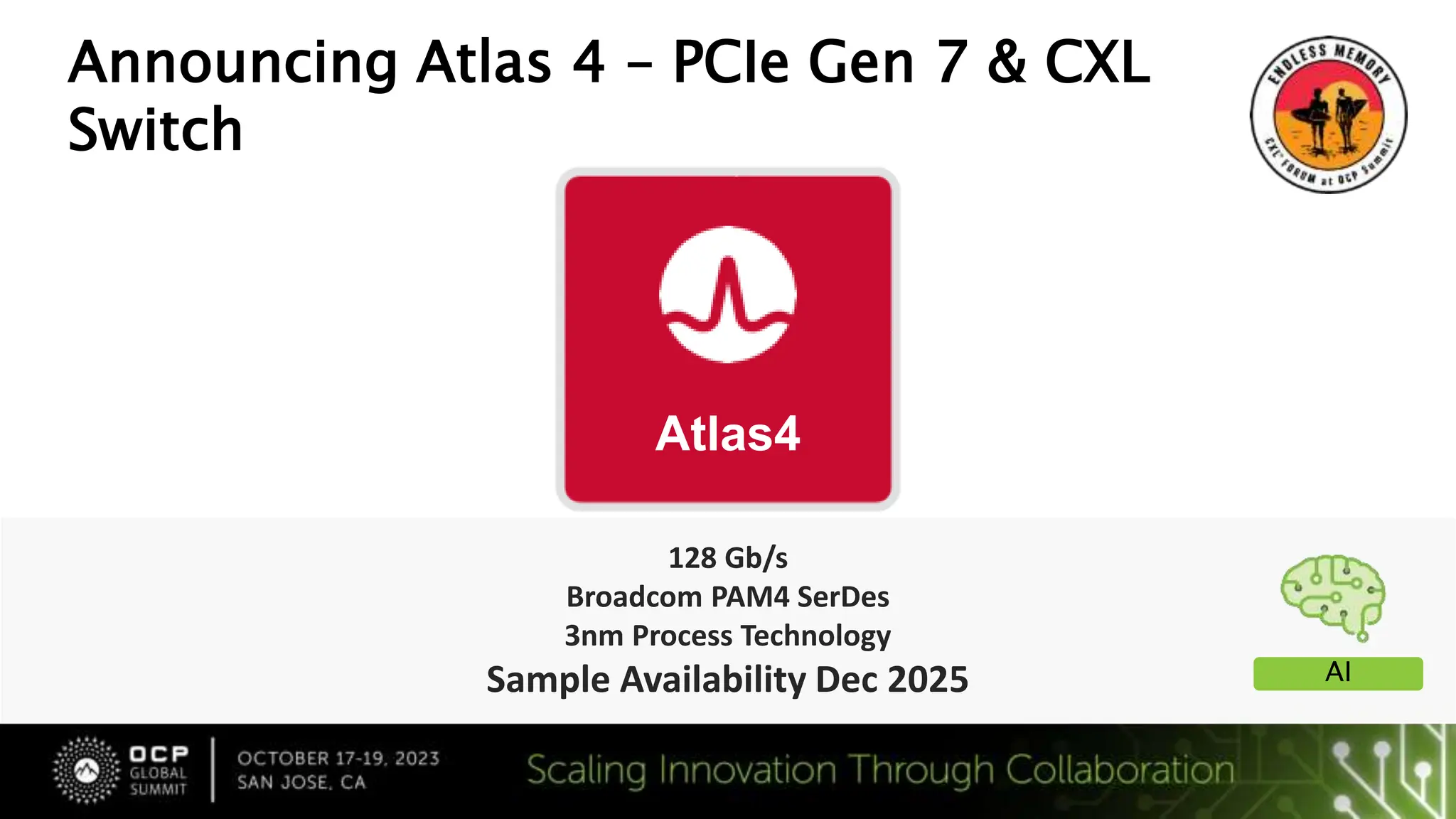

Broadcom has accelerated its PCIe/CXL roadmap, introducing the Atlas 3 and Atlas 4 platforms to enhance the open AI ecosystem with increased lane counts and bandwidth. The Atlas 3 platform features PCIe Gen 6 and CXL 3.1 support, enabling interoperability among ecosystem partners and allowing for complex AI architecture fabric configurations. Future advancements include Atlas 4 with PCIe Gen 7 capabilities, expected to provide significant performance enhancements by December 2025.