Report

Share

Download to read offline

Recommended

Recommended

More Related Content

What's hot

What's hot (20)

Embedded Systems (18EC62) - ARM Cortex-M3 Instruction Set and Programming (Mo...

Embedded Systems (18EC62) - ARM Cortex-M3 Instruction Set and Programming (Mo...

WSN network architecture -Sensor Network Scenarios & Transceiver Design Consi...

WSN network architecture -Sensor Network Scenarios & Transceiver Design Consi...

Similar to Bilbo 1

Similar to Bilbo 1 (20)

UNIT-II CPLD & FPGA Architectures and Applications

UNIT-II CPLD & FPGA Architectures and Applications

Design of a Digital Baseband Processor for UWB Transceiver on RFID Tag

Design of a Digital Baseband Processor for UWB Transceiver on RFID Tag

Lab ObjectivesThe objective for this lab is to review the Motoro.docx

Lab ObjectivesThe objective for this lab is to review the Motoro.docx

System Development for Verification of General Purpose Input Output

System Development for Verification of General Purpose Input Output

Implementation of CAN on FPGA for Security Evaluation Purpose

Implementation of CAN on FPGA for Security Evaluation Purpose

IRJET- UART Testing under Built-In-Self-Test(BIST) using Verilog on FPGA

IRJET- UART Testing under Built-In-Self-Test(BIST) using Verilog on FPGA

Recently uploaded

🔝9953056974🔝!!-YOUNG call girls in Rajendra Nagar Escort rvice Shot 2000 nigh...

🔝9953056974🔝!!-YOUNG call girls in Rajendra Nagar Escort rvice Shot 2000 nigh...9953056974 Low Rate Call Girls In Saket, Delhi NCR

College Call Girls Nashik Nehal 7001305949 Independent Escort Service Nashik

College Call Girls Nashik Nehal 7001305949 Independent Escort Service NashikCall Girls in Nagpur High Profile

Recently uploaded (20)

VIP Call Girls Service Kondapur Hyderabad Call +91-8250192130

VIP Call Girls Service Kondapur Hyderabad Call +91-8250192130

Call Girls Delhi {Jodhpur} 9711199012 high profile service

Call Girls Delhi {Jodhpur} 9711199012 high profile service

🔝9953056974🔝!!-YOUNG call girls in Rajendra Nagar Escort rvice Shot 2000 nigh...

🔝9953056974🔝!!-YOUNG call girls in Rajendra Nagar Escort rvice Shot 2000 nigh...

Heart Disease Prediction using machine learning.pptx

Heart Disease Prediction using machine learning.pptx

Biology for Computer Engineers Course Handout.pptx

Biology for Computer Engineers Course Handout.pptx

VIP Call Girls Service Hitech City Hyderabad Call +91-8250192130

VIP Call Girls Service Hitech City Hyderabad Call +91-8250192130

CCS355 Neural Network & Deep Learning Unit II Notes with Question bank .pdf

CCS355 Neural Network & Deep Learning Unit II Notes with Question bank .pdf

High Profile Call Girls Nagpur Isha Call 7001035870 Meet With Nagpur Escorts

High Profile Call Girls Nagpur Isha Call 7001035870 Meet With Nagpur Escorts

Exploring_Network_Security_with_JA3_by_Rakesh Seal.pptx

Exploring_Network_Security_with_JA3_by_Rakesh Seal.pptx

College Call Girls Nashik Nehal 7001305949 Independent Escort Service Nashik

College Call Girls Nashik Nehal 7001305949 Independent Escort Service Nashik

Gurgaon ✡️9711147426✨Call In girls Gurgaon Sector 51 escort service

Gurgaon ✡️9711147426✨Call In girls Gurgaon Sector 51 escort service

Bilbo 1

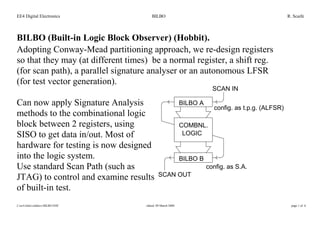

- 1. EE4 Digital Electronics BILBO R. Scaife I:ee4slidesolddocsBILBO.DOC edited: 09 March 2000 page 1 of 6 BILBO (Built-in Logic Block Observer) (Hobbit). Adopting Conway-Mead partitioning approach, we re-design registers so that they may (at different times) be a normal register, a shift reg. (for scan path), a parallel signature analyser or an autonomous LFSR (for test vector generation). Can now apply Signature Analysis methods to the combinational logic block between 2 registers, using SISO to get data in/out. Most of hardware for testing is now designed into the logic system. Use standard Scan Path (such as JTAG) to control and examine results of built-in test. BILBO A BILBO B COMBNL. LOGIC config. as t.p.g. (ALFSR) config. as S.A. SCAN IN SCAN OUT COMBNL. LOGIC

- 2. EE4 Digital Electronics BILBO R. Scaife I:ee4slidesolddocsBILBO.DOC edited: 09 March 2000 page 2 of 6 Full BILBO Register: Z1 Q /Q D Q Z2 Q /Q D Q Z Q /Q D QN ZN-1 Q /Q D QN-1 /SO 0 1 SI B1 B2

- 3. EE4 Digital Electronics BILBO R. Scaife I:ee4slidesolddocsBILBO.DOC edited: 09 March 2000 page 3 of 6 Normal Register Operation (B1= B2 =1): Acts as normal register. Z1 Q /Q D Q1 Z2 Q /Q D Q2 ZNZN-1 Q /Q D QN-1 Q /Q D QN

- 4. EE4 Digital Electronics BILBO R. Scaife I:ee4slidesolddocsBILBO.DOC edited: 09 March 2000 page 4 of 6 Shift Register (Scan) Mode (B1= B2 =0): Used either to drive {Qi} to particular values or read {Qi}, via serial scan-path. Q /Q D Q1 Q /Q D QN-1 Q /Q D Q2 Q /Q DSI SO QN

- 5. EE4 Digital Electronics BILBO R. Scaife I:ee4slidesolddocsBILBO.DOC edited: 09 March 2000 page 5 of 6 Autonomous LFSR (ALFSR) Mode (B1= 1, B2= 0): Used to Generate Test Sequences. Q /Q D Q /Q D Q /Q D Q /Q D QNQN-1Q1 Q2

- 6. EE4 Digital Electronics BILBO R. Scaife I:ee4slidesolddocsBILBO.DOC edited: 09 March 2000 page 6 of 6 Multiple-Input Shift Register (MISR) mode (B1= 1, B2= 0): Used in Signature Analyser mode to process output of combinational logic block in response to signals generated by BILBO in ALFSR mode. Z1 Z2 Q ZN /Q D Q1 Q ZN-1 /Q D QN-1 Q /Q D Q1 Q /Q D Q2