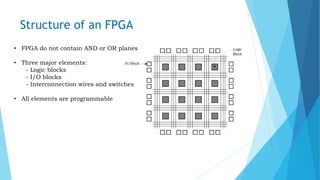

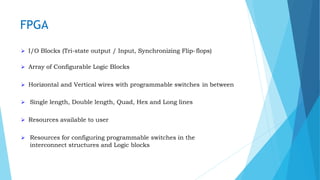

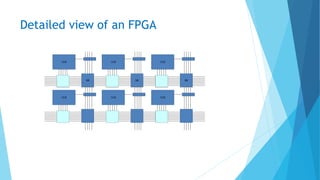

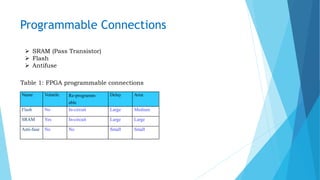

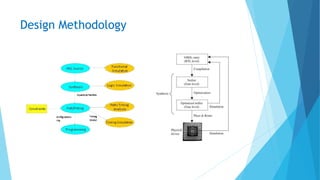

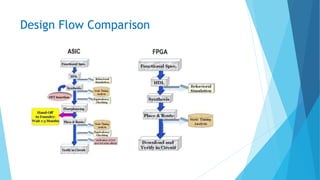

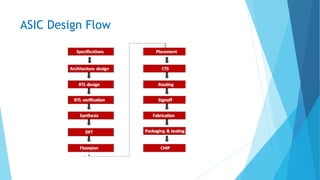

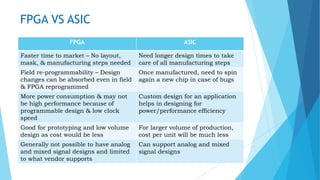

This document compares ASICs and FPGAs, highlighting that FPGAs are programmable integrated circuits that can be reconfigured post-deployment, while ASICs are custom-designed for specific applications. It details types of FPGAs, their structure, programming methods, and major manufacturers, such as Xilinx and Altera. Additionally, it discusses the advantages of ASICs over FPGAs, including cost and power savings, while noting the faster time to market and reprogrammability of FPGAs.