A generalized algorithm and reconfigurable

•Download as DOCX, PDF•

0 likes•85 views

VLSI Projects for M. Tech, VLSI Projects in Vijayanagar, VLSI Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, VLSI IEEE projects in Bangalore, IEEE 2015 VLSI Projects, FPGA and Xilinx Projects, FPGA and Xilinx Projects in Bangalore, FPGA and Xilinx Projects in Vijayangar

Report

Share

Report

Share

Recommended

A generalized algorithm and reconfigurable architecture for efficient and sca...

I3E Technologies,

#23/A, 2nd Floor SKS Complex,

Opp. Bus Stand, Karur-639 001.

IEEE PROJECTS AVAILABLE,

NON-IEEE PROJECTS AVAILABLE,

APPLICATION BASED PROJECTS AVAILABLE,

MINI-PROJECTS AVAILABLE.

Mobile : 99436 99916, 99436 99926, 99436 99936

Mail ID: i3eprojectskarur@gmail.com

Web: www.i3etechnologies.com, www.i3eprojects.com

Improved 8 point approximate dct for image and video compression requiring on...

Improved 8 point approximate dct for image and video compression requiring on...LogicMindtech Nologies

VLSI Projects for M. Tech, VLSI Projects in Vijayanagar, VLSI Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, VLSI IEEE projects in Bangalore, IEEE 2015 VLSI Projects, FPGA and Xilinx Projects, FPGA and Xilinx Projects in Bangalore, FPGA and Xilinx Projects in VijayangarNovel reconfigurable hardware architecture for polynomial matrix multiplications

I3E Technologies,

#23/A, 2nd Floor SKS Complex,

Opp. Bus Stand, Karur-639 001.

IEEE PROJECTS AVAILABLE,

NON-IEEE PROJECTS AVAILABLE,

APPLICATION BASED PROJECTS AVAILABLE,

MINI-PROJECTS AVAILABLE.

Mobile : 99436 99916, 99436 99926, 99436 99936

Mail ID: i3eprojectskarur@gmail.com

Web: www.i3etechnologies.com, www.i3eprojects.com

Fpga implementation of truncated multiplier for array multiplication

VLSI Projects in Bangalore

9611582234, 9945657526

International Journal of Engineering Research and Development

Electrical, Electronics and Computer Engineering,

Information Engineering and Technology,

Mechanical, Industrial and Manufacturing Engineering,

Automation and Mechatronics Engineering,

Material and Chemical Engineering,

Civil and Architecture Engineering,

Biotechnology and Bio Engineering,

Environmental Engineering,

Petroleum and Mining Engineering,

Marine and Agriculture engineering,

Aerospace Engineering.

Compact dfa scalable pattern matching using longest prefix match solutions

Ecruitment Solutions (ECS) is one of the leading Delhi based Software Development & HR Consulting Firm, which is assessed at the level of ISO 9001:2008 standard. ECS offers an awesome project and product based solutions to many customers around the globe.

In addition, ECS has also widened its wings by the way consummating academic projects especially for the final year professional degree students in India. ECS consist of a technical team that has solved many IEEE papers and delivered world-class solutions .

The implementation of the improved omp for aic reconstruction based on parall...

Sparse signal recovery becomes extremely challenging for a variety of real-time applications. In this paper, we improve the orthogonal matching pursuit (OMP) algorithm based on parallel correlation indices selection mechanism in each iteration and Goldschmidt algorithm. Simulation results show that the improved OMP algorithm with a reduced number of iterations and low hardware complexity of matrix operations has higher success rate and recovery signal-to-noise-ratio (RSNR) for sparse signal recovery. This paper presents an efficient complex valued system hardware architecture of the recovery algorithm for analog-to-information structure based on compressive sensing. The proposed architecture is implemented and validated on the Xilinx Virtex6 field-programmable gate array (FPGA) for signal reconstruction with N = 1024, K = 36, and M = 256. The implementation results showed that the improved OMP algorithm achieved a higher RSNR of 31.04 dB compared with the original OMP algorithm. This synthesized design consumes a few percentages of the hardware resources of the FPGA chip with the clock frequency of 135.4 MHZ and reconstruction time of 170 µs, which is faster than the existing design.

Recommended

A generalized algorithm and reconfigurable architecture for efficient and sca...

I3E Technologies,

#23/A, 2nd Floor SKS Complex,

Opp. Bus Stand, Karur-639 001.

IEEE PROJECTS AVAILABLE,

NON-IEEE PROJECTS AVAILABLE,

APPLICATION BASED PROJECTS AVAILABLE,

MINI-PROJECTS AVAILABLE.

Mobile : 99436 99916, 99436 99926, 99436 99936

Mail ID: i3eprojectskarur@gmail.com

Web: www.i3etechnologies.com, www.i3eprojects.com

Improved 8 point approximate dct for image and video compression requiring on...

Improved 8 point approximate dct for image and video compression requiring on...LogicMindtech Nologies

VLSI Projects for M. Tech, VLSI Projects in Vijayanagar, VLSI Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, VLSI IEEE projects in Bangalore, IEEE 2015 VLSI Projects, FPGA and Xilinx Projects, FPGA and Xilinx Projects in Bangalore, FPGA and Xilinx Projects in VijayangarNovel reconfigurable hardware architecture for polynomial matrix multiplications

I3E Technologies,

#23/A, 2nd Floor SKS Complex,

Opp. Bus Stand, Karur-639 001.

IEEE PROJECTS AVAILABLE,

NON-IEEE PROJECTS AVAILABLE,

APPLICATION BASED PROJECTS AVAILABLE,

MINI-PROJECTS AVAILABLE.

Mobile : 99436 99916, 99436 99926, 99436 99936

Mail ID: i3eprojectskarur@gmail.com

Web: www.i3etechnologies.com, www.i3eprojects.com

Fpga implementation of truncated multiplier for array multiplication

VLSI Projects in Bangalore

9611582234, 9945657526

International Journal of Engineering Research and Development

Electrical, Electronics and Computer Engineering,

Information Engineering and Technology,

Mechanical, Industrial and Manufacturing Engineering,

Automation and Mechatronics Engineering,

Material and Chemical Engineering,

Civil and Architecture Engineering,

Biotechnology and Bio Engineering,

Environmental Engineering,

Petroleum and Mining Engineering,

Marine and Agriculture engineering,

Aerospace Engineering.

Compact dfa scalable pattern matching using longest prefix match solutions

Ecruitment Solutions (ECS) is one of the leading Delhi based Software Development & HR Consulting Firm, which is assessed at the level of ISO 9001:2008 standard. ECS offers an awesome project and product based solutions to many customers around the globe.

In addition, ECS has also widened its wings by the way consummating academic projects especially for the final year professional degree students in India. ECS consist of a technical team that has solved many IEEE papers and delivered world-class solutions .

The implementation of the improved omp for aic reconstruction based on parall...

Sparse signal recovery becomes extremely challenging for a variety of real-time applications. In this paper, we improve the orthogonal matching pursuit (OMP) algorithm based on parallel correlation indices selection mechanism in each iteration and Goldschmidt algorithm. Simulation results show that the improved OMP algorithm with a reduced number of iterations and low hardware complexity of matrix operations has higher success rate and recovery signal-to-noise-ratio (RSNR) for sparse signal recovery. This paper presents an efficient complex valued system hardware architecture of the recovery algorithm for analog-to-information structure based on compressive sensing. The proposed architecture is implemented and validated on the Xilinx Virtex6 field-programmable gate array (FPGA) for signal reconstruction with N = 1024, K = 36, and M = 256. The implementation results showed that the improved OMP algorithm achieved a higher RSNR of 31.04 dB compared with the original OMP algorithm. This synthesized design consumes a few percentages of the hardware resources of the FPGA chip with the clock frequency of 135.4 MHZ and reconstruction time of 170 µs, which is faster than the existing design.

An area efficient relaxed half-stochastic decoding architecture for nonbinary...

An area efficient relaxed half-stochastic decoding architecture for nonbinary...LogicMindtech Nologies

VLSI Projects for M. Tech, VLSI Projects in Vijayanagar, VLSI Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, VLSI IEEE projects in Bangalore, IEEE 2015 VLSI Projects, FPGA and Xilinx Projects, FPGA and Xilinx Projects in Bangalore, FPGA and Xilinx Projects in VijayangarDESIGN OF DELAY COMPUTATION METHOD FOR CYCLOTOMIC FAST FOURIER TRANSFORM

In this paper the Delay Computation method for Common Sub expression Elimination algorithm is being implemented on Cyclotomic Fast Fourier Transform. The Common Sub Expression Elimination algorithm is combined with the delay computing method and is known as Gate Level Delay Computation with Common Sub expression Elimination Algorithm. Common sub expression elimination is effective

optimization method used to reduce adders in cyclotomic Fourier transform. The delay computing method is based on delay matrix and suitable for implementation with computers. The Gate level delay computation method is used to find critical path delay and it is analyzed on various finite field elements. The presented algorithm is established through a case study in Cyclotomic Fast Fourier Transform over finite field. If Cyclotomic Fast Fourier Transform is implemented directly then the system will have high additive complexities. So by using GLDC-CSE algorithm on cyclotomic fast Fourier transform, the additive

complexities will be reduced and also the area and area delay product will be reduced.

High throughput finite field multipliers using redundant basis for fpga and a...

High throughput finite field multipliers using redundant basis for fpga and a...LogicMindtech Nologies

VLSI Projects for M. Tech, VLSI Projects in Vijayanagar, VLSI Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, VLSI IEEE projects in Bangalore, IEEE 2015 VLSI Projects, FPGA and Xilinx Projects, FPGA and Xilinx Projects in Bangalore, FPGA and Xilinx Projects in VijayangarA High-Speed FPGA Implementation of an RSD-Based ECC Processor

A High-Speed FPGA Implementation of an RSD-Based ECC Processor

Image Processing IEEE 2015 Projects

List of Image Processing IEEE 2015 Projects. It Contains the IEEE Projects in the Domain Image Processing for the year 2015

A novel area efficient vlsi architecture

VLSI Projects for M. Tech, VLSI Projects in Vijayanagar, VLSI Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, VLSI IEEE projects in Bangalore, IEEE 2015 VLSI Projects, FPGA and Xilinx Projects, FPGA and Xilinx Projects in Bangalore, FPGA and Xilinx Projects in Vijayangar

Result biased distributed-arithmetic-based

VLSI Projects for M. Tech, VLSI Projects in Vijayanagar, VLSI Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, VLSI IEEE projects in Bangalore, IEEE 2015 VLSI Projects, FPGA and Xilinx Projects, FPGA and Xilinx Projects in Bangalore, FPGA and Xilinx Projects in Vijayangar

4 - Simulation and analysis of different DCT techniques on MATLAB (presented ...

Simulation and analysis of different DCT techniques on MATLAB (presented in a Malaysian conference)

Fpga based efficient multiplier for image processing applications using recur...

The Digital Image processing applications like medical imaging, satellite imaging, Biometric trait images

etc., rely on multipliers to improve the quality of image. However, existing multiplication techniques

introduce errors in the output with consumption of more time, hence error free high speed multipliers has

to be designed. In this paper we propose FPGA based Recursive Error Free Mitchell Log Multiplier

(REFMLM) for image Filters. The 2x2 error free Mitchell log multiplier is designed with zero error by

introducing error correction term is used in higher order Karastuba-Ofman Multiplier (KOM)

Architectures. The higher order KOM multipliers is decomposed into number of lower order multipliers

using radix 2 till basic multiplier block of order 2x2 which is designed by error free Mitchell log multiplier.

The 8x8 REFMLM is tested for Gaussian filter to remove noise in fingerprint image. The Multiplier is

synthesized using Spartan 3 FPGA family device XC3S1500-5fg320. It is observed that the performance

parameters such as area utilization, speed, error and PSNR are better in the case of proposed architecture

compared to existing architectures.

Integrating research and e learning in advance computer architecture

Integrating research and e learning in advance computer architecture slide help you to get computer Architecture concepts

Mini Project on 4 BIT SERIAL MULTIPLIER

A mini project based on 4 BIT SERIAL MULTIPLIER along with Verilog Code and Output

Area–delay–power efficient carry select adder

VLSI Projects for M. Tech, VLSI Projects in Vijayanagar, VLSI Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, VLSI IEEE projects in Bangalore, IEEE 2015 VLSI Projects, FPGA and Xilinx Projects, FPGA and Xilinx Projects in Bangalore, FPGA and Xilinx Projects in Vijayangar

Accumulo and the Convergence of Machine Learning, Big Data, and Supercomputing

Machine learning, big data, and simulation challenges have led to a proliferation of computing hardware and software solutions. Hyperscale data centers, accelerators, and programmable logic can deliver enormous performance via a wide range of analytic environments and data storage technologies. Apache Accumulo is a unique technology with the potential to enable all of these fields. Effectively exploiting Accumulo in these fields requires mathematically rigorous interfaces that allow users to focus on their domains. Mathematically rigorous interfaces are at the core MIT Lincoln Laboratory Supercomputing Center (LLSC) and enable the LLSC to deliver Apache Accumulo o thousands of scientists and engineers. This talk discusses the rapidly evolving computing landscape and how mathematically rigorous interfaces are the key to exploiting Apache Accumulo's advanced capabilities.

– Speaker –

Jeremy Kepner

Fellow, MIT

Dr. Jeremy Kepner is a MIT Lincoln Laboratory Fellow. He founded the Lincoln Laboratory Supercomputing Center and pioneered the establishment of the Massachusetts Green High Performance Computing Center. He has developed novel big data and parallel computing software used by thousands of scientists and engineers worldwide. He has led several embedded computing efforts, which earned him a 2011 R&D 100 Award. Dr. Kepner has chaired SIAM Data Mining, the IEEE Big Data conference, and the IEEE High Performance Extreme Computing conference. Dr. Kepner is the author of two bestselling books, Parallel MATLAB and Graph Algorithms in the Language of Linear Algebra. His peer-reviewed publications include works on abstract algebra, astronomy, cloud computing, cybersecurity, data mining, databases, graph algorithms, health sciences, signal processing, and visualization. Dr. Kepner holds a BA degree in astrophysics from Pomona College and a PhD degree in astrophysics from Princeton University.

— More Information —

For more information see http://www.accumulosummit.com/

IMPLEMENTATION OF EFFICIENT ADDER USING MULTI VALUE LOGIC TECHNIQUE

The digital logic circuits are restricted for the requirement of interconnections. This difficulty overcomes by using a big set of signals over the same chip area. Multiple-valued logic (MVL) designs contain more importance from that perspective. This paper gives the fabrication of a multiple-valued half adder and full adder circuits. This technique advantageous for large scale circuits due to which large power dissipation with increased speed can lead to the development of extremely low energy circuit’s use for the high performance required for number of applications. Multiple-valued logic (MVL) designs are gaining more advantageous from the design of a multiple-valued half adder and full adder circuits. The presented adders are design in Multiple-Valued voltage-Mode Logic (MV-VML). In quaternary half adder, quaternary logic levels are exploited for the intention of addition. Addition operation is executed with minimum number of gates and less depth of net. The design is targeted for the 0.18 μm CMOS technology. Circuit is design by using Advanced Design System software {ADS software}. In this paper we try to find area, power and speed of the design HAq / FAq without any need of conversion, and compare to existing binary circuits [HAb / FAb].

IRJET- FPGA Implementation of Low Power Configurable Adder for Approximate Co...

https://www.irjet.net/archives/V6/i3/IRJET-V6I3773.pdf

Improved 8 point approximate dct for image and video compression requiring on...

Improved 8 point approximate dct for image and video compression requiring on...LogicMindtech Nologies

VLSI Projects for M. Tech, VLSI Projects in Vijayanagar, VLSI Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, VLSI IEEE projects in Bangalore, IEEE 2015 VLSI Projects, FPGA and Xilinx Projects, FPGA and Xilinx Projects in Bangalore, FPGA and Xilinx Projects in VijayangarA LIGHT WEIGHT VLSI FRAME WORK FOR HIGHT CIPHER ON FPGA

https://www.irjet.net/archives/V10/i2/IRJET-V10I260.pdf

A new method for self-organized dynamic delay loop associated pipeline with ...

The minimization of propagation delay between pipeline stages is very important in wave propagation through pipeline-stages. The propagation delay can be minimized by minimizing the number of stages in a pipeline. In the proposed design a dynamic stage control is imparted in the pipeline. The propagation delay can be optimized in any type of pipeline by controlling number of stages dynamically. The pipeline interpretation helps a lot to overcome the flaws due to not ready sequence (NRS) and synchronization problems. It is observed that, in the pipeline design the basic and actively involved pipeline techniques are concerned with different challenges like clock, throughput, cell area, and sizes. As the data throughput increases the number of stages in pipeline also needs to be increased to meet the desired goal. In the case of unpredictable data speed, the definite number of pipeline stages creates severe problems. In this work a dynamic pipeline is integrated where the number of stages is dynamically changing depending up on data speed. In dynamic pipeline technique the circuit cell area of reconfigurable computing system (RCS) will be reduced dynamically at low-speed data transmission. In the high-speed data communication, the data speed is managed and controlled by dynamic delay loops.

More Related Content

What's hot

An area efficient relaxed half-stochastic decoding architecture for nonbinary...

An area efficient relaxed half-stochastic decoding architecture for nonbinary...LogicMindtech Nologies

VLSI Projects for M. Tech, VLSI Projects in Vijayanagar, VLSI Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, VLSI IEEE projects in Bangalore, IEEE 2015 VLSI Projects, FPGA and Xilinx Projects, FPGA and Xilinx Projects in Bangalore, FPGA and Xilinx Projects in VijayangarDESIGN OF DELAY COMPUTATION METHOD FOR CYCLOTOMIC FAST FOURIER TRANSFORM

In this paper the Delay Computation method for Common Sub expression Elimination algorithm is being implemented on Cyclotomic Fast Fourier Transform. The Common Sub Expression Elimination algorithm is combined with the delay computing method and is known as Gate Level Delay Computation with Common Sub expression Elimination Algorithm. Common sub expression elimination is effective

optimization method used to reduce adders in cyclotomic Fourier transform. The delay computing method is based on delay matrix and suitable for implementation with computers. The Gate level delay computation method is used to find critical path delay and it is analyzed on various finite field elements. The presented algorithm is established through a case study in Cyclotomic Fast Fourier Transform over finite field. If Cyclotomic Fast Fourier Transform is implemented directly then the system will have high additive complexities. So by using GLDC-CSE algorithm on cyclotomic fast Fourier transform, the additive

complexities will be reduced and also the area and area delay product will be reduced.

High throughput finite field multipliers using redundant basis for fpga and a...

High throughput finite field multipliers using redundant basis for fpga and a...LogicMindtech Nologies

VLSI Projects for M. Tech, VLSI Projects in Vijayanagar, VLSI Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, VLSI IEEE projects in Bangalore, IEEE 2015 VLSI Projects, FPGA and Xilinx Projects, FPGA and Xilinx Projects in Bangalore, FPGA and Xilinx Projects in VijayangarA High-Speed FPGA Implementation of an RSD-Based ECC Processor

A High-Speed FPGA Implementation of an RSD-Based ECC Processor

Image Processing IEEE 2015 Projects

List of Image Processing IEEE 2015 Projects. It Contains the IEEE Projects in the Domain Image Processing for the year 2015

A novel area efficient vlsi architecture

VLSI Projects for M. Tech, VLSI Projects in Vijayanagar, VLSI Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, VLSI IEEE projects in Bangalore, IEEE 2015 VLSI Projects, FPGA and Xilinx Projects, FPGA and Xilinx Projects in Bangalore, FPGA and Xilinx Projects in Vijayangar

Result biased distributed-arithmetic-based

VLSI Projects for M. Tech, VLSI Projects in Vijayanagar, VLSI Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, VLSI IEEE projects in Bangalore, IEEE 2015 VLSI Projects, FPGA and Xilinx Projects, FPGA and Xilinx Projects in Bangalore, FPGA and Xilinx Projects in Vijayangar

4 - Simulation and analysis of different DCT techniques on MATLAB (presented ...

Simulation and analysis of different DCT techniques on MATLAB (presented in a Malaysian conference)

Fpga based efficient multiplier for image processing applications using recur...

The Digital Image processing applications like medical imaging, satellite imaging, Biometric trait images

etc., rely on multipliers to improve the quality of image. However, existing multiplication techniques

introduce errors in the output with consumption of more time, hence error free high speed multipliers has

to be designed. In this paper we propose FPGA based Recursive Error Free Mitchell Log Multiplier

(REFMLM) for image Filters. The 2x2 error free Mitchell log multiplier is designed with zero error by

introducing error correction term is used in higher order Karastuba-Ofman Multiplier (KOM)

Architectures. The higher order KOM multipliers is decomposed into number of lower order multipliers

using radix 2 till basic multiplier block of order 2x2 which is designed by error free Mitchell log multiplier.

The 8x8 REFMLM is tested for Gaussian filter to remove noise in fingerprint image. The Multiplier is

synthesized using Spartan 3 FPGA family device XC3S1500-5fg320. It is observed that the performance

parameters such as area utilization, speed, error and PSNR are better in the case of proposed architecture

compared to existing architectures.

Integrating research and e learning in advance computer architecture

Integrating research and e learning in advance computer architecture slide help you to get computer Architecture concepts

Mini Project on 4 BIT SERIAL MULTIPLIER

A mini project based on 4 BIT SERIAL MULTIPLIER along with Verilog Code and Output

Area–delay–power efficient carry select adder

VLSI Projects for M. Tech, VLSI Projects in Vijayanagar, VLSI Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, VLSI IEEE projects in Bangalore, IEEE 2015 VLSI Projects, FPGA and Xilinx Projects, FPGA and Xilinx Projects in Bangalore, FPGA and Xilinx Projects in Vijayangar

Accumulo and the Convergence of Machine Learning, Big Data, and Supercomputing

Machine learning, big data, and simulation challenges have led to a proliferation of computing hardware and software solutions. Hyperscale data centers, accelerators, and programmable logic can deliver enormous performance via a wide range of analytic environments and data storage technologies. Apache Accumulo is a unique technology with the potential to enable all of these fields. Effectively exploiting Accumulo in these fields requires mathematically rigorous interfaces that allow users to focus on their domains. Mathematically rigorous interfaces are at the core MIT Lincoln Laboratory Supercomputing Center (LLSC) and enable the LLSC to deliver Apache Accumulo o thousands of scientists and engineers. This talk discusses the rapidly evolving computing landscape and how mathematically rigorous interfaces are the key to exploiting Apache Accumulo's advanced capabilities.

– Speaker –

Jeremy Kepner

Fellow, MIT

Dr. Jeremy Kepner is a MIT Lincoln Laboratory Fellow. He founded the Lincoln Laboratory Supercomputing Center and pioneered the establishment of the Massachusetts Green High Performance Computing Center. He has developed novel big data and parallel computing software used by thousands of scientists and engineers worldwide. He has led several embedded computing efforts, which earned him a 2011 R&D 100 Award. Dr. Kepner has chaired SIAM Data Mining, the IEEE Big Data conference, and the IEEE High Performance Extreme Computing conference. Dr. Kepner is the author of two bestselling books, Parallel MATLAB and Graph Algorithms in the Language of Linear Algebra. His peer-reviewed publications include works on abstract algebra, astronomy, cloud computing, cybersecurity, data mining, databases, graph algorithms, health sciences, signal processing, and visualization. Dr. Kepner holds a BA degree in astrophysics from Pomona College and a PhD degree in astrophysics from Princeton University.

— More Information —

For more information see http://www.accumulosummit.com/

IMPLEMENTATION OF EFFICIENT ADDER USING MULTI VALUE LOGIC TECHNIQUE

The digital logic circuits are restricted for the requirement of interconnections. This difficulty overcomes by using a big set of signals over the same chip area. Multiple-valued logic (MVL) designs contain more importance from that perspective. This paper gives the fabrication of a multiple-valued half adder and full adder circuits. This technique advantageous for large scale circuits due to which large power dissipation with increased speed can lead to the development of extremely low energy circuit’s use for the high performance required for number of applications. Multiple-valued logic (MVL) designs are gaining more advantageous from the design of a multiple-valued half adder and full adder circuits. The presented adders are design in Multiple-Valued voltage-Mode Logic (MV-VML). In quaternary half adder, quaternary logic levels are exploited for the intention of addition. Addition operation is executed with minimum number of gates and less depth of net. The design is targeted for the 0.18 μm CMOS technology. Circuit is design by using Advanced Design System software {ADS software}. In this paper we try to find area, power and speed of the design HAq / FAq without any need of conversion, and compare to existing binary circuits [HAb / FAb].

IRJET- FPGA Implementation of Low Power Configurable Adder for Approximate Co...

https://www.irjet.net/archives/V6/i3/IRJET-V6I3773.pdf

What's hot (18)

An area efficient relaxed half-stochastic decoding architecture for nonbinary...

An area efficient relaxed half-stochastic decoding architecture for nonbinary...

DESIGN OF DELAY COMPUTATION METHOD FOR CYCLOTOMIC FAST FOURIER TRANSFORM

DESIGN OF DELAY COMPUTATION METHOD FOR CYCLOTOMIC FAST FOURIER TRANSFORM

High throughput finite field multipliers using redundant basis for fpga and a...

High throughput finite field multipliers using redundant basis for fpga and a...

A High-Speed FPGA Implementation of an RSD-Based ECC Processor

A High-Speed FPGA Implementation of an RSD-Based ECC Processor

4 - Simulation and analysis of different DCT techniques on MATLAB (presented ...

4 - Simulation and analysis of different DCT techniques on MATLAB (presented ...

Fpga based efficient multiplier for image processing applications using recur...

Fpga based efficient multiplier for image processing applications using recur...

Integrating research and e learning in advance computer architecture

Integrating research and e learning in advance computer architecture

Accumulo and the Convergence of Machine Learning, Big Data, and Supercomputing

Accumulo and the Convergence of Machine Learning, Big Data, and Supercomputing

IMPLEMENTATION OF EFFICIENT ADDER USING MULTI VALUE LOGIC TECHNIQUE

IMPLEMENTATION OF EFFICIENT ADDER USING MULTI VALUE LOGIC TECHNIQUE

IRJET- FPGA Implementation of Low Power Configurable Adder for Approximate Co...

IRJET- FPGA Implementation of Low Power Configurable Adder for Approximate Co...

A tutorial on CGAL polyhedron for subdivision algorithms

A tutorial on CGAL polyhedron for subdivision algorithms

Similar to A generalized algorithm and reconfigurable

Improved 8 point approximate dct for image and video compression requiring on...

Improved 8 point approximate dct for image and video compression requiring on...LogicMindtech Nologies

VLSI Projects for M. Tech, VLSI Projects in Vijayanagar, VLSI Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, VLSI IEEE projects in Bangalore, IEEE 2015 VLSI Projects, FPGA and Xilinx Projects, FPGA and Xilinx Projects in Bangalore, FPGA and Xilinx Projects in VijayangarA LIGHT WEIGHT VLSI FRAME WORK FOR HIGHT CIPHER ON FPGA

https://www.irjet.net/archives/V10/i2/IRJET-V10I260.pdf

A new method for self-organized dynamic delay loop associated pipeline with ...

The minimization of propagation delay between pipeline stages is very important in wave propagation through pipeline-stages. The propagation delay can be minimized by minimizing the number of stages in a pipeline. In the proposed design a dynamic stage control is imparted in the pipeline. The propagation delay can be optimized in any type of pipeline by controlling number of stages dynamically. The pipeline interpretation helps a lot to overcome the flaws due to not ready sequence (NRS) and synchronization problems. It is observed that, in the pipeline design the basic and actively involved pipeline techniques are concerned with different challenges like clock, throughput, cell area, and sizes. As the data throughput increases the number of stages in pipeline also needs to be increased to meet the desired goal. In the case of unpredictable data speed, the definite number of pipeline stages creates severe problems. In this work a dynamic pipeline is integrated where the number of stages is dynamically changing depending up on data speed. In dynamic pipeline technique the circuit cell area of reconfigurable computing system (RCS) will be reduced dynamically at low-speed data transmission. In the high-speed data communication, the data speed is managed and controlled by dynamic delay loops.

Edal an energy efficient, delay-aware, and lifetime-balancing data collection...

Edal an energy efficient, delay-aware, and lifetime-balancing data collection...LogicMindtech Nologies

NS2 Projects for M. Tech, NS2 Projects in Vijayanagar, NS2 Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, NS2 IEEE projects in Bangalore, IEEE 2015 NS2 Projects, WSN and MANET Projects, WSN and MANET Projects in Bangalore, WSN and MANET Projects in VijayangarEFFICIENT ABSOLUTE DIFFERENCE CIRCUIT FOR SAD COMPUTATION ON FPGA

Video Compression is very essential to meet the technological demands such as low power, less memory

and fast transfer rate for different range of devices and for various multimedia applications. Video

compression is primarily achieved by Motion Estimation (ME) process in any video encoder which

contributes to significant compression gain.Sum of Absolute Difference (SAD) is used as distortion metric

in ME process.In this paper, efficient Absolute Difference(AD)circuit is proposed which uses Brent Kung

Adder(BKA) and a comparator based on modified 1’s complement principle and conditional sum adder

scheme. Results shows that proposed architecture reduces delay by 15% and number of slice LUTs by 42

% as compared to conventional architecture. Simulation and synthesis are done on Xilinx ISE 14.2 using

Virtex 7 FPGA.

EFFICIENT ABSOLUTE DIFFERENCE CIRCUIT FOR SAD COMPUTATION ON FPGA

Video Compression is very essential to meet the technological demands such as low power, less memory and fast transfer rate for different range of devices and for various multimedia applications. Video compression is primarily achieved by Motion Estimation (ME) process in any video encoder which contributes to significant compression gain.Sum of Absolute Difference (SAD) is used as distortion metric in ME process.In this paper, efficient Absolute Difference(AD)circuit is proposed which uses Brent Kung Adder(BKA) and a comparator based on modified 1’s complement principle and conditional sum adder scheme. Results shows that proposed architecture reduces delay by 15% and number of slice LUTs by 42 % as compared to conventional architecture. Simulation and synthesis are done on Xilinx ISE 14.2 using Virtex 7 FPGA.

Reconfigurable CORDIC Low-Power Implementation of Complex Signal Processing f...

In recent years, CORDIC algorithms has been used extensively for various image processing

system& biomedical applications. By using CORDIC algorithm we can able to reducing the number of

iteration to process the image in the system. Low power design is to be challenging process during system

operations. Previous approaches scope to minimize the power consumption without image quality

consideration. In this paper CORDIC Based Low Power DCT iterations process equally based upon their

image quality. An hardware implementation of ROM & control logic circuit to require large hardware

space in this system. Look-ahead CORDIC Approach is used to finish the iteration at one time. When

reducing hardware area & reducing number of iterations for maximize battery lifetime. This idea used to

achieve the low power design of image and video compression application

EFFICIENT ABSOLUTE DIFFERENCE CIRCUIT FOR SAD COMPUTATION ON FPGA

Video Compression is very essential to meet the technological demands such as low power, less memory and fast transfer rate for different range of devices and for various multimedia applications. Video compression is primarily achieved by Motion Estimation (ME) process in any video encoder which contributes to significant compression gain.Sum of Absolute Difference (SAD) is used as distortion metric in ME process.In this paper, efficient Absolute Difference(AD)circuit is proposed which uses Brent Kung Adder(BKA) and a comparator based on modified 1’s complement principle and conditional sum adder scheme. Results shows that proposed architecture reduces delay by 15% and number of slice LUTs by 42% as compared to conventional architecture. Simulation and synthesis are done on Xilinx ISE 14.2 using Virtex 7 FPGA.

IRJET- The RTL Model of a Reconfigurable Pipelined MCM

https://www.irjet.net/archives/V6/i5/IRJET-V6I5123.pdf

IRJET- A Review- FPGA based Architectures for Image Capturing Consequently Pr...

https://irjet.net/archives/V7/i1/IRJET-V7I1288.pdf

International Journal of Computational Engineering Research(IJCER)

International Journal of Computational Engineering Research(IJCER) is an intentional online Journal in English monthly publishing journal. This Journal publish original research work that contributes significantly to further the scientific knowledge in engineering and Technology.

HARDWARE SOFTWARE CO-SIMULATION OF MOTION ESTIMATION IN H.264 ENCODER

This paper proposes about motion estimation in H.264/AVC encoder. Compared with standards

such as MPEG-2 and MPEG-4 Visual, H.264 can deliver better image quality at the same

compressed bit rate or at a lower bit rate. The increase in compression efficiency comes at the

expense of increase in complexity, which is a fact that must be overcome. An efficient Co-design

methodology is required, where the encoder software application is highly optimized and

structured in a very modular and efficient manner, so as to allow its most complex and time

consuming operations to be offloaded to dedicated hardware accelerators. The Motion

Estimation algorithm is the most computationally intensive part of the encoder which is simulated using MATLAB. The hardware/software co-simulation is done using system generator tool and implemented using Xilinx FPGA Spartan 3E for different scanning methods.

Design and Performance Analysis of 8 x 8 Network on Chip Router

https://www.irjet.net/archives/V9/i6/IRJET-V9I676.pdf

2017 18 ieee vlsi titles,IEEE 2017-18 BULK NS2 PROJECTS TITLES,IEEE 2017-18...

NEXGEN TECHNOLOGY as an efficient Software Training Center located at Pondicherry with IT Training on IEEE Projects in Android,IEEE IT B.Tech Student Projects, Android Projects Training with Placements Pondicherry, IEEE projects in pondicherry, final IEEE Projects in Pondicherry , MCA, BTech, BCA Projects in Pondicherry, Bulk IEEE PROJECTS IN Pondicherry.So far we have reached almost all engineering colleges located in Pondicherry and around 90km

Nexgen Technology Address:

Nexgen Technology

No :66,4th cross,Venkata nagar,

Near SBI ATM,

Puducherry.

Email Id: praveen@nexgenproject.com.

www.nexgenproject.com

Mobile: 9791938249

Telephone: 0413-2211159.

LOGIC OPTIMIZATION USING TECHNOLOGY INDEPENDENT MUX BASED ADDERS IN FPGA

Adders form an almost obligatory component of every contemporary integrated circuit. The prerequisite of the adder is that it is primarily fast and secondarily efficient in terms of power consumption and chip area. Therefore, careful optimization of the adder is of the greatest importance. This optimization can be attained

in two levels; it can be circuit or logic optimization. In circuit optimization the size of transistors are manipulated, where as in logic optimization the Boolean equations are rearranged (or manipulated) to optimize speed, area and power consumption. This paper focuses the optimization of adder through technology independent mapping. The work presents 20 different logical construction of 1-bit adder cell in CMOS logic and its performance is analyzed in terms of transistor count, delay and power dissipation. These performance issues are analyzed through Tanner EDA with TSMC MOSIS 250nm technology. From this analysis the optimized equation is chosen to construct a full adder circuit in terms of multiplexer. This logic optimized multiplexer based adders are incorporated in selected existing adders like ripple carry

adder, carry look-ahead adder, carry skip adder, carry select adder, carry increment adder and carry save adder and its performance is analyzed in terms of area (slices used) and maximum combinational path delay as a function of size. The target FPGA device chosen for the implementation of these adders was Xilinx ISE 12.1 Spartan3E XC3S500-5FG320. Each adder type was implemented with bit sizes of: 8, 16, 32, 64 bits. This variety of sizes will provide with more insight about the performance of each adder in terms of area and delay as a function of size.

COMEDI: Combinatorial Election of Diagnostic Vectors From Detection Test Sets...

COMEDI: Combinatorial Election of Diagnostic Vectors From Detection Test Sets...JAYAPRAKASH JPINFOTECH

COMEDI: Combinatorial Election of Diagnostic Vectors From Detection Test Sets for Logic CircuitsEnergy efficient wireless sensor networks using linear programming optimizati...

Energy efficient wireless sensor networks using linear programming optimizati...LogicMindtech Nologies

NS2 Projects for M. Tech, NS2 Projects in Vijayanagar, NS2 Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, NS2 IEEE projects in Bangalore, IEEE 2015 NS2 Projects, WSN and MANET Projects, WSN and MANET Projects in Bangalore, WSN and MANET Projects in VijayangarcuTau Leaping

Brief Explanation about the Tau-Leaping Process, Parallel Processing and NVIDIA's CUDA architecture

And the use of cuTau - Leaping for simulation of Biological systems

Similar to A generalized algorithm and reconfigurable (20)

Improved 8 point approximate dct for image and video compression requiring on...

Improved 8 point approximate dct for image and video compression requiring on...

A LIGHT WEIGHT VLSI FRAME WORK FOR HIGHT CIPHER ON FPGA

A LIGHT WEIGHT VLSI FRAME WORK FOR HIGHT CIPHER ON FPGA

Vlsi 2015 2016 ieee project list-(v)_with abstract

Vlsi 2015 2016 ieee project list-(v)_with abstract

A new method for self-organized dynamic delay loop associated pipeline with ...

A new method for self-organized dynamic delay loop associated pipeline with ...

Edal an energy efficient, delay-aware, and lifetime-balancing data collection...

Edal an energy efficient, delay-aware, and lifetime-balancing data collection...

EFFICIENT ABSOLUTE DIFFERENCE CIRCUIT FOR SAD COMPUTATION ON FPGA

EFFICIENT ABSOLUTE DIFFERENCE CIRCUIT FOR SAD COMPUTATION ON FPGA

EFFICIENT ABSOLUTE DIFFERENCE CIRCUIT FOR SAD COMPUTATION ON FPGA

EFFICIENT ABSOLUTE DIFFERENCE CIRCUIT FOR SAD COMPUTATION ON FPGA

Reconfigurable CORDIC Low-Power Implementation of Complex Signal Processing f...

Reconfigurable CORDIC Low-Power Implementation of Complex Signal Processing f...

EFFICIENT ABSOLUTE DIFFERENCE CIRCUIT FOR SAD COMPUTATION ON FPGA

EFFICIENT ABSOLUTE DIFFERENCE CIRCUIT FOR SAD COMPUTATION ON FPGA

IRJET- The RTL Model of a Reconfigurable Pipelined MCM

IRJET- The RTL Model of a Reconfigurable Pipelined MCM

IRJET- A Review- FPGA based Architectures for Image Capturing Consequently Pr...

IRJET- A Review- FPGA based Architectures for Image Capturing Consequently Pr...

International Journal of Computational Engineering Research(IJCER)

International Journal of Computational Engineering Research(IJCER)

HARDWARE SOFTWARE CO-SIMULATION OF MOTION ESTIMATION IN H.264 ENCODER

HARDWARE SOFTWARE CO-SIMULATION OF MOTION ESTIMATION IN H.264 ENCODER

Design and Performance Analysis of 8 x 8 Network on Chip Router

Design and Performance Analysis of 8 x 8 Network on Chip Router

2017 18 ieee vlsi titles,IEEE 2017-18 BULK NS2 PROJECTS TITLES,IEEE 2017-18...

2017 18 ieee vlsi titles,IEEE 2017-18 BULK NS2 PROJECTS TITLES,IEEE 2017-18...

LOGIC OPTIMIZATION USING TECHNOLOGY INDEPENDENT MUX BASED ADDERS IN FPGA

LOGIC OPTIMIZATION USING TECHNOLOGY INDEPENDENT MUX BASED ADDERS IN FPGA

COMEDI: Combinatorial Election of Diagnostic Vectors From Detection Test Sets...

COMEDI: Combinatorial Election of Diagnostic Vectors From Detection Test Sets...

Energy efficient wireless sensor networks using linear programming optimizati...

Energy efficient wireless sensor networks using linear programming optimizati...

More from LogicMindtech Nologies

Utilizing image scales towards totally training free blind image quality asse...

Utilizing image scales towards totally training free blind image quality asse...LogicMindtech Nologies

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Thermal imaging as a biometrics approach to facial signature authentication

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Template ip

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Targeting accurate object extraction from an image a comprehensive study of ...

Targeting accurate object extraction from an image a comprehensive study of ...LogicMindtech Nologies

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Sparse dissimilarity constrained coding for glaucoma screening

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Sar sift a sift like algorithm for sar images

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Optic disc boundary and vessel origin

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

On criminalidentificationin color skin images usingskin marks (rppvsm) and fu...

On criminalidentificationin color skin images usingskin marks (rppvsm) and fu...LogicMindtech Nologies

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Multi scale two-directional two-dimensional

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Measuring calorie and nutrition from food image

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Lossless and reversible data hiding in encrypted images with public key crypt...

Lossless and reversible data hiding in encrypted images with public key crypt...LogicMindtech Nologies

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Joint super resolution and denoising from a single depth image

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Iterative vessel segmentation of fundus images

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Influence of color to gray conversion on the performance of document image bi...

Influence of color to gray conversion on the performance of document image bi...LogicMindtech Nologies

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Improving pixel based change detection accuracy using an object-based approac...

Improving pixel based change detection accuracy using an object-based approac...LogicMindtech Nologies

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Image quality assessment for fake biometric detection application to iris f...

Image quality assessment for fake biometric detection application to iris f...LogicMindtech Nologies

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Image forgery detection using adaptive over segmentation and feature point ma...

Image forgery detection using adaptive over segmentation and feature point ma...LogicMindtech Nologies

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Haze removal for a single remote sensing image based on deformed haze imaging...

Haze removal for a single remote sensing image based on deformed haze imaging...LogicMindtech Nologies

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Face recognition by exploiting local gabor

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

Enhancing color images of extremely low light scenes based on rgb nir images ...

Enhancing color images of extremely low light scenes based on rgb nir images ...LogicMindtech Nologies

IMAGE PROCESSING Projects for M. Tech, IMAGE PROCESSING Projects in Vijayanagar, IMAGE PROCESSING Projects in Bangalore, M. Tech Projects in Vijayanagar, M. Tech Projects in Bangalore, IMAGE PROCESSING IEEE projects in Bangalore, IEEE 2015 IMAGE PROCESSING Projects, MATLAB Image Processing Projects, MATLAB Image Processing Projects in Bangalore, MATLAB Image Processing Projects in Vijayangar

More from LogicMindtech Nologies (20)

Utilizing image scales towards totally training free blind image quality asse...

Utilizing image scales towards totally training free blind image quality asse...

Thermal imaging as a biometrics approach to facial signature authentication

Thermal imaging as a biometrics approach to facial signature authentication

Targeting accurate object extraction from an image a comprehensive study of ...

Targeting accurate object extraction from an image a comprehensive study of ...

Sparse dissimilarity constrained coding for glaucoma screening

Sparse dissimilarity constrained coding for glaucoma screening

On criminalidentificationin color skin images usingskin marks (rppvsm) and fu...

On criminalidentificationin color skin images usingskin marks (rppvsm) and fu...

Lossless and reversible data hiding in encrypted images with public key crypt...

Lossless and reversible data hiding in encrypted images with public key crypt...

Joint super resolution and denoising from a single depth image

Joint super resolution and denoising from a single depth image

Influence of color to gray conversion on the performance of document image bi...

Influence of color to gray conversion on the performance of document image bi...

Improving pixel based change detection accuracy using an object-based approac...

Improving pixel based change detection accuracy using an object-based approac...

Image quality assessment for fake biometric detection application to iris f...

Image quality assessment for fake biometric detection application to iris f...

Image forgery detection using adaptive over segmentation and feature point ma...

Image forgery detection using adaptive over segmentation and feature point ma...

Haze removal for a single remote sensing image based on deformed haze imaging...

Haze removal for a single remote sensing image based on deformed haze imaging...

Enhancing color images of extremely low light scenes based on rgb nir images ...

Enhancing color images of extremely low light scenes based on rgb nir images ...

Recently uploaded

Sachpazis:Terzaghi Bearing Capacity Estimation in simple terms with Calculati...

Terzaghi's soil bearing capacity theory, developed by Karl Terzaghi, is a fundamental principle in geotechnical engineering used to determine the bearing capacity of shallow foundations. This theory provides a method to calculate the ultimate bearing capacity of soil, which is the maximum load per unit area that the soil can support without undergoing shear failure. The Calculation HTML Code included.

CW RADAR, FMCW RADAR, FMCW ALTIMETER, AND THEIR PARAMETERS

It consists of cw radar and fmcw radar ,range measurement,if amplifier and fmcw altimeterThe CW radar operates using continuous wave transmission, while the FMCW radar employs frequency-modulated continuous wave technology. Range measurement is a crucial aspect of radar systems, providing information about the distance to a target. The IF amplifier plays a key role in signal processing, amplifying intermediate frequency signals for further analysis. The FMCW altimeter utilizes frequency-modulated continuous wave technology to accurately measure altitude above a reference point.

一比一原版(SFU毕业证)西蒙菲莎大学毕业证成绩单如何办理

SFU毕业证原版定制【微信:176555708】【西蒙菲莎大学毕业证成绩单-学位证】【微信:176555708】(留信学历认证永久存档查询)采用学校原版纸张、特殊工艺完全按照原版一比一制作(包括:隐形水印,阴影底纹,钢印LOGO烫金烫银,LOGO烫金烫银复合重叠,文字图案浮雕,激光镭射,紫外荧光,温感,复印防伪)行业标杆!精益求精,诚心合作,真诚制作!多年品质 ,按需精细制作,24小时接单,全套进口原装设备,十五年致力于帮助留学生解决难题,业务范围有加拿大、英国、澳洲、韩国、美国、新加坡,新西兰等学历材料,包您满意。

◆◆◆◆◆ — — — — — — — — 【留学教育】留学归国服务中心 — — — — — -◆◆◆◆◆

【主营项目】

一.毕业证【微信:176555708】成绩单、使馆认证、教育部认证、雅思托福成绩单、学生卡等!

二.真实使馆公证(即留学回国人员证明,不成功不收费)

三.真实教育部学历学位认证(教育部存档!教育部留服网站永久可查)

四.办理各国各大学文凭(一对一专业服务,可全程监控跟踪进度)

如果您处于以下几种情况:

◇在校期间,因各种原因未能顺利毕业……拿不到官方毕业证【微信:176555708】

◇面对父母的压力,希望尽快拿到;

◇不清楚认证流程以及材料该如何准备;

◇回国时间很长,忘记办理;

◇回国马上就要找工作,办给用人单位看;

◇企事业单位必须要求办理的

◇需要报考公务员、购买免税车、落转户口

◇申请留学生创业基金

留信网认证的作用:

1:该专业认证可证明留学生真实身份

2:同时对留学生所学专业登记给予评定

3:国家专业人才认证中心颁发入库证书

4:这个认证书并且可以归档倒地方

5:凡事获得留信网入网的信息将会逐步更新到个人身份内,将在公安局网内查询个人身份证信息后,同步读取人才网入库信息

6:个人职称评审加20分

7:个人信誉贷款加10分→ 【关于价格问题(保证一手价格)

我们所定的价格是非常合理的,而且我们现在做得单子大多数都是代理和回头客户介绍的所以一般现在有新的单子 我给客户的都是第一手的代理价格,因为我想坦诚对待大家 不想跟大家在价格方面浪费时间

对于老客户或者被老客户介绍过来的朋友,我们都会适当给一些优惠。

8:在国家人才网主办的国家网络招聘大会中纳入资料,供国家高端企业选择人才

选择实体注册公司办理,更放心,更安全!我们的承诺:可来公司面谈,可签订合同,会陪同客户一起到教育部认证窗口递交认证材料,客户在教育部官方认证查询网站查询到认证通过结果后付款,不成功不收费!

学历顾问:微信:176555708

Immunizing Image Classifiers Against Localized Adversary Attacks

This paper addresses the vulnerability of deep learning models, particularly convolutional neural networks

(CNN)s, to adversarial attacks and presents a proactive training technique designed to counter them. We

introduce a novel volumization algorithm, which transforms 2D images into 3D volumetric representations.

When combined with 3D convolution and deep curriculum learning optimization (CLO), itsignificantly improves

the immunity of models against localized universal attacks by up to 40%. We evaluate our proposed approach

using contemporary CNN architectures and the modified Canadian Institute for Advanced Research (CIFAR-10

and CIFAR-100) and ImageNet Large Scale Visual Recognition Challenge (ILSVRC12) datasets, showcasing

accuracy improvements over previous techniques. The results indicate that the combination of the volumetric

input and curriculum learning holds significant promise for mitigating adversarial attacks without necessitating

adversary training.

Industrial Training at Shahjalal Fertilizer Company Limited (SFCL)

This presentation is about the working procedure of Shahjalal Fertilizer Company Limited (SFCL). A Govt. owned Company of Bangladesh Chemical Industries Corporation under Ministry of Industries.

NUMERICAL SIMULATIONS OF HEAT AND MASS TRANSFER IN CONDENSING HEAT EXCHANGERS...

Power plants release a large amount of water vapor into the

atmosphere through the stack. The flue gas can be a potential

source for obtaining much needed cooling water for a power

plant. If a power plant could recover and reuse a portion of this

moisture, it could reduce its total cooling water intake

requirement. One of the most practical way to recover water

from flue gas is to use a condensing heat exchanger. The power

plant could also recover latent heat due to condensation as well

as sensible heat due to lowering the flue gas exit temperature.

Additionally, harmful acids released from the stack can be

reduced in a condensing heat exchanger by acid condensation. reduced in a condensing heat exchanger by acid condensation.

Condensation of vapors in flue gas is a complicated

phenomenon since heat and mass transfer of water vapor and

various acids simultaneously occur in the presence of noncondensable

gases such as nitrogen and oxygen. Design of a

condenser depends on the knowledge and understanding of the

heat and mass transfer processes. A computer program for

numerical simulations of water (H2O) and sulfuric acid (H2SO4)

condensation in a flue gas condensing heat exchanger was

developed using MATLAB. Governing equations based on

mass and energy balances for the system were derived to

predict variables such as flue gas exit temperature, cooling

water outlet temperature, mole fraction and condensation rates

of water and sulfuric acid vapors. The equations were solved

using an iterative solution technique with calculations of heat

and mass transfer coefficients and physical properties.

Water Industry Process Automation and Control Monthly - May 2024.pdf

Water Industry Process Automation and Control Monthly - May 2024.pdfWater Industry Process Automation & Control

Welcome to WIPAC Monthly the magazine brought to you by the LinkedIn Group Water Industry Process Automation & Control.

In this month's edition, along with this month's industry news to celebrate the 13 years since the group was created we have articles including

A case study of the used of Advanced Process Control at the Wastewater Treatment works at Lleida in Spain

A look back on an article on smart wastewater networks in order to see how the industry has measured up in the interim around the adoption of Digital Transformation in the Water Industry.Forklift Classes Overview by Intella Parts

Discover the different forklift classes and their specific applications. Learn how to choose the right forklift for your needs to ensure safety, efficiency, and compliance in your operations.

For more technical information, visit our website https://intellaparts.com

HYDROPOWER - Hydroelectric power generation

Overview of the fundamental roles in Hydropower generation and the components involved in wider Electrical Engineering.

This paper presents the design and construction of hydroelectric dams from the hydrologist’s survey of the valley before construction, all aspects and involved disciplines, fluid dynamics, structural engineering, generation and mains frequency regulation to the very transmission of power through the network in the United Kingdom.

Author: Robbie Edward Sayers

Collaborators and co editors: Charlie Sims and Connor Healey.

(C) 2024 Robbie E. Sayers

NO1 Uk best vashikaran specialist in delhi vashikaran baba near me online vas...

NO1 Uk best vashikaran specialist in delhi vashikaran baba near me online vas...Amil Baba Dawood bangali

Contact with Dawood Bhai Just call on +92322-6382012 and we'll help you. We'll solve all your problems within 12 to 24 hours and with 101% guarantee and with astrology systematic. If you want to take any personal or professional advice then also you can call us on +92322-6382012 , ONLINE LOVE PROBLEM & Other all types of Daily Life Problem's.Then CALL or WHATSAPP us on +92322-6382012 and Get all these problems solutions here by Amil Baba DAWOOD BANGALI

#vashikaranspecialist #astrologer #palmistry #amliyaat #taweez #manpasandshadi #horoscope #spiritual #lovelife #lovespell #marriagespell#aamilbabainpakistan #amilbabainkarachi #powerfullblackmagicspell #kalajadumantarspecialist #realamilbaba #AmilbabainPakistan #astrologerincanada #astrologerindubai #lovespellsmaster #kalajaduspecialist #lovespellsthatwork #aamilbabainlahore#blackmagicformarriage #aamilbaba #kalajadu #kalailam #taweez #wazifaexpert #jadumantar #vashikaranspecialist #astrologer #palmistry #amliyaat #taweez #manpasandshadi #horoscope #spiritual #lovelife #lovespell #marriagespell#aamilbabainpakistan #amilbabainkarachi #powerfullblackmagicspell #kalajadumantarspecialist #realamilbaba #AmilbabainPakistan #astrologerincanada #astrologerindubai #lovespellsmaster #kalajaduspecialist #lovespellsthatwork #aamilbabainlahore #blackmagicforlove #blackmagicformarriage #aamilbaba #kalajadu #kalailam #taweez #wazifaexpert #jadumantar #vashikaranspecialist #astrologer #palmistry #amliyaat #taweez #manpasandshadi #horoscope #spiritual #lovelife #lovespell #marriagespell#aamilbabainpakistan #amilbabainkarachi #powerfullblackmagicspell #kalajadumantarspecialist #realamilbaba #AmilbabainPakistan #astrologerincanada #astrologerindubai #lovespellsmaster #kalajaduspecialist #lovespellsthatwork #aamilbabainlahore #Amilbabainuk #amilbabainspain #amilbabaindubai #Amilbabainnorway #amilbabainkrachi #amilbabainlahore #amilbabaingujranwalan #amilbabainislamabad

Recently uploaded (20)

Sachpazis:Terzaghi Bearing Capacity Estimation in simple terms with Calculati...

Sachpazis:Terzaghi Bearing Capacity Estimation in simple terms with Calculati...

Pile Foundation by Venkatesh Taduvai (Sub Geotechnical Engineering II)-conver...

Pile Foundation by Venkatesh Taduvai (Sub Geotechnical Engineering II)-conver...

CW RADAR, FMCW RADAR, FMCW ALTIMETER, AND THEIR PARAMETERS

CW RADAR, FMCW RADAR, FMCW ALTIMETER, AND THEIR PARAMETERS

Immunizing Image Classifiers Against Localized Adversary Attacks

Immunizing Image Classifiers Against Localized Adversary Attacks

Industrial Training at Shahjalal Fertilizer Company Limited (SFCL)

Industrial Training at Shahjalal Fertilizer Company Limited (SFCL)

Fundamentals of Electric Drives and its applications.pptx

Fundamentals of Electric Drives and its applications.pptx

NUMERICAL SIMULATIONS OF HEAT AND MASS TRANSFER IN CONDENSING HEAT EXCHANGERS...

NUMERICAL SIMULATIONS OF HEAT AND MASS TRANSFER IN CONDENSING HEAT EXCHANGERS...

Water Industry Process Automation and Control Monthly - May 2024.pdf

Water Industry Process Automation and Control Monthly - May 2024.pdf

block diagram and signal flow graph representation

block diagram and signal flow graph representation

MCQ Soil mechanics questions (Soil shear strength).pdf

MCQ Soil mechanics questions (Soil shear strength).pdf

NO1 Uk best vashikaran specialist in delhi vashikaran baba near me online vas...

NO1 Uk best vashikaran specialist in delhi vashikaran baba near me online vas...

A generalized algorithm and reconfigurable

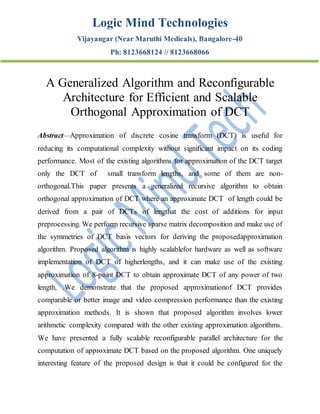

- 1. Logic Mind Technologies Vijayangar (Near Maruthi Medicals), Bangalore-40 Ph: 8123668124 // 8123668066 A Generalized Algorithm and Reconfigurable Architecture for Efficient and Scalable Orthogonal Approximation of DCT Abstract—Approximation of discrete cosine transform (DCT) is useful for reducing its computational complexity without significant impact on its coding performance. Most of the existing algorithms for approximation of the DCT target only the DCT of small transform lengths, and some of them are non- orthogonal.This paper presents a generalized recursive algorithm to obtain orthogonal approximation of DCT where an approximate DCT of length could be derived from a pair of DCTs of lengthat the cost of additions for input preprocessing. We perform recursive sparse matrix decomposition and make use of the symmetries of DCT basis vectors for deriving the proposedapproximation algorithm. Proposed algorithm is highly scalablefor hardware as well as software implementation of DCT of higherlengths, and it can make use of the existing approximation of 8-point DCT to obtain approximate DCT of any power of two length, .We demonstrate that the proposed approximationof DCT provides comparable or better image and video compression performance than the existing approximation methods. It is shown that proposed algorithm involves lower arithmetic complexity compared with the other existing approximation algorithms. We have presented a fully scalable reconfigurable parallel architecture for the computation of approximate DCT based on the proposed algorithm. One uniquely interesting feature of the proposed design is that it could be configured for the

- 2. computation of a 32-point DCT or for parallel computation of two 16-point DCTs or four 8-point DCTs with a marginal control overhead. The proposed architecture is found to offer many advantages in terms of hardware complexity, regularity and modularity. Experimental results obtained from FPGA implementation show the advantage of the proposed method. SOFTWARE REQUIREMENT: ModelSim6.4c. Xilinx 9.1/13.2. HARDWARE REQUIREMENT: FPGA Spartan 3. PROJECT FLOW: First Review: Literature Survey Paper Explanation Design of Project Project Enhancement explanation Second Review: Implementing 40% of Base Paper Third Review Implementing Remaining 60% of Base Paper with Future Enhancement (Modification) For More Details please contact Logic Mind Technologies Vijayangar (NearMaruthi Medicals), Bangalore-40 Ph: 8123668124 // 8123668066 Mail: logicmindtech@gmail.com