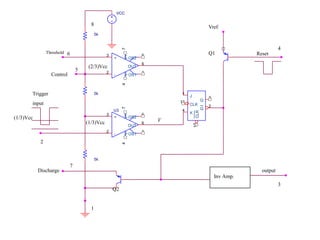

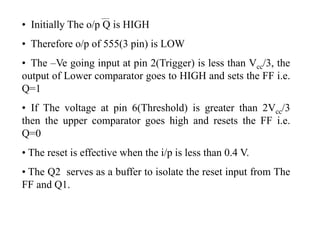

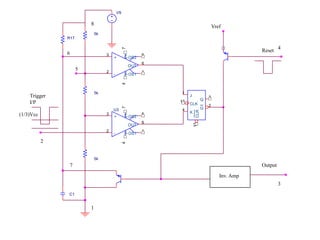

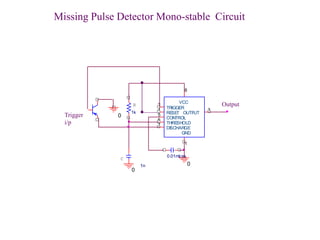

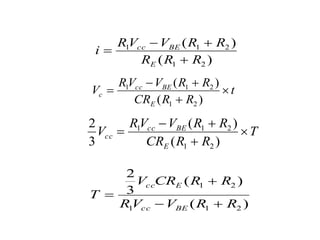

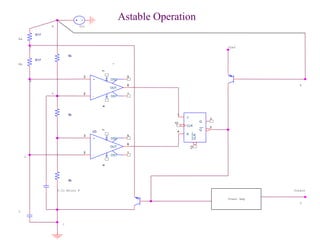

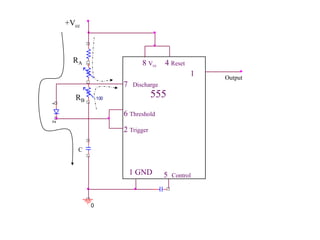

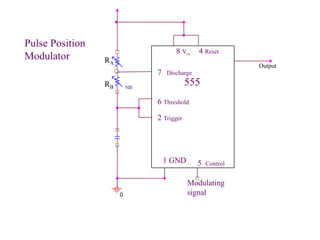

This circuit uses two 555 timers and an inverting amplifier to generate a pulse width modulated signal. The first 555 operates in monostable mode and is triggered by an input signal, causing its output to go high for a fixed period of time determined by an RC circuit. The second 555 and inverting amplifier together form an astable multivibrator that toggles the output between high and low at a frequency determined by its RC values. The output of the first 555 discharges the second 555's timing capacitor, modifying the output pulse width and creating the PWM signal.