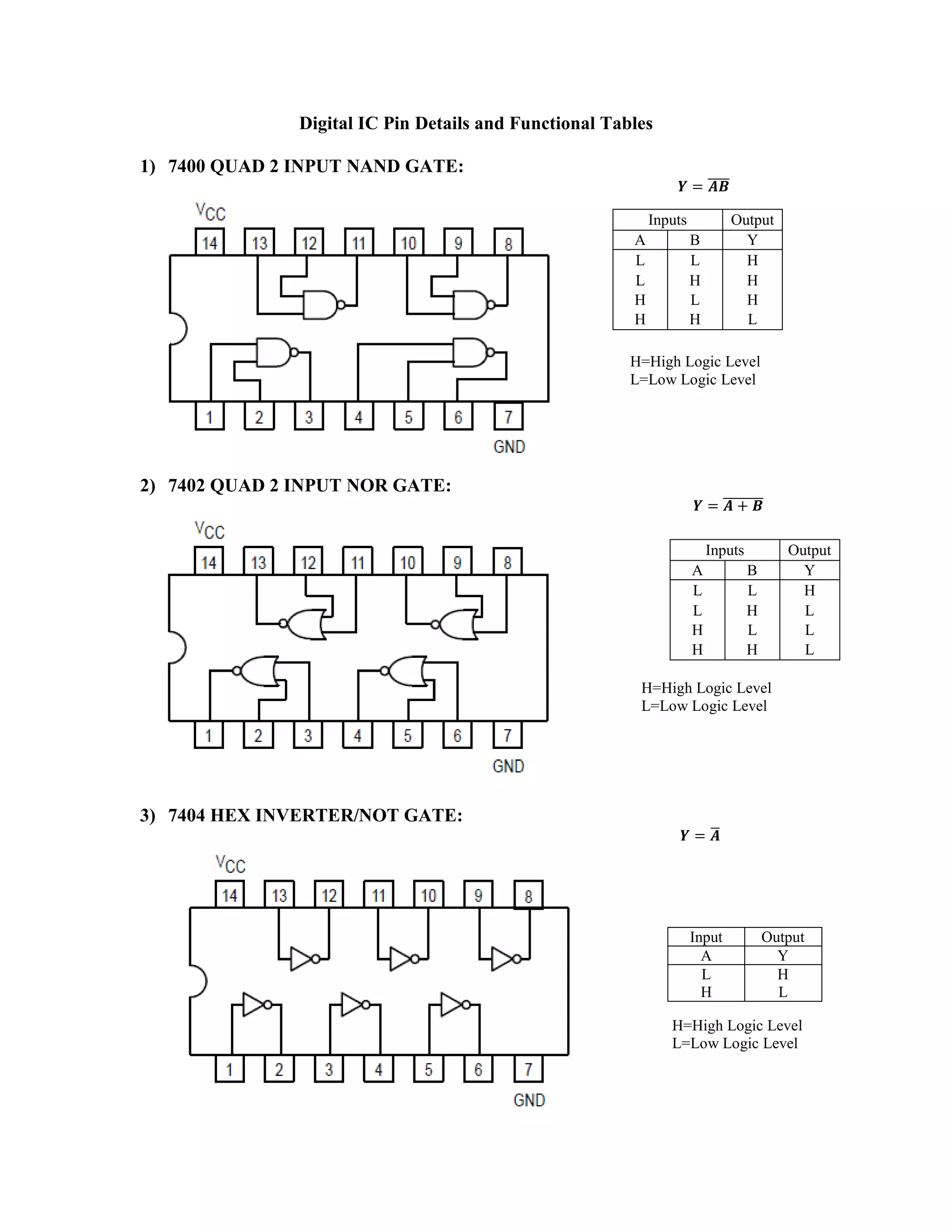

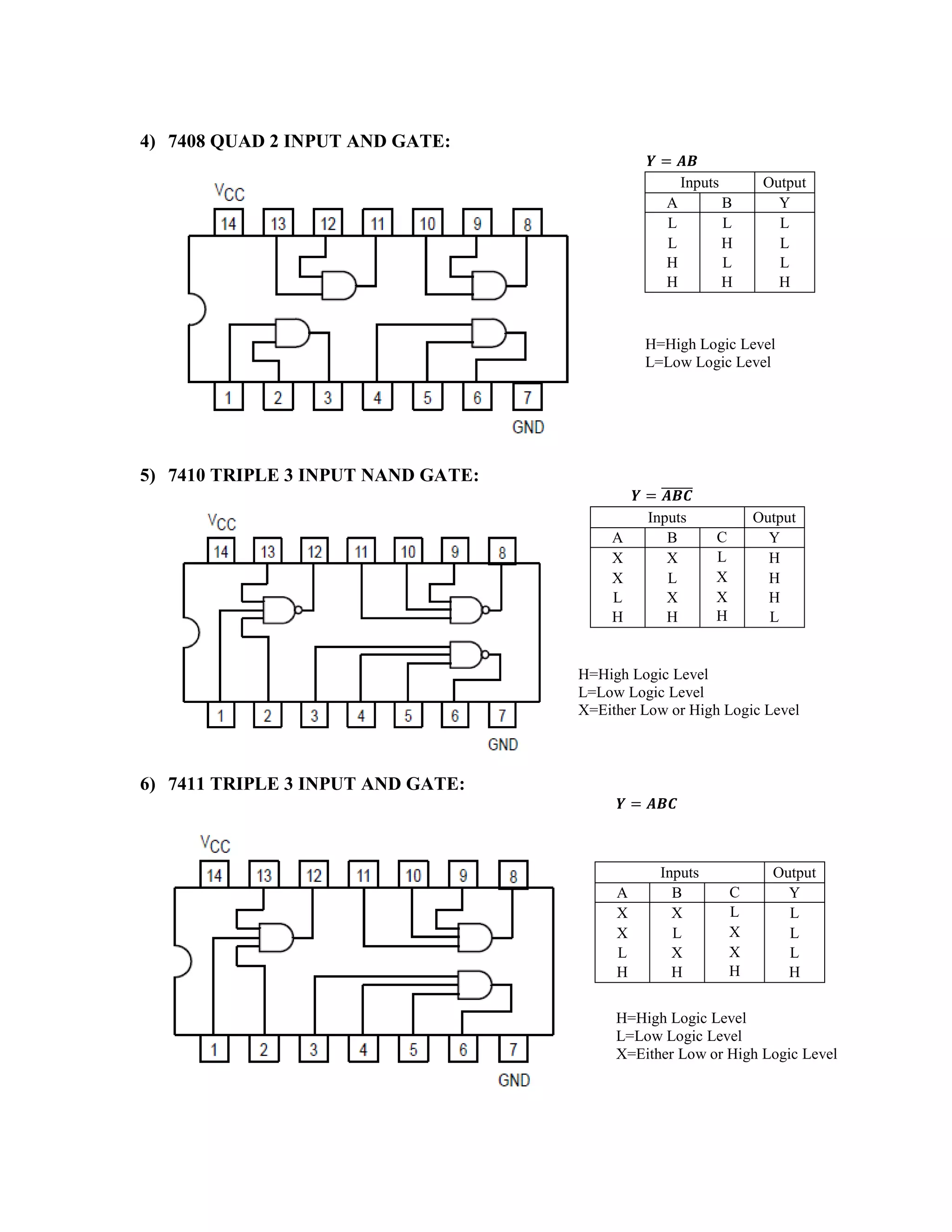

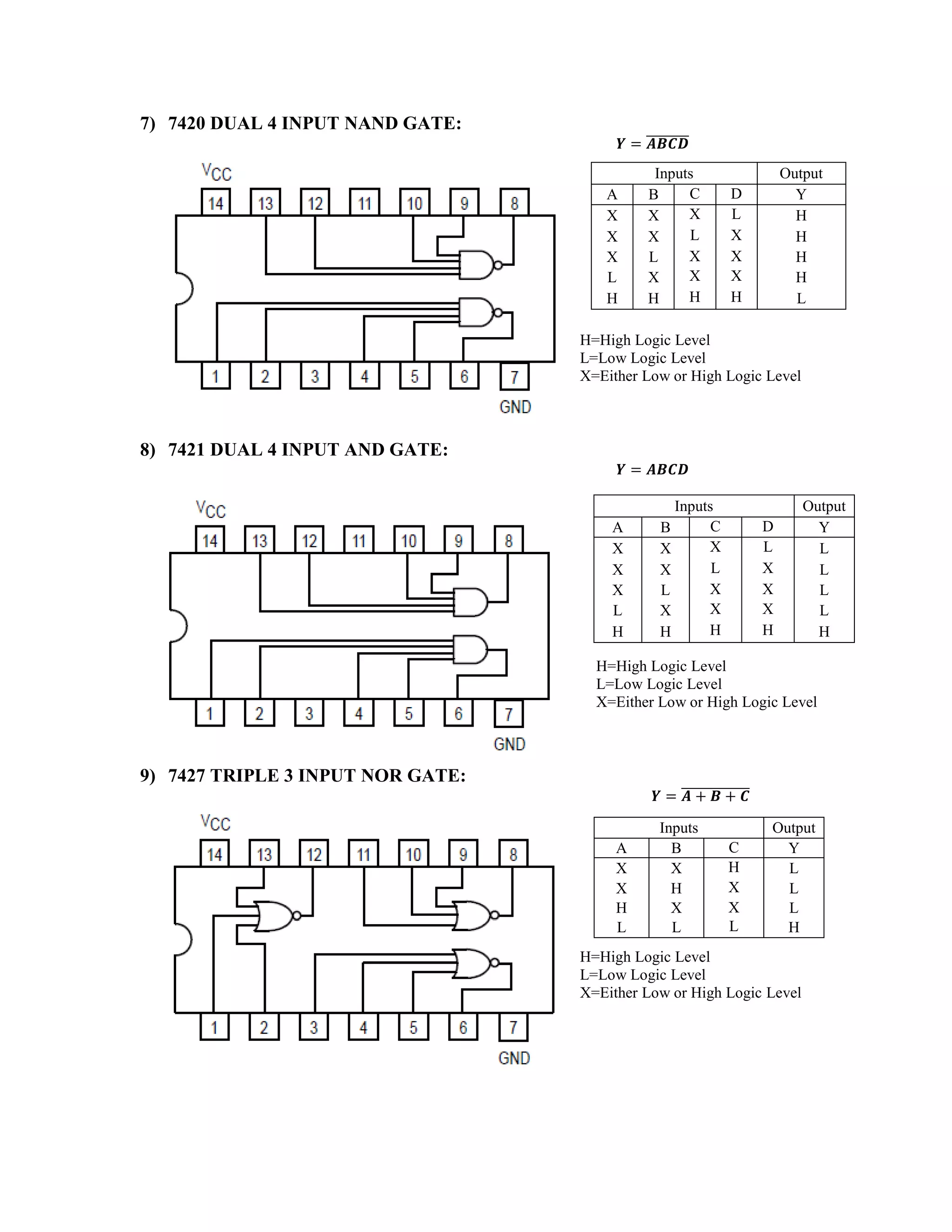

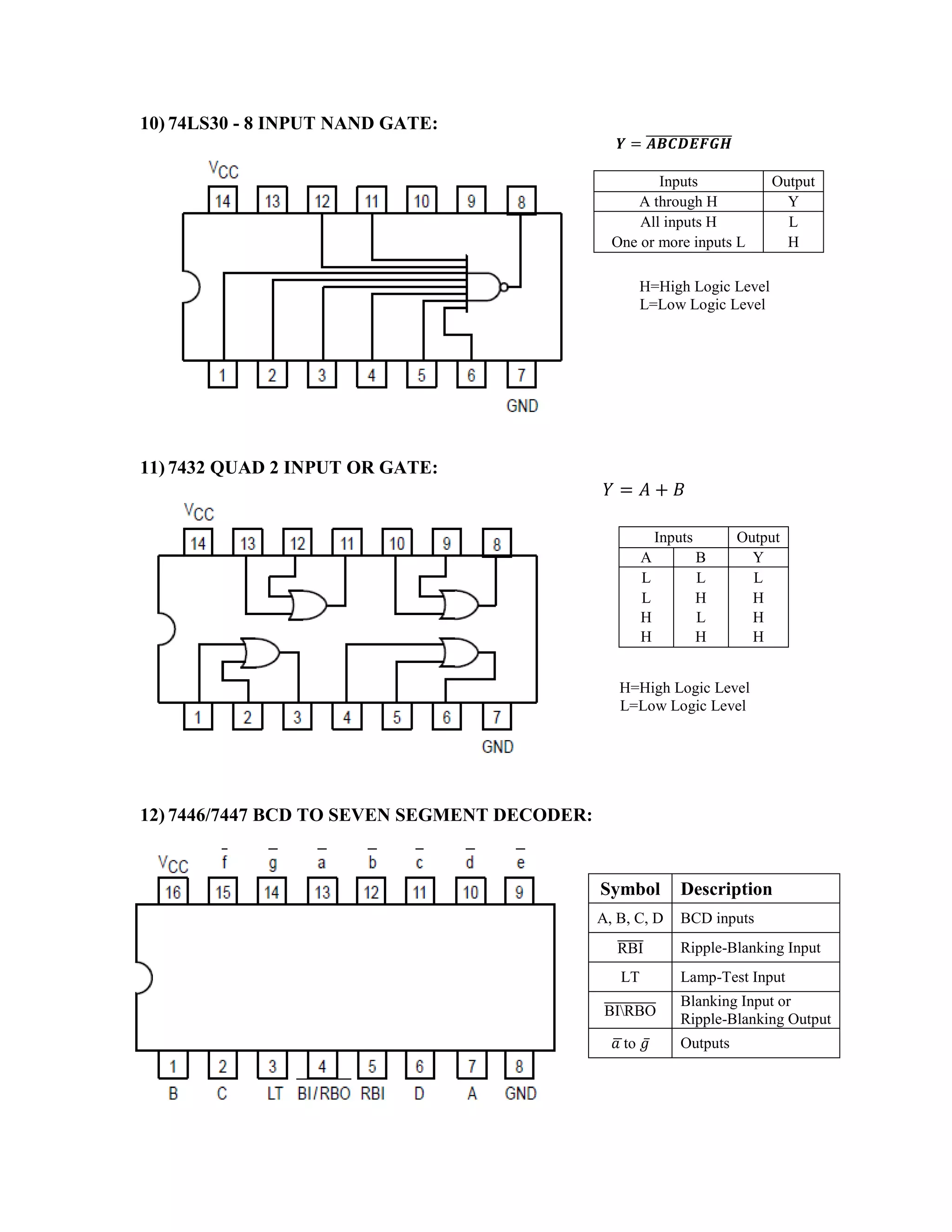

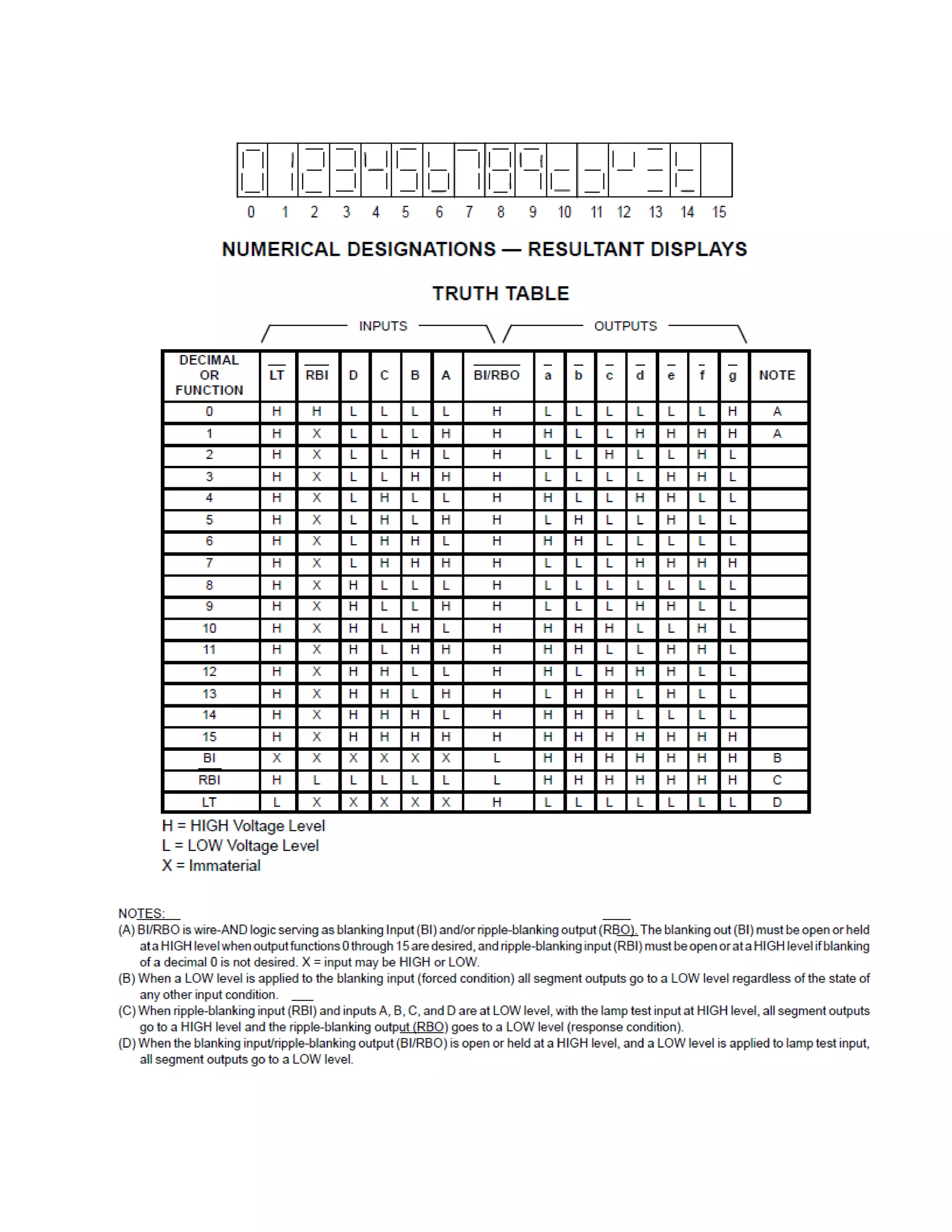

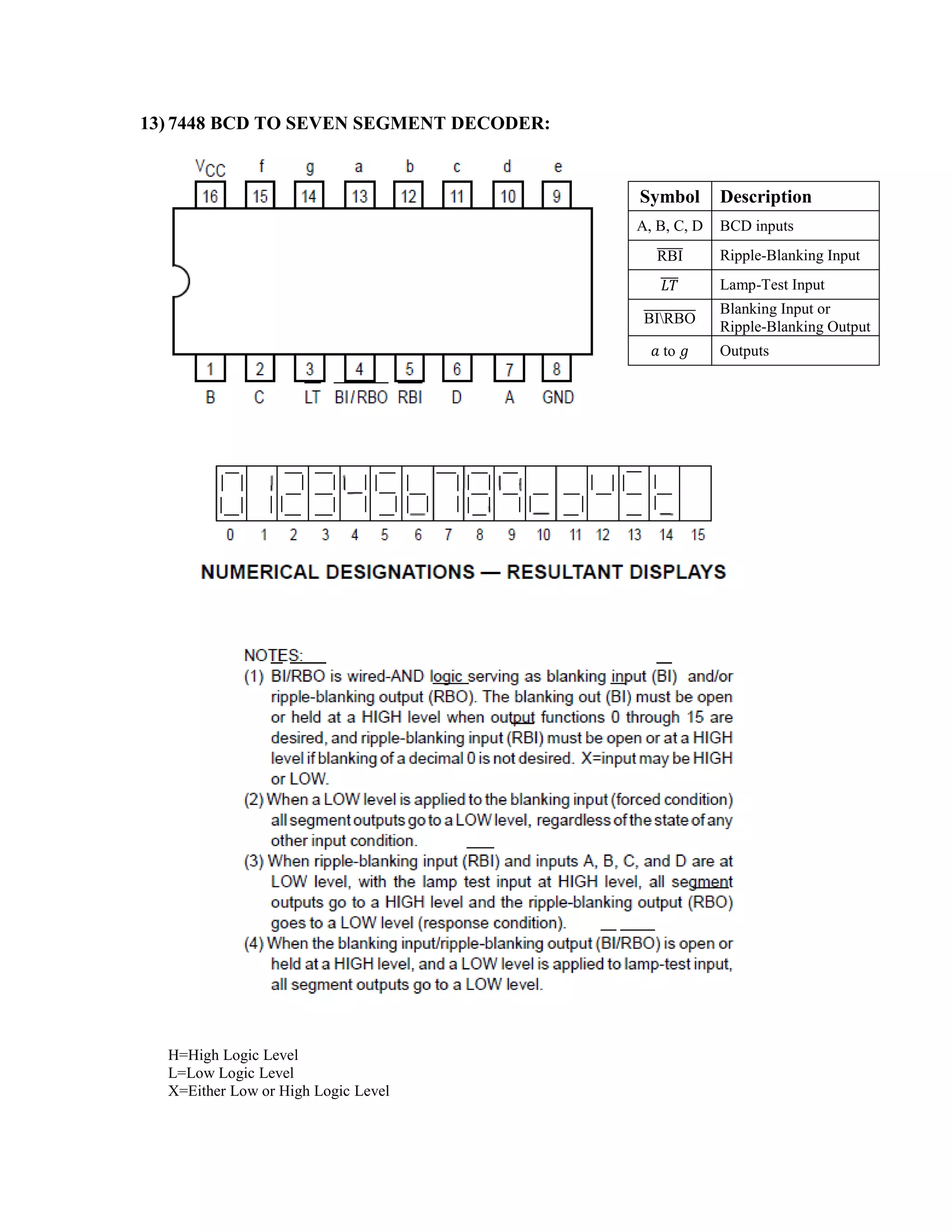

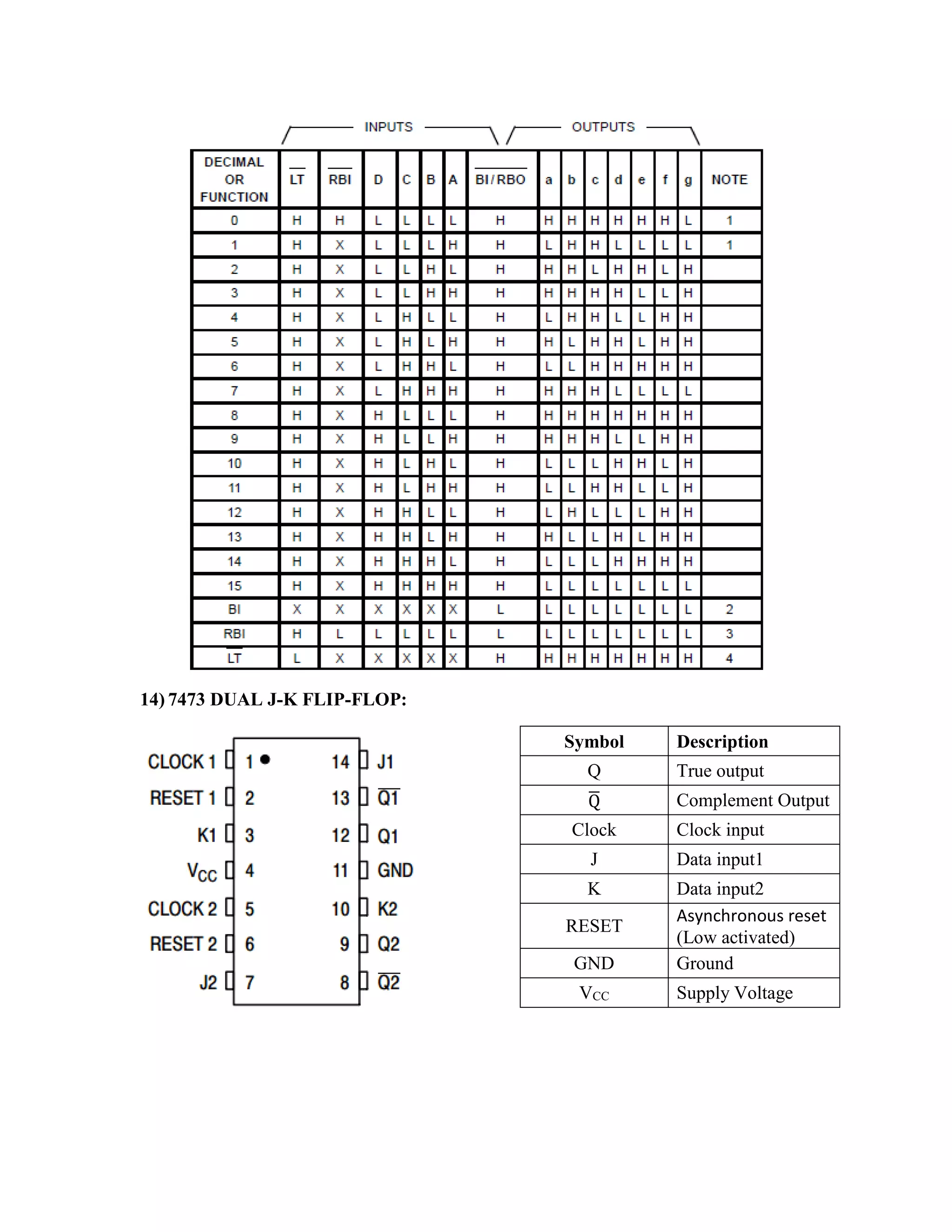

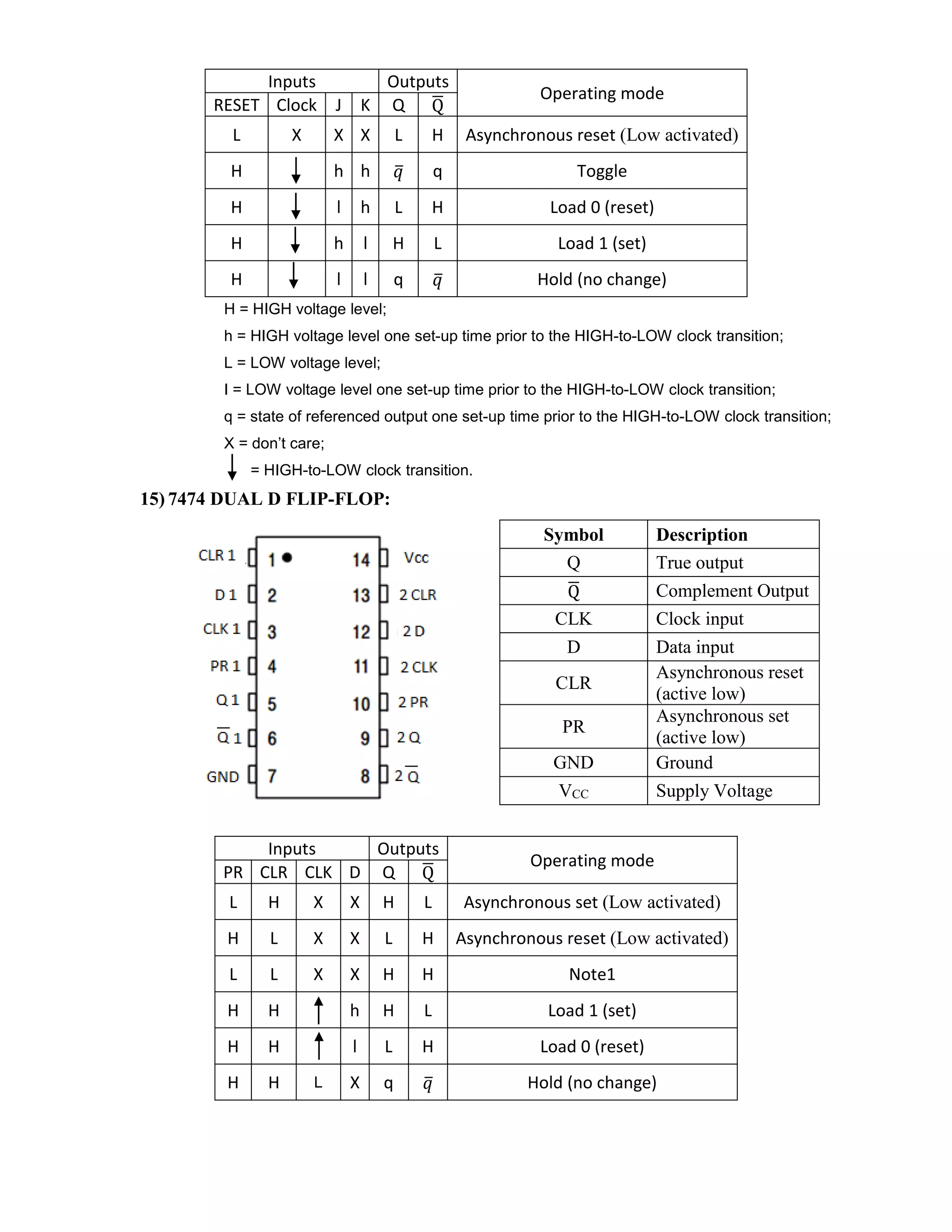

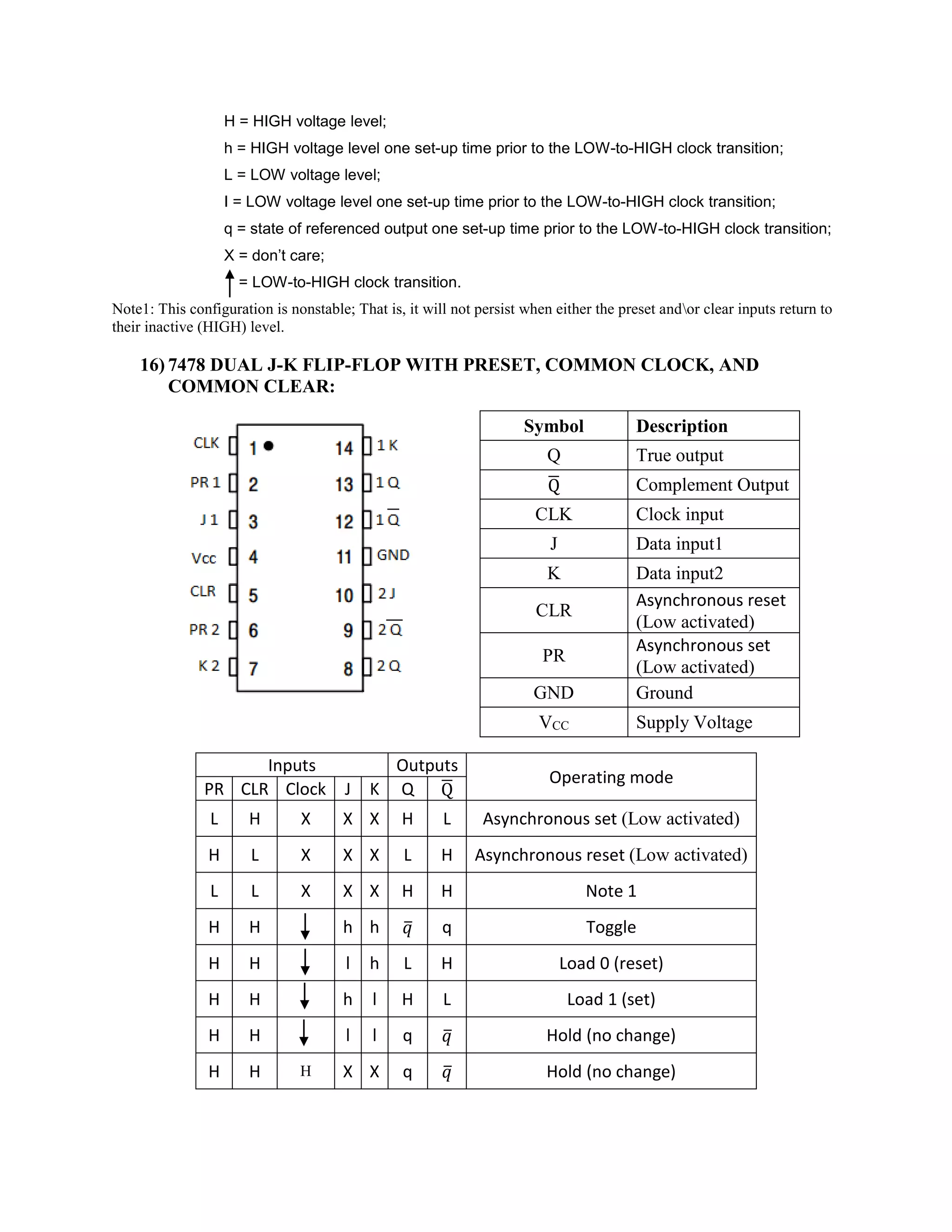

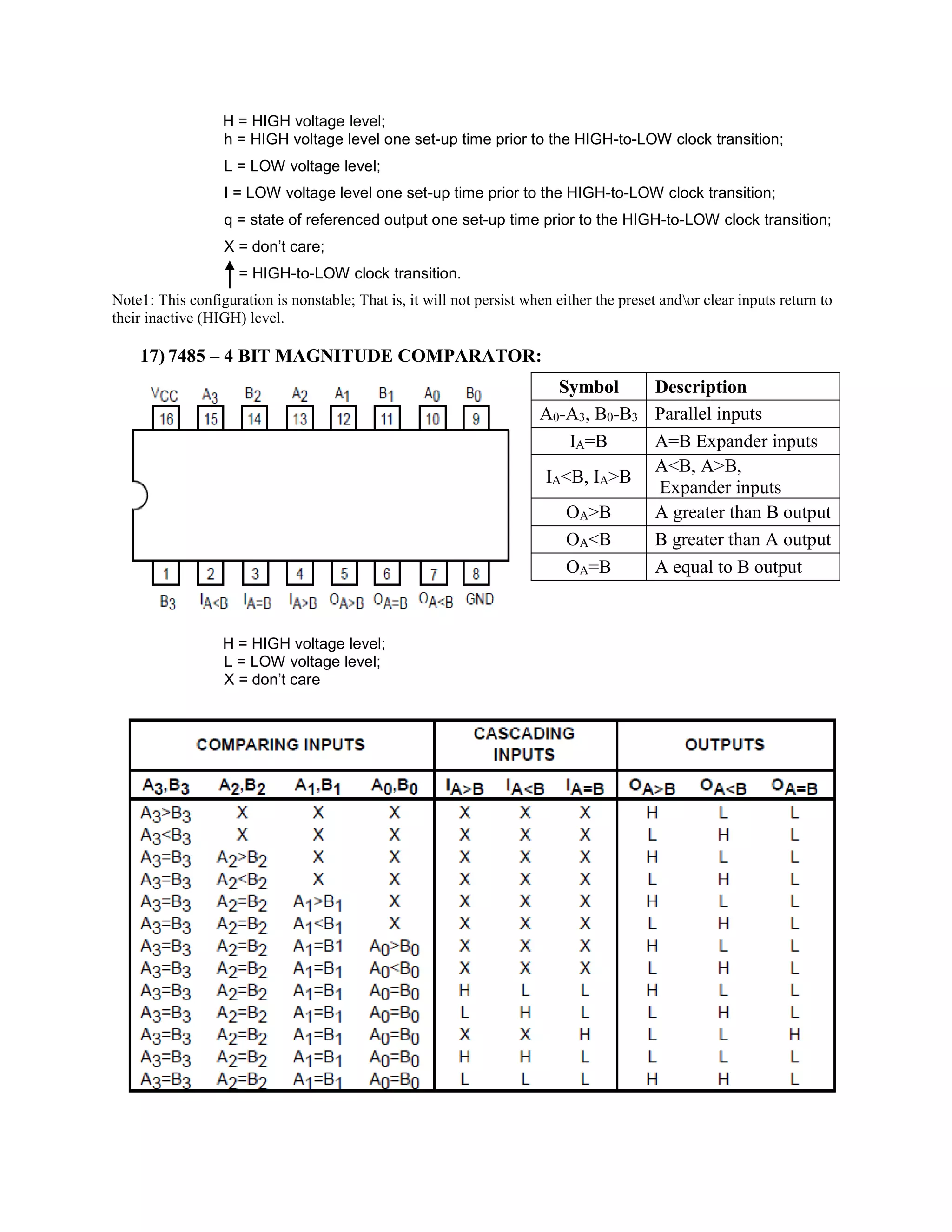

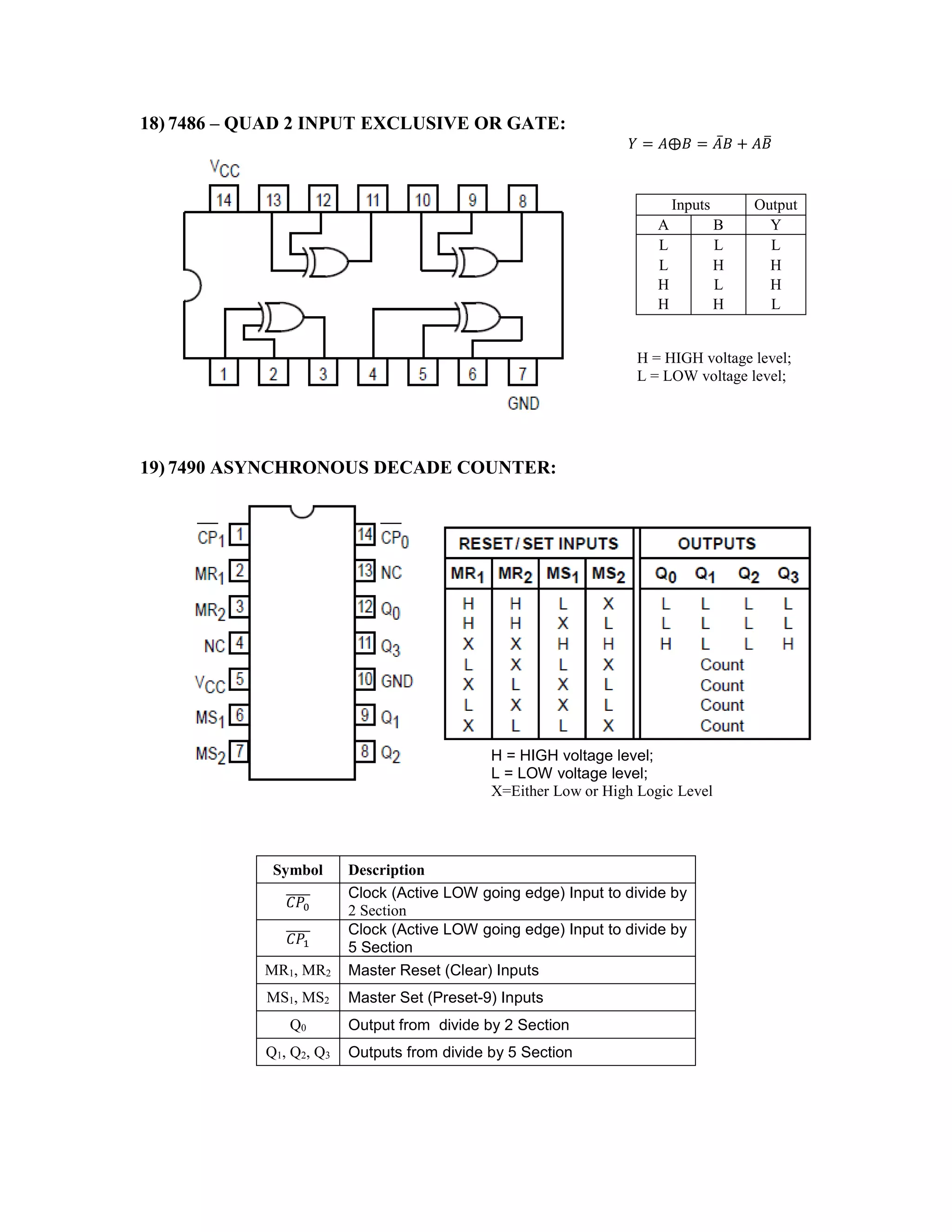

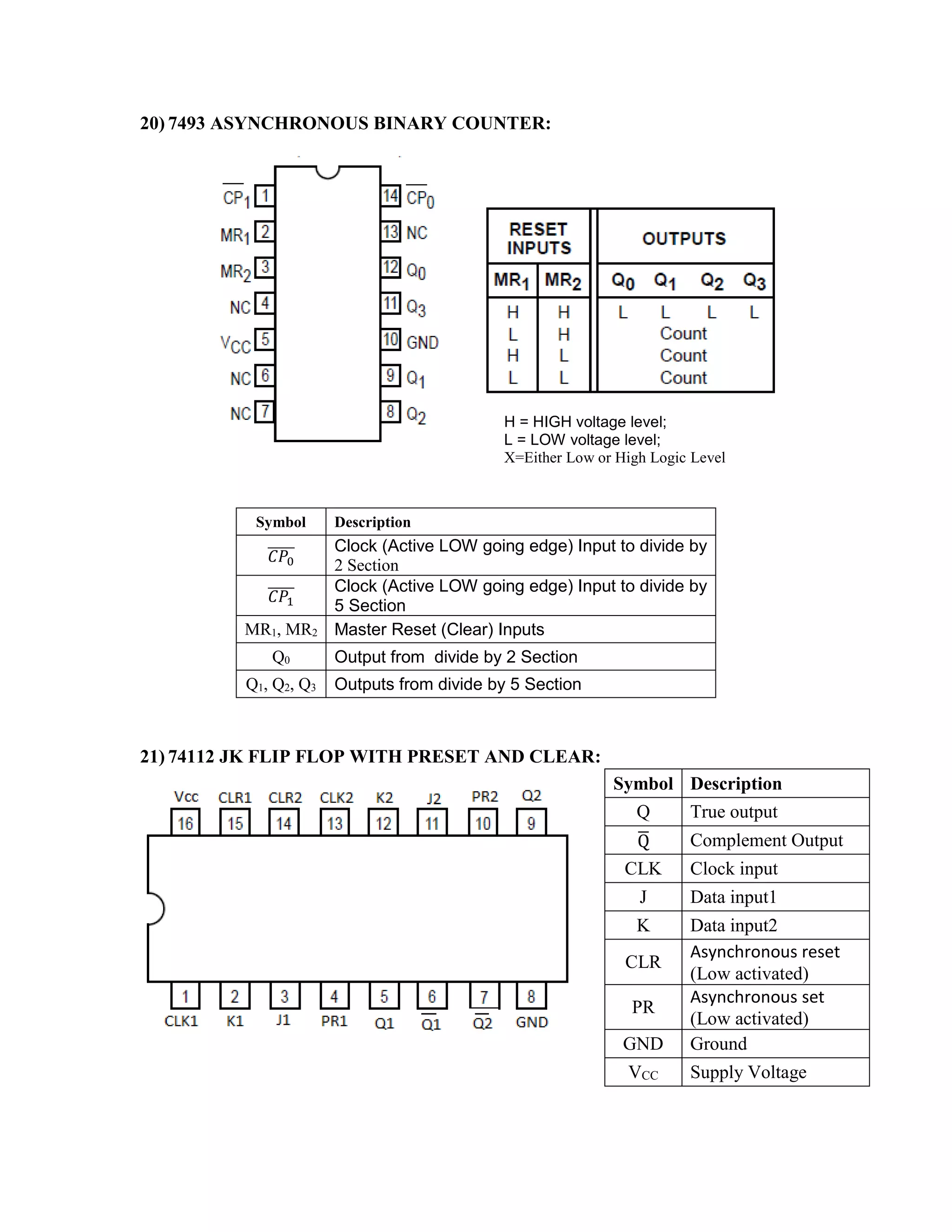

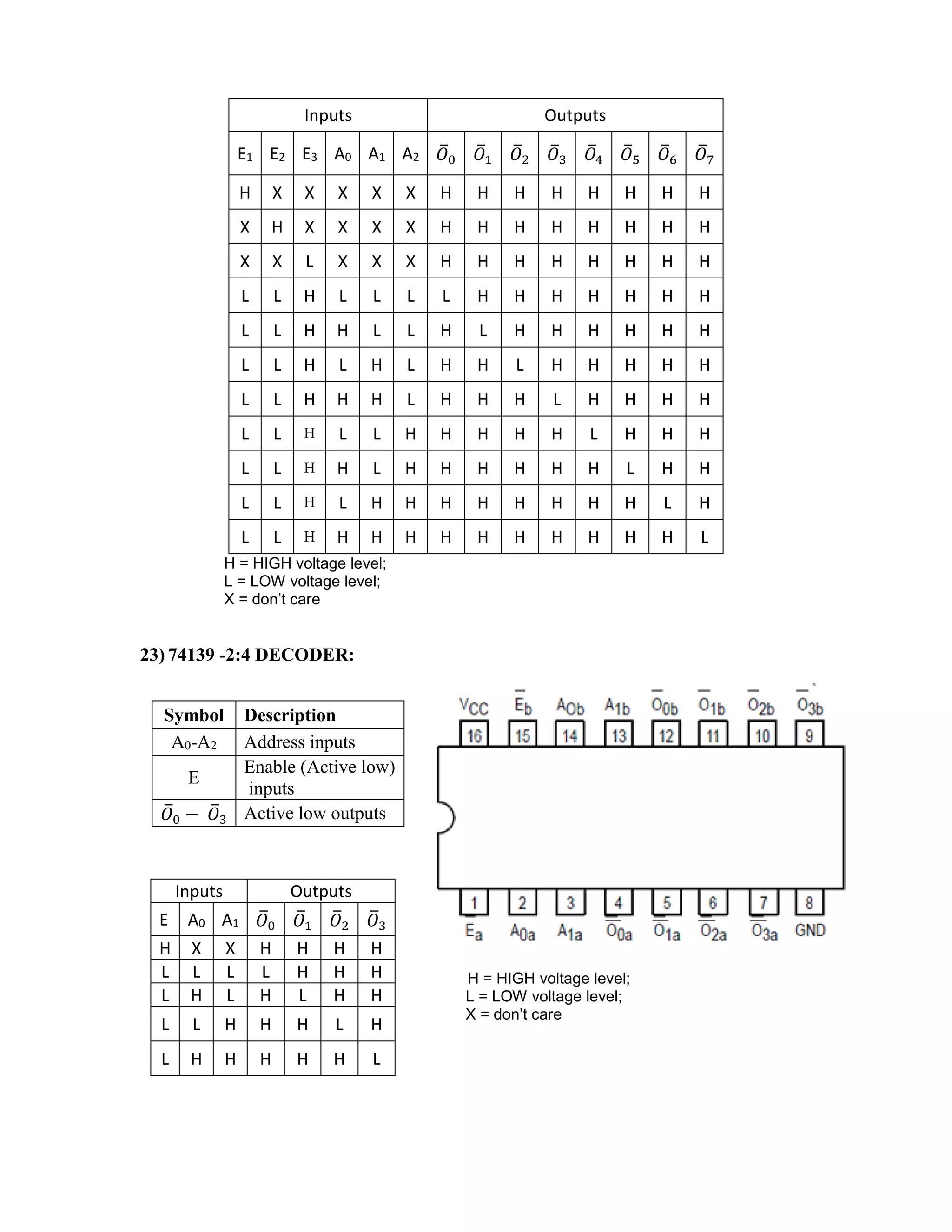

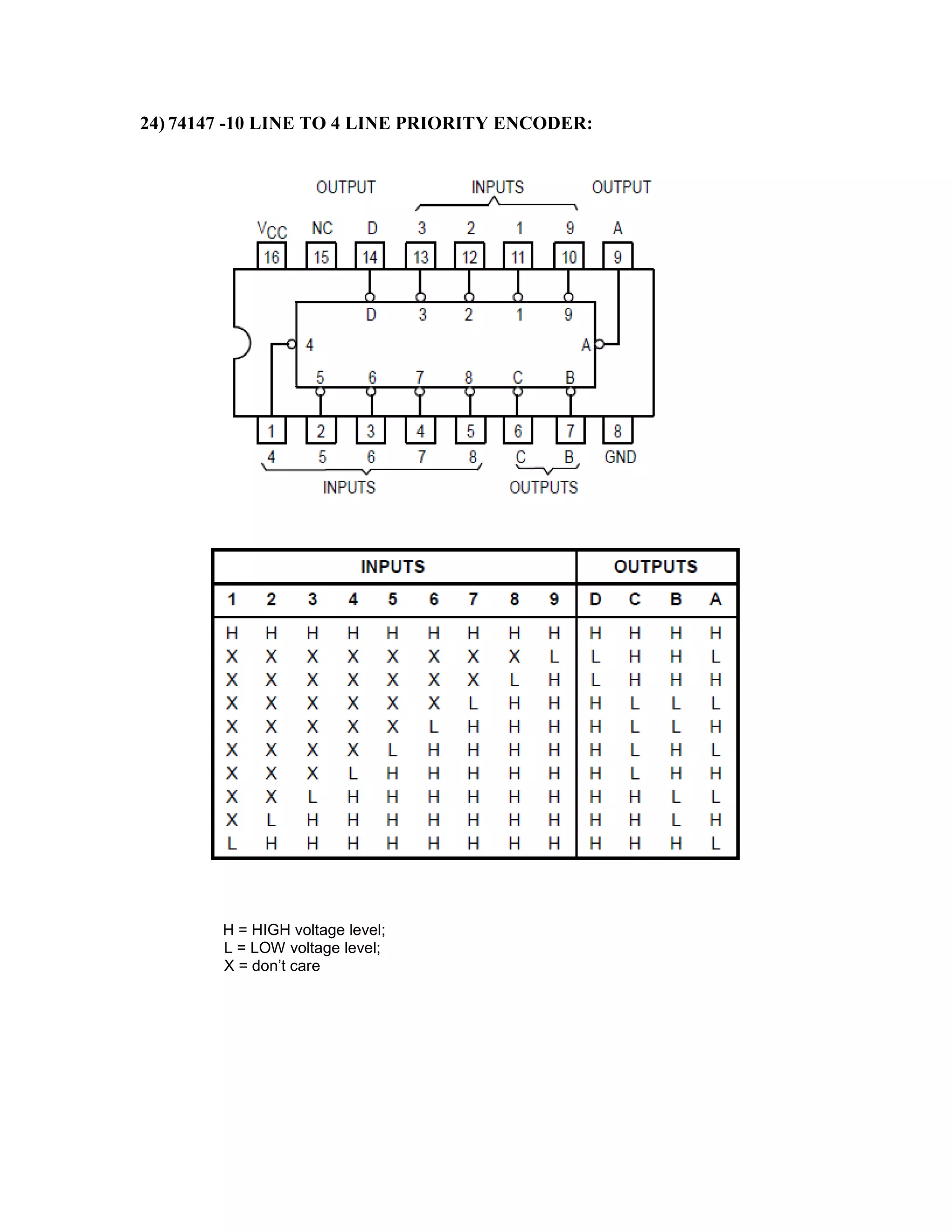

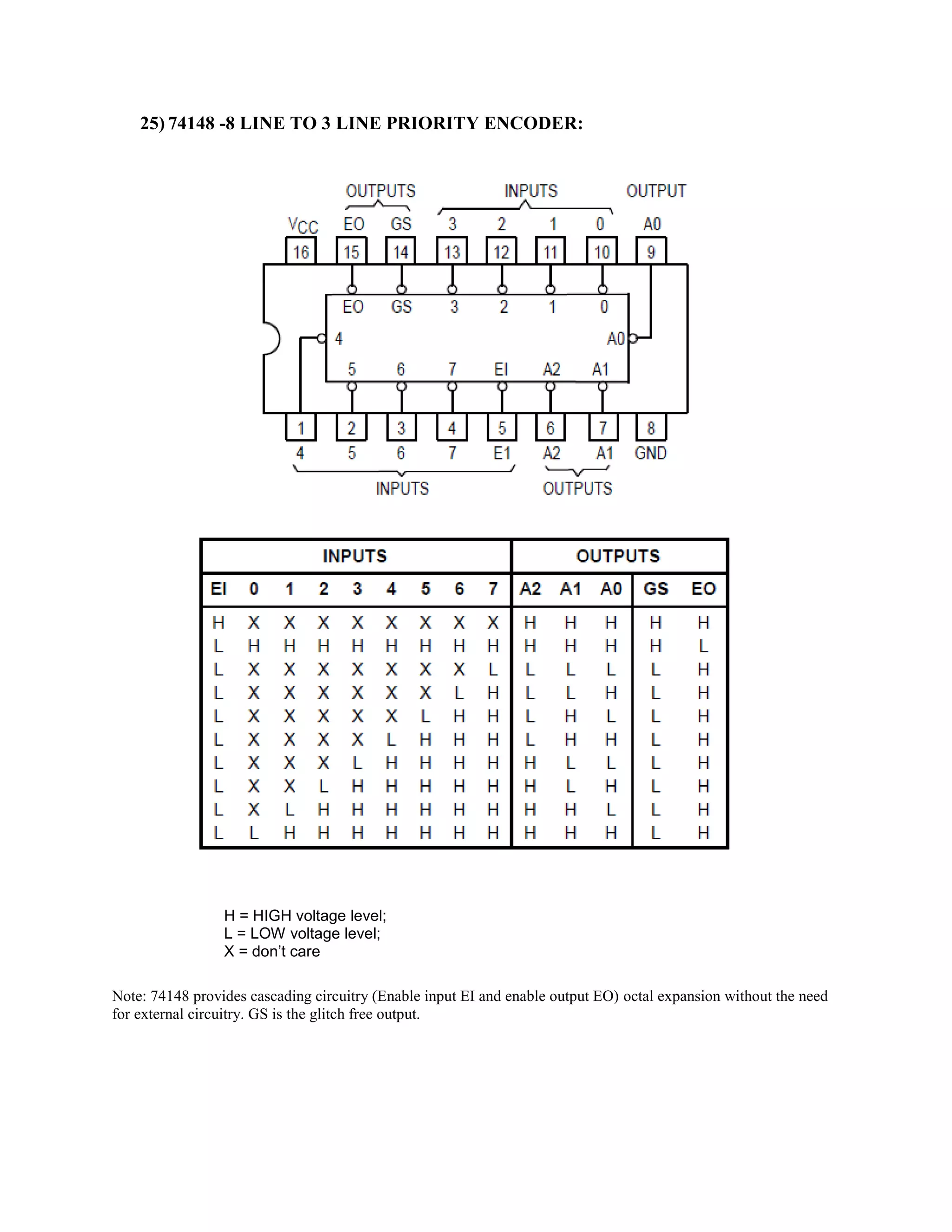

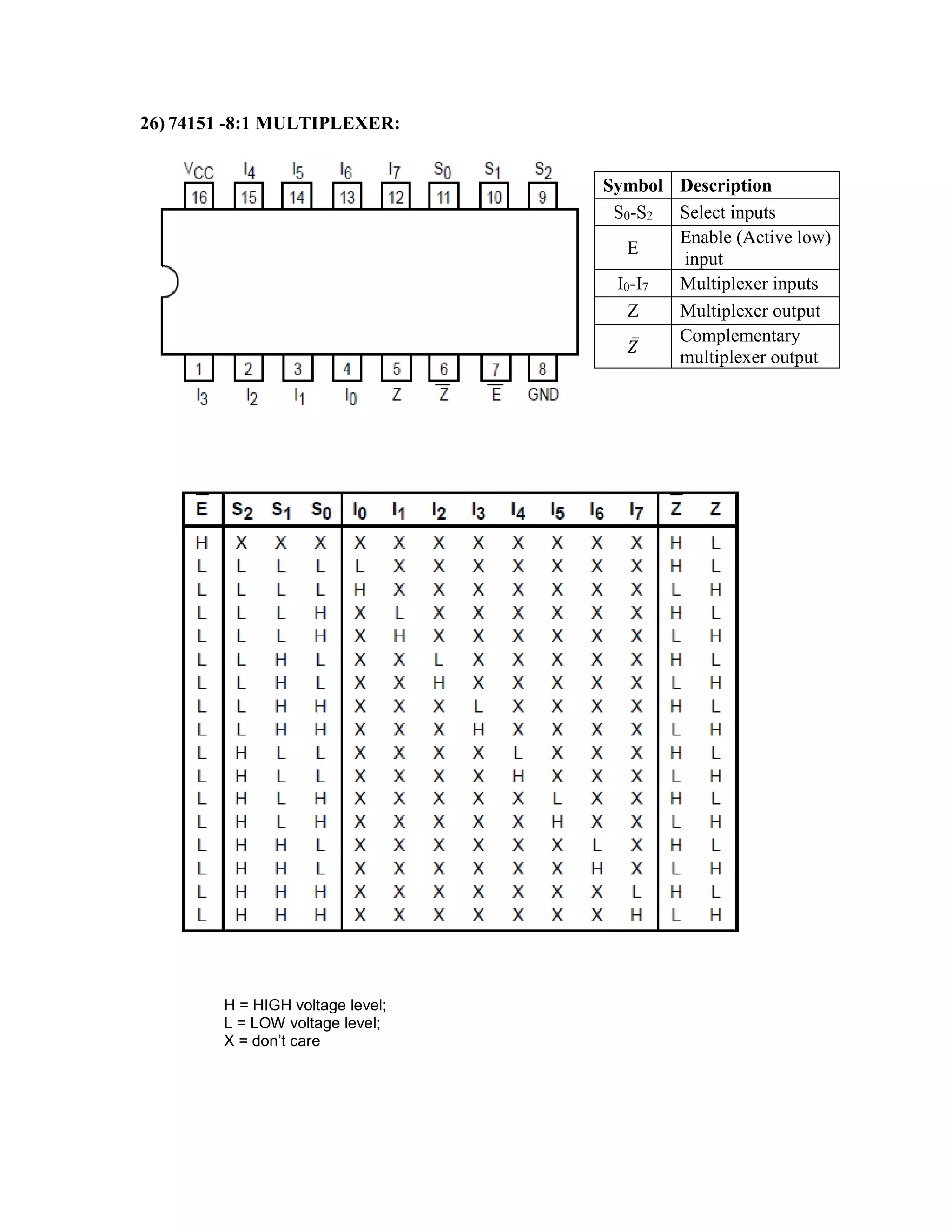

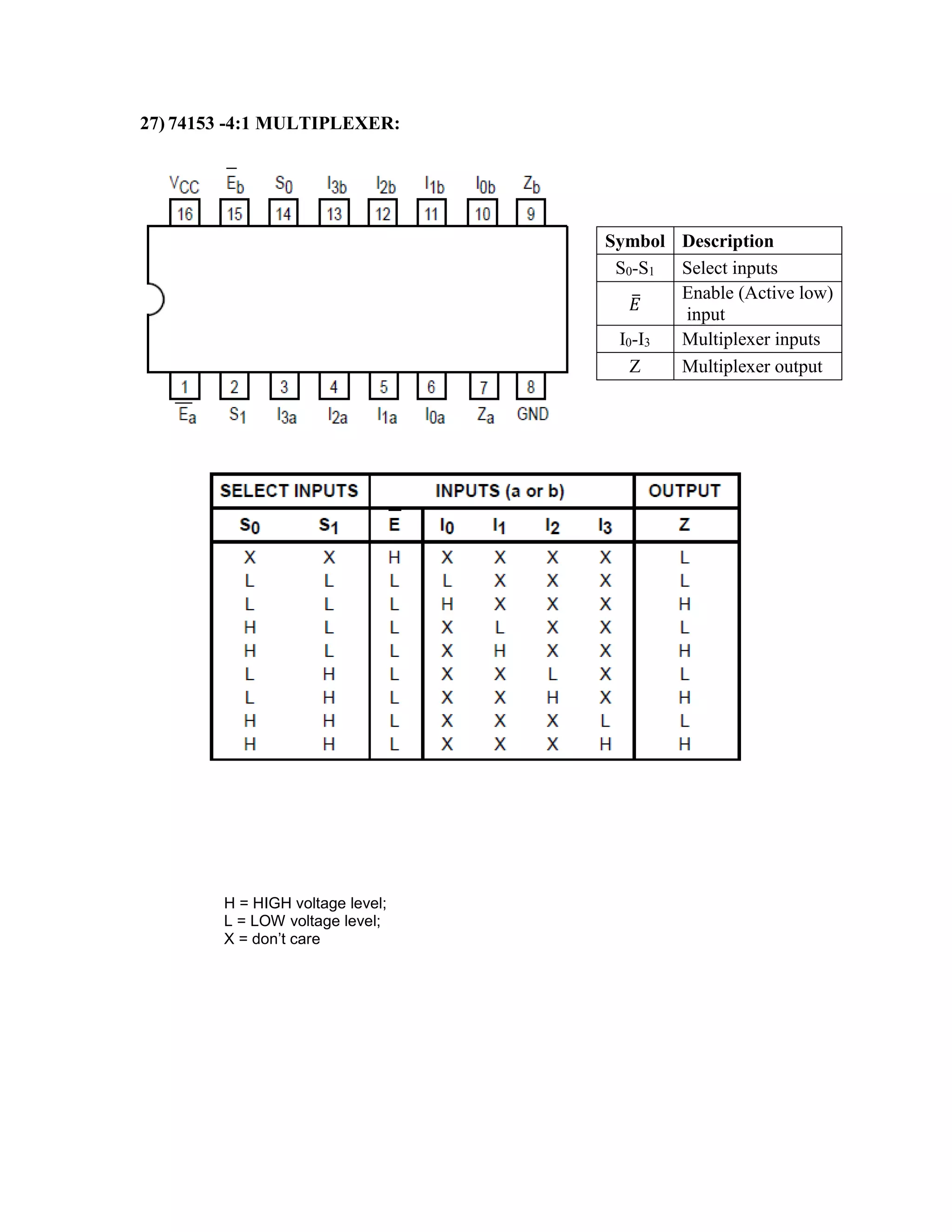

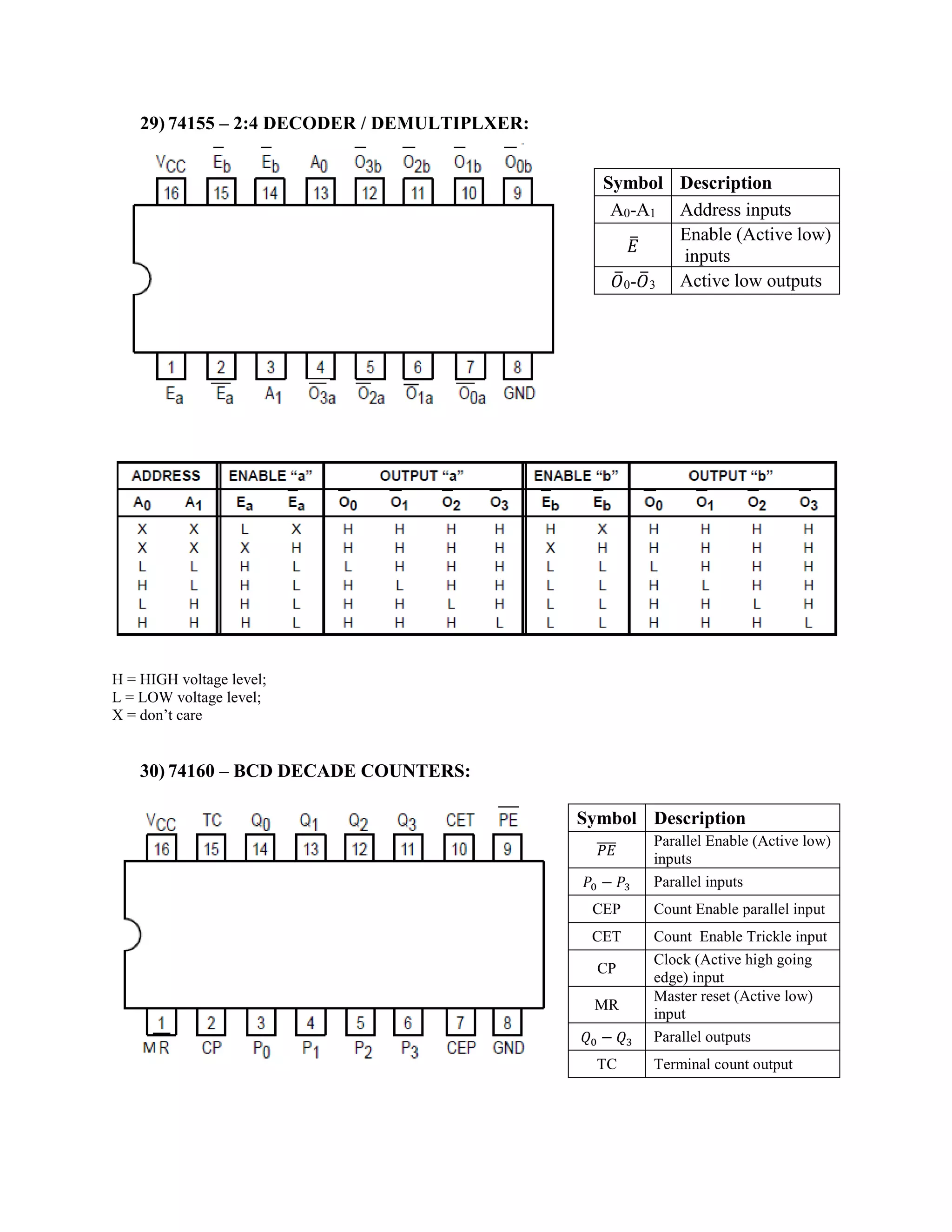

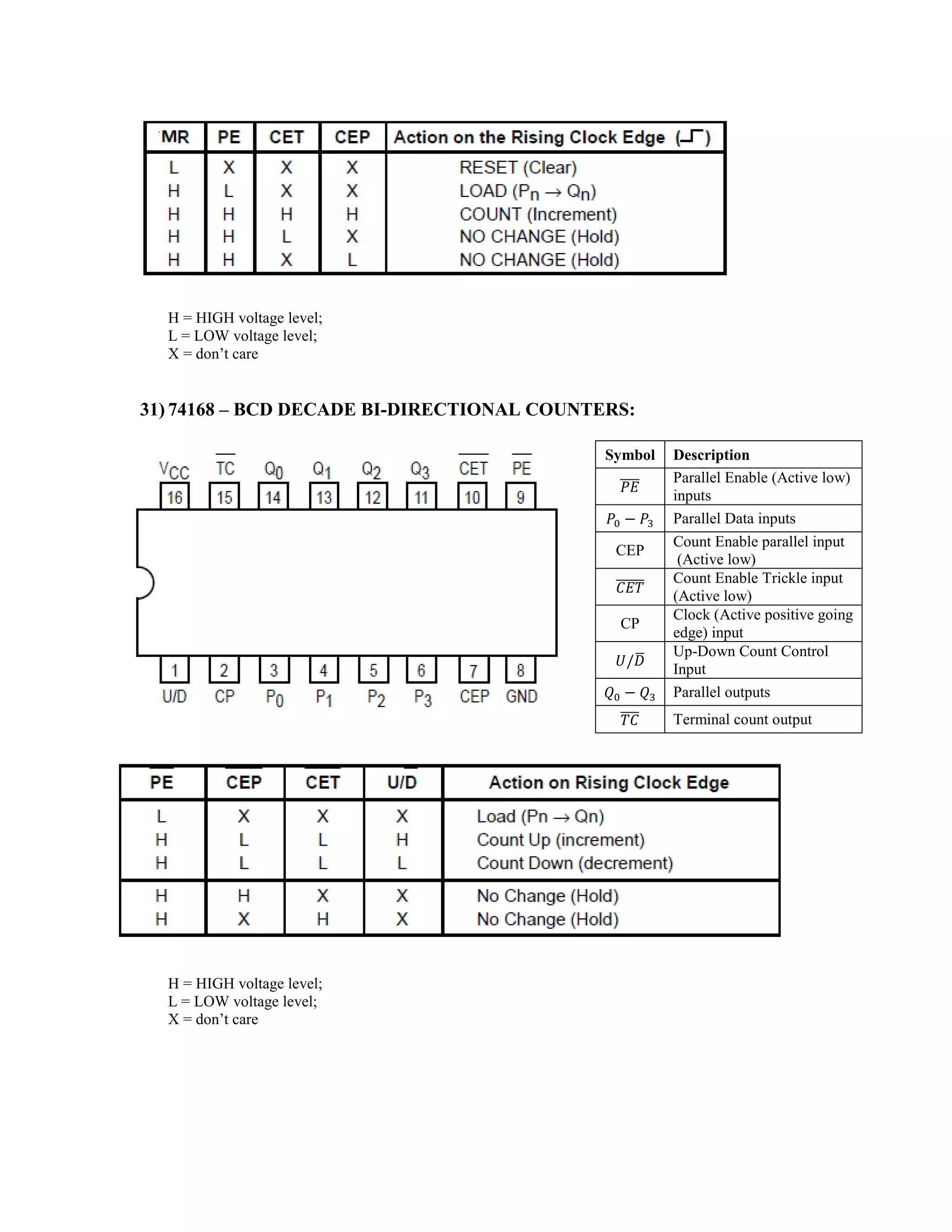

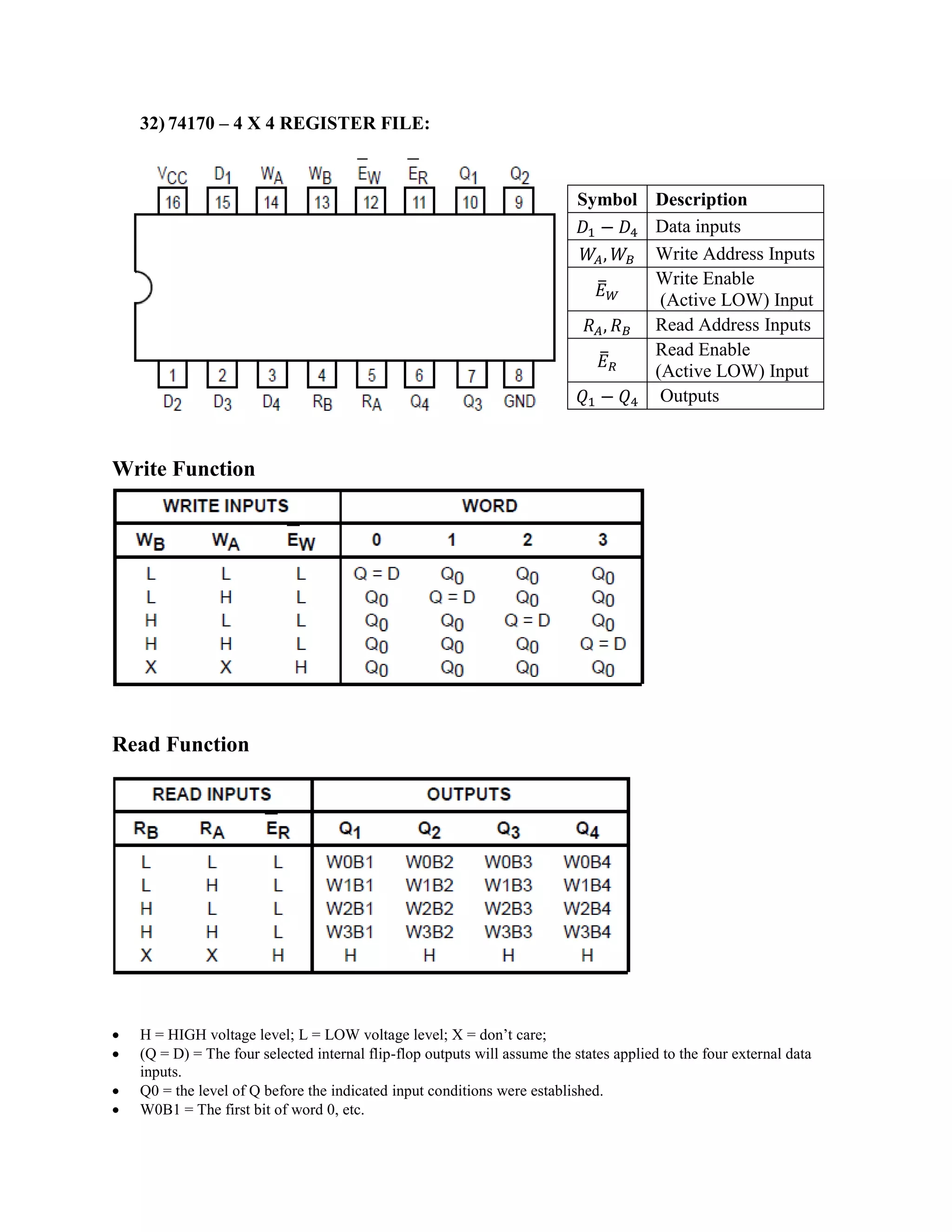

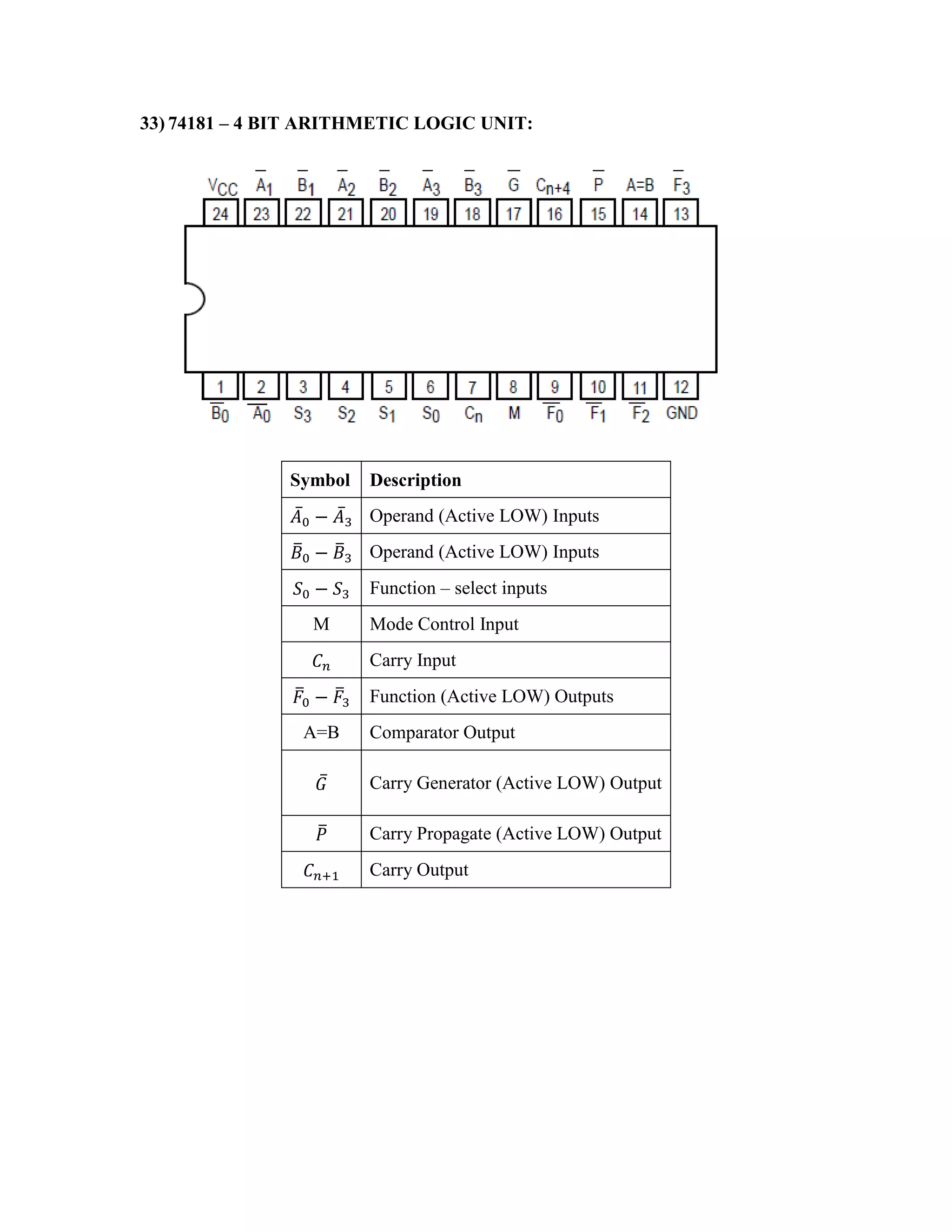

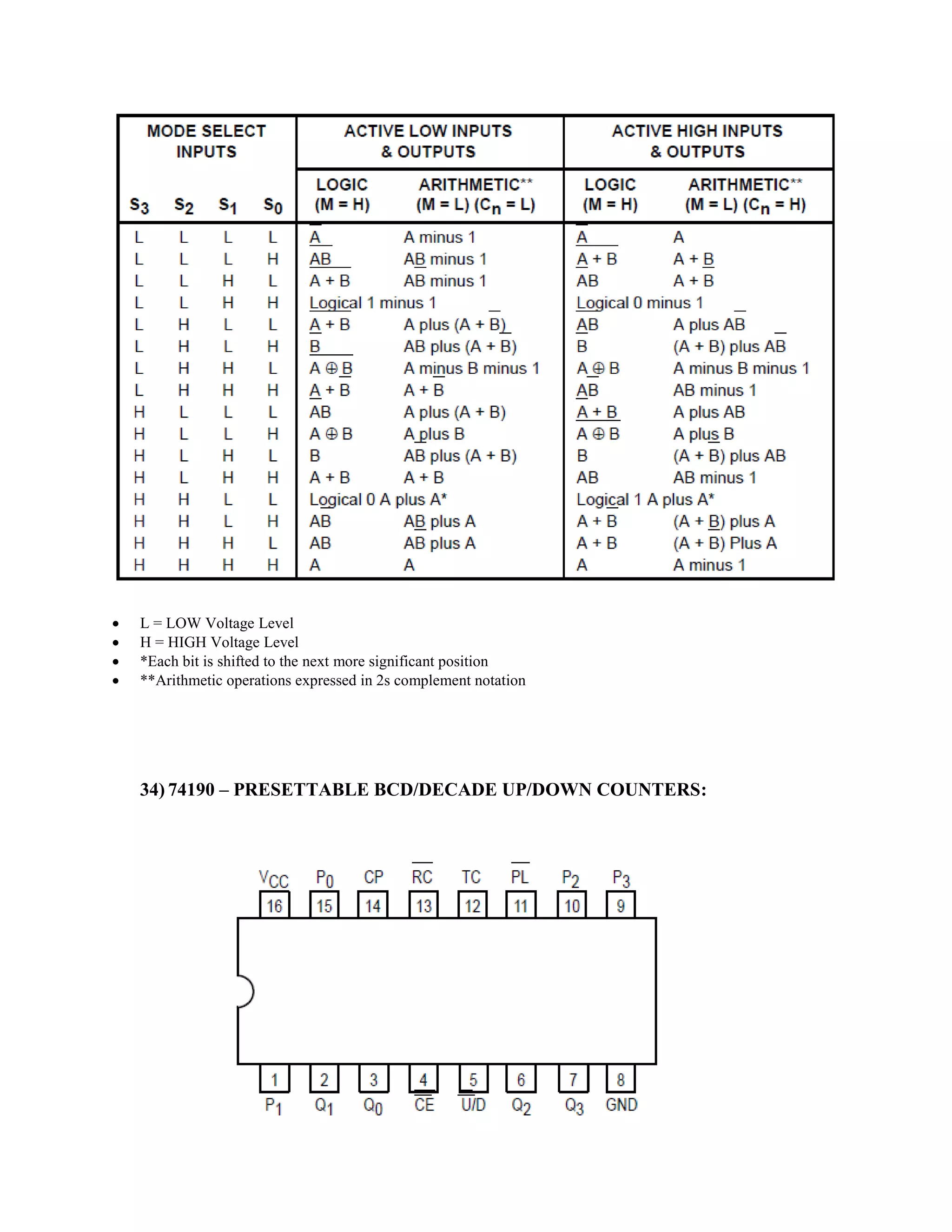

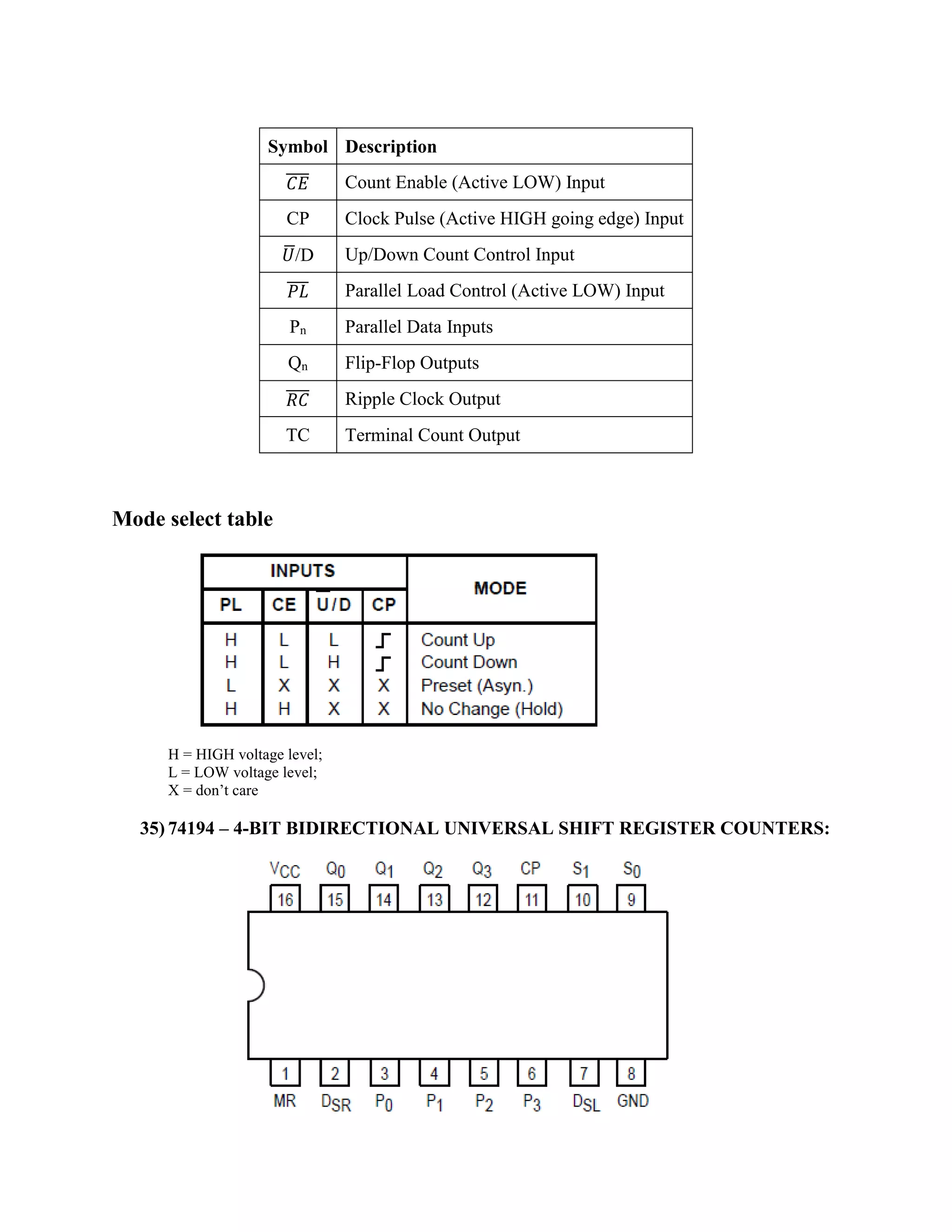

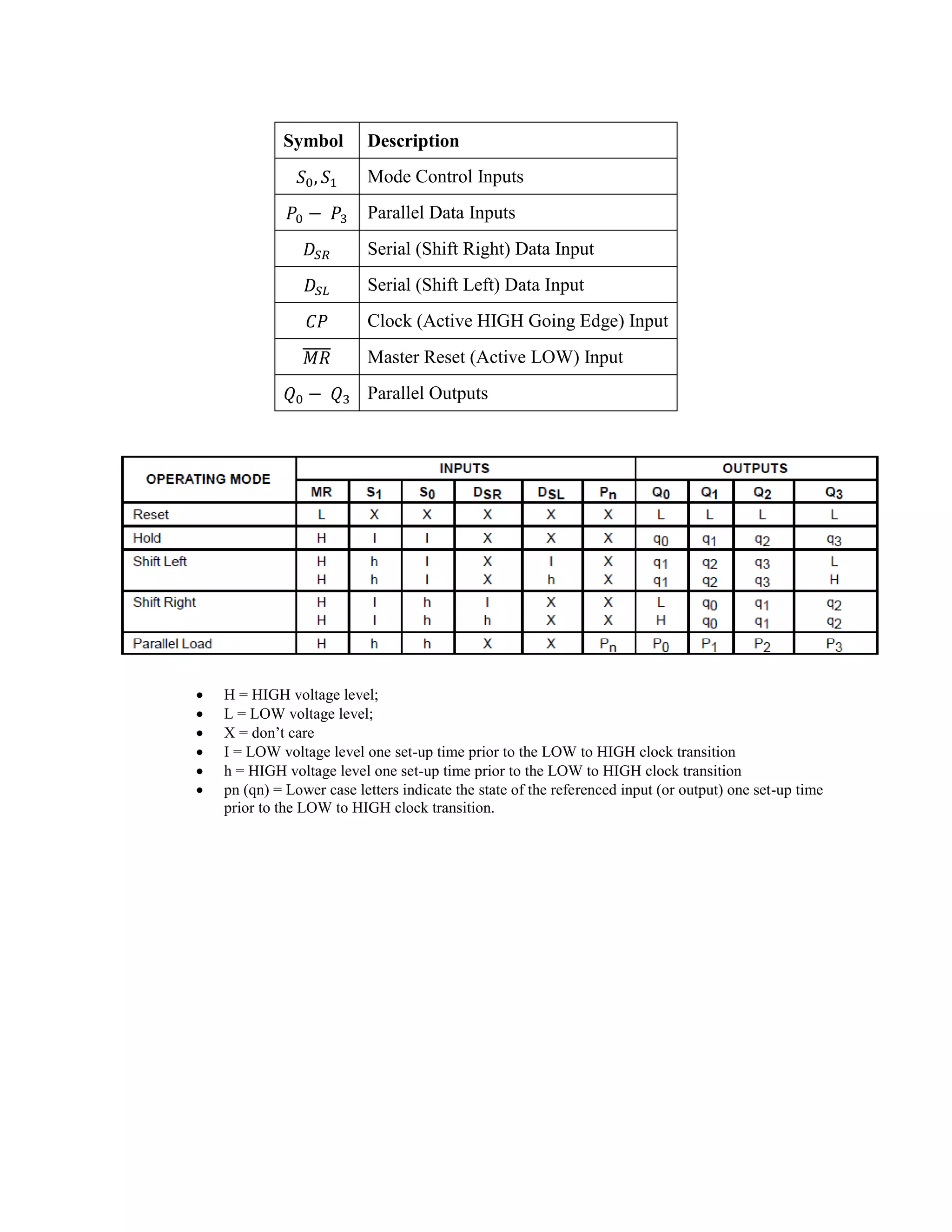

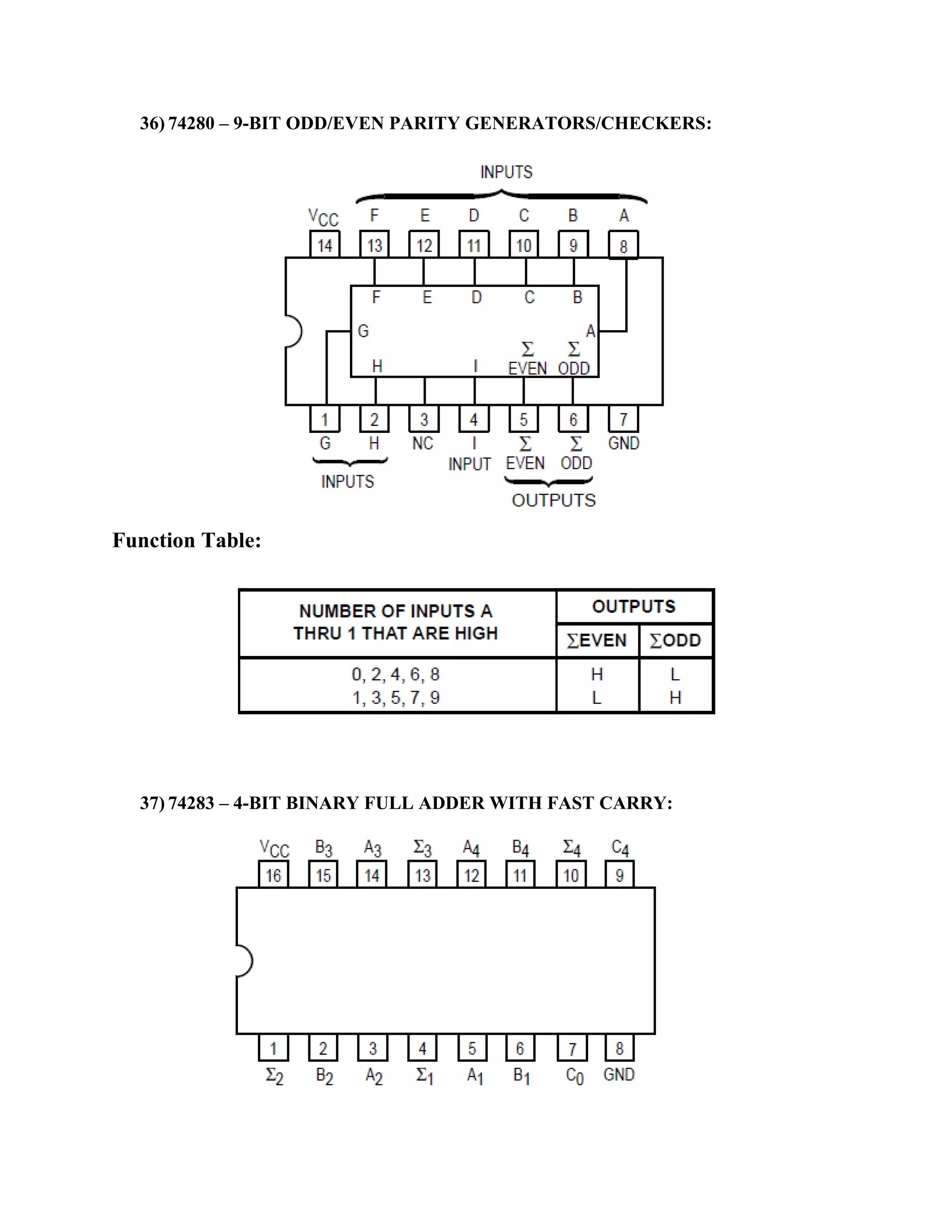

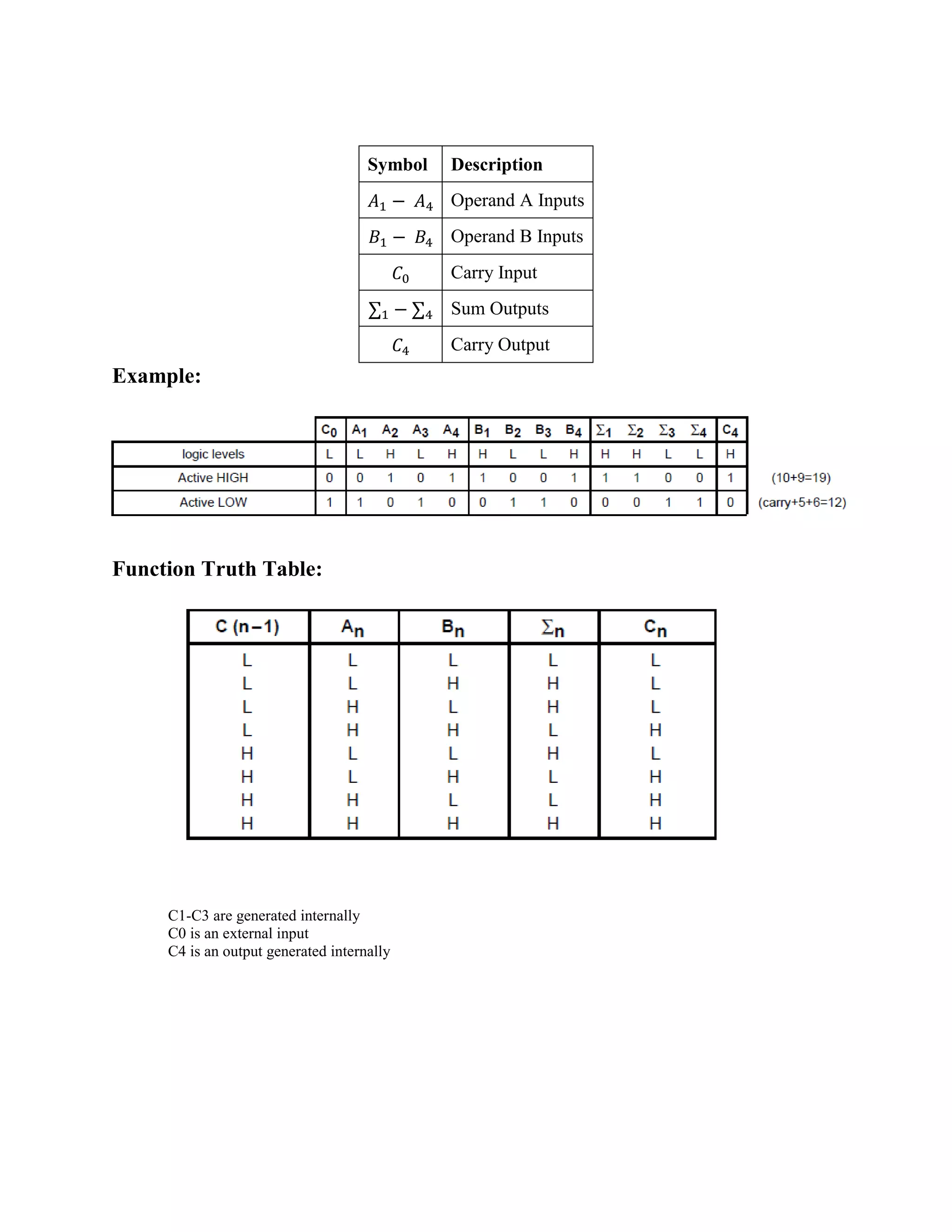

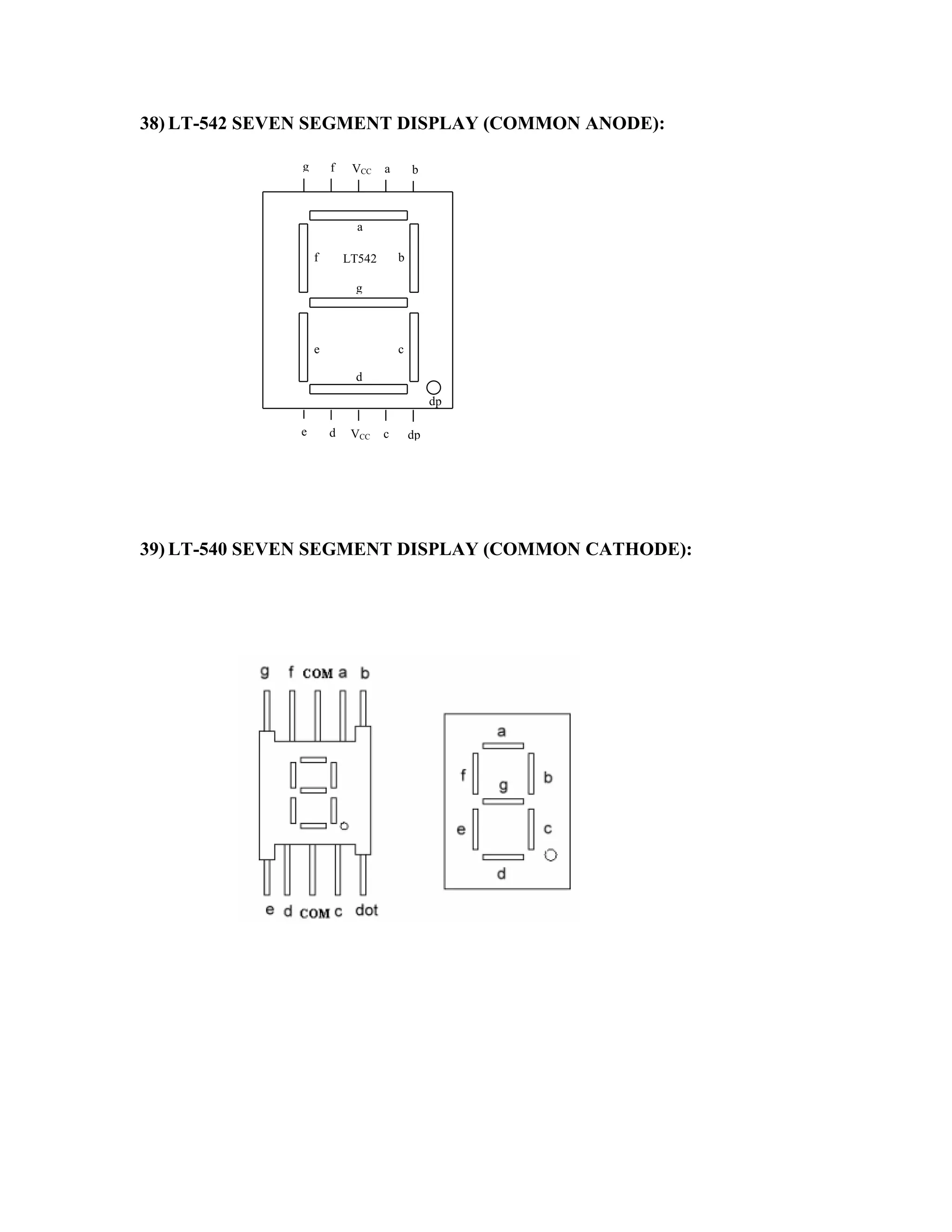

The document describes various digital logic integrated circuits (ICs) including their pin configurations, logic levels, truth tables and functions. It provides details for common ICs like NAND, NOR, AND, OR gates, flip-flops, decoders, multiplexers, comparators and counters. The document serves as a reference for the pin connections, symbols and operating modes of different digital logic family ICs.