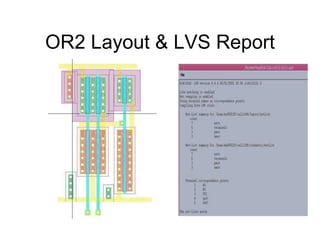

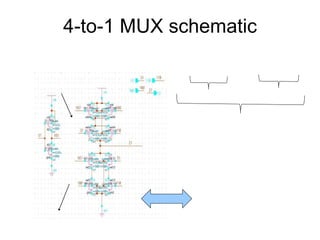

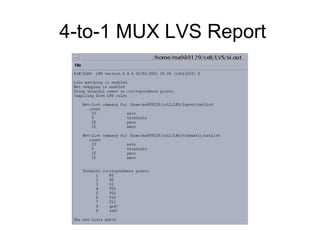

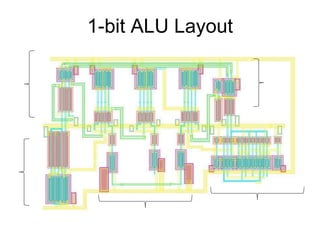

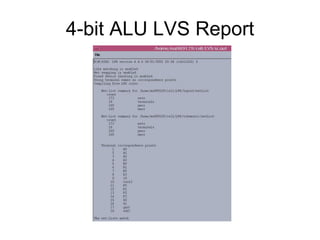

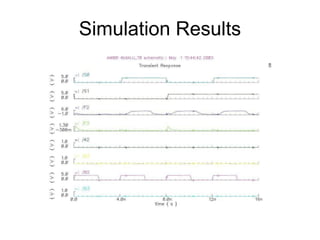

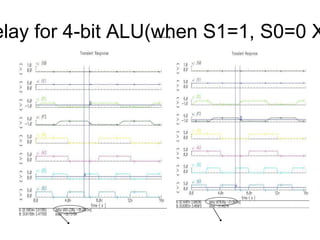

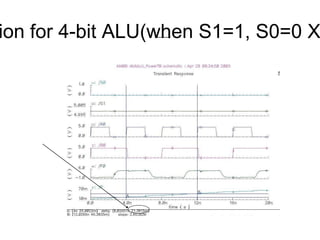

This document describes the design and simulation of a 4-bit arithmetic logic unit (ALU) circuit. It includes block diagrams and schematics of the logic gates, full adder, 4-to-1 multiplexer, 1-bit ALU, and 4-bit ALU. Simulation results demonstrate the circuit's functionality when performing operations on different input patterns, and propagation delays are reported for each component.