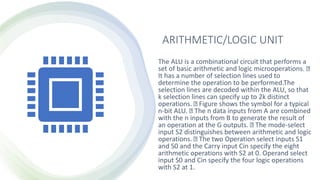

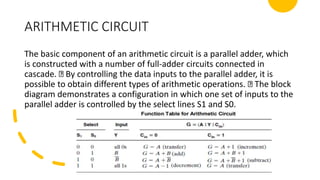

S. Hari Prasanth's digital principles and computer design course covers computer architecture basics including the datapath and control unit. The document discusses how the datapath contains registers, buses, multiplexers, and an arithmetic logic unit (ALU) to perform operations on data. It explains how the control unit provides signals to direct data flow and the ALU operation for instructions like adding register values. The ALU is described as a combinational logic circuit that performs arithmetic and logic operations based on selection lines that specify the operation.