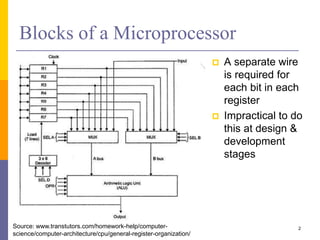

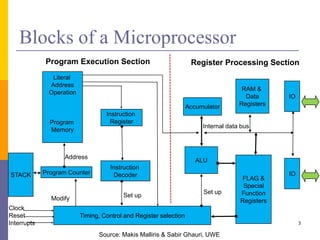

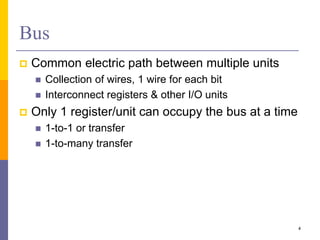

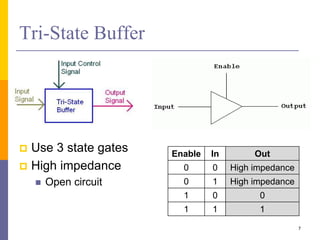

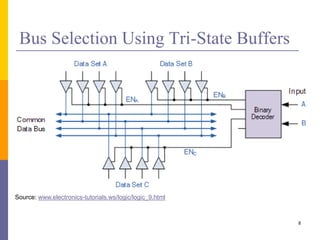

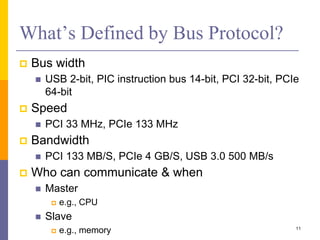

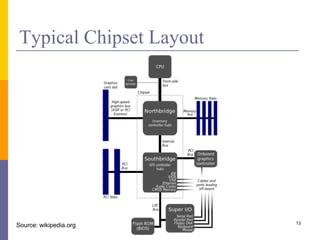

The document discusses computer buses and their role in microprocessor design. It defines a bus as a common electric path that interconnects registers and input/output units using a collection of wires. Buses allow for the transfer of data between components using techniques like multiplexers and tri-state buffers. The document outlines different types of common computer buses and bus protocols. It also compares serial and parallel bus architectures.