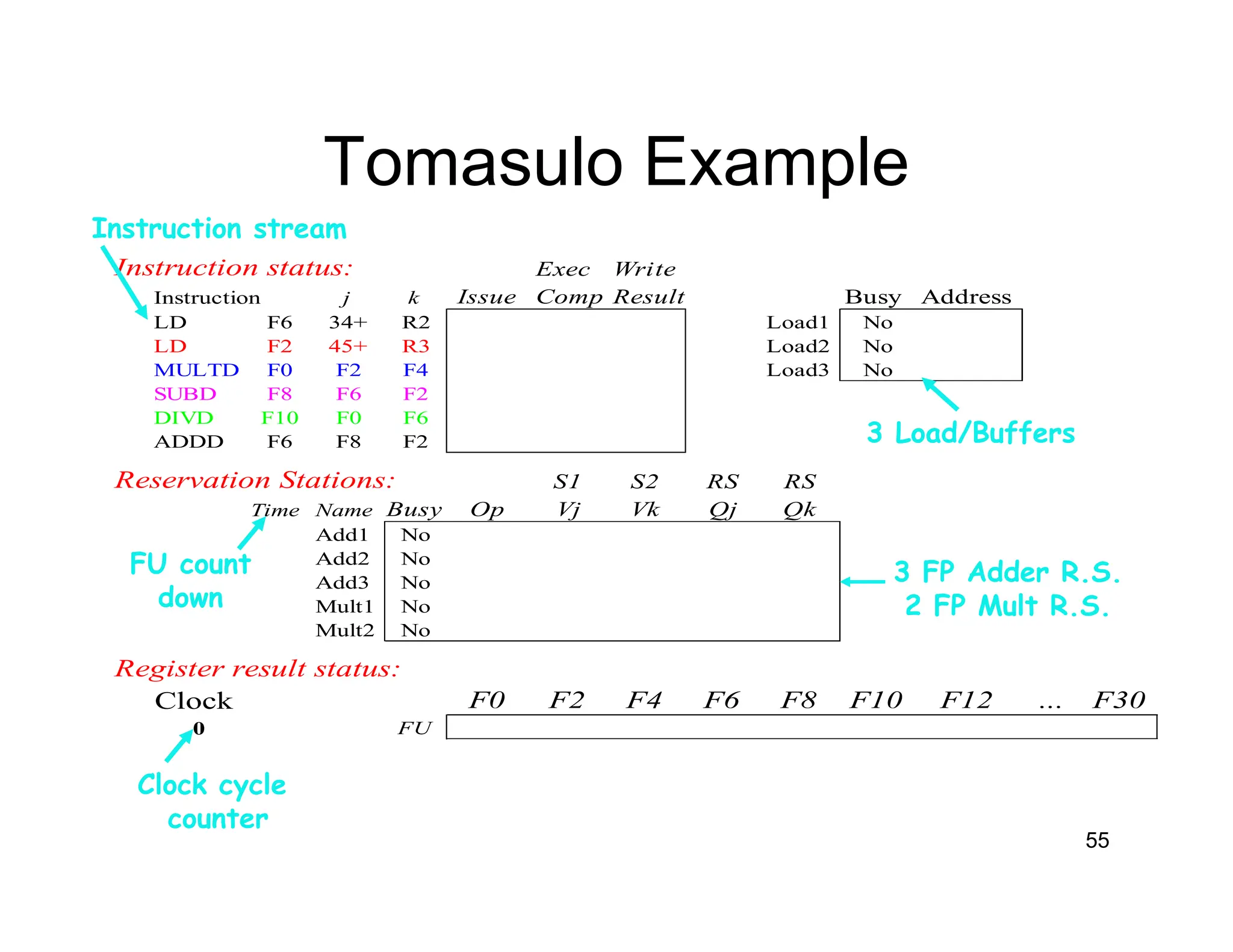

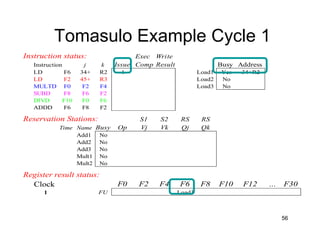

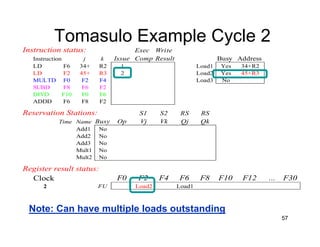

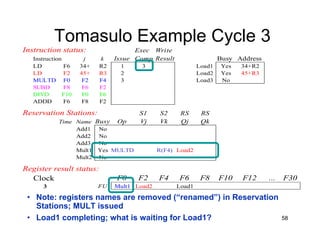

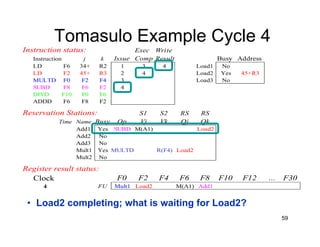

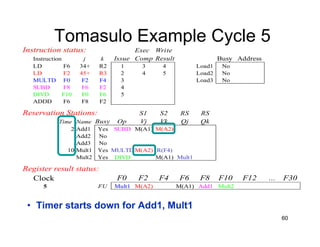

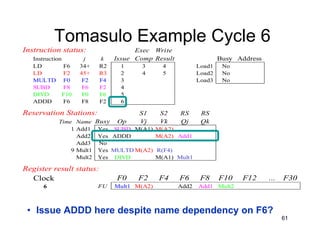

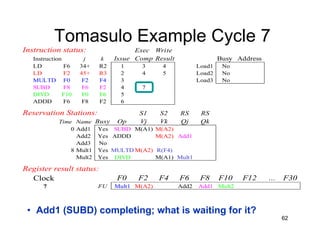

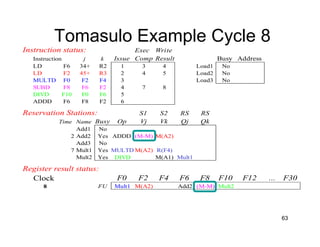

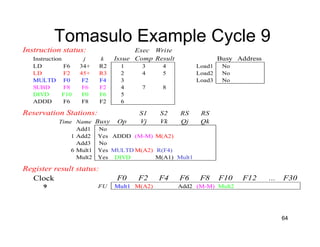

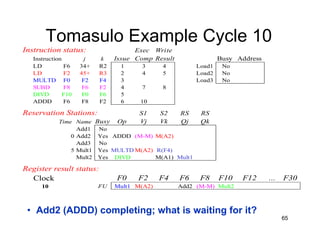

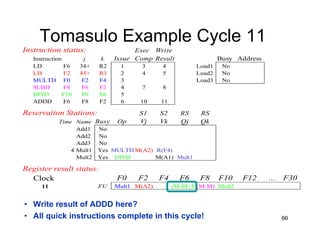

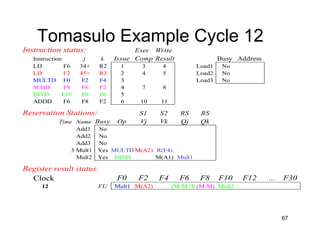

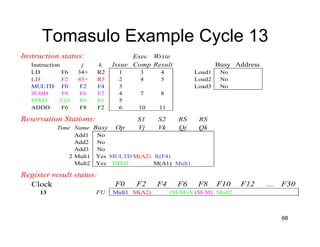

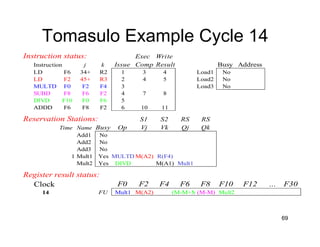

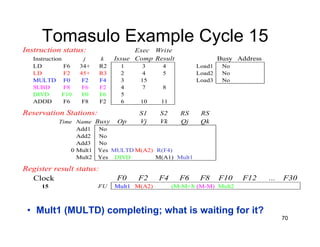

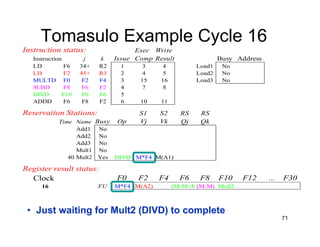

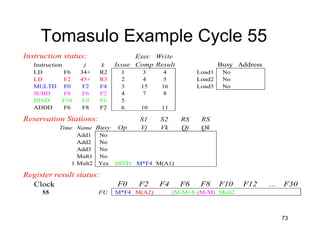

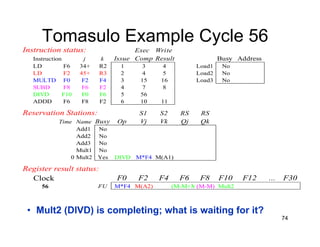

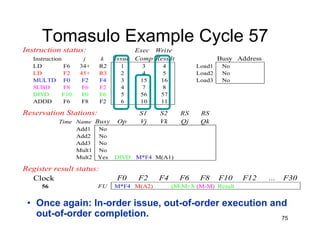

The document provides a detailed example of the Tomasulo algorithm, illustrating the instruction status, reservation stations, and register results over multiple clock cycles. It highlights the execution of various floating-point instructions and how they are scheduled and completed in a non-blocking manner. The example emphasizes issues like dependencies and the handling of multiple outstanding loads in a dynamically scheduled environment.