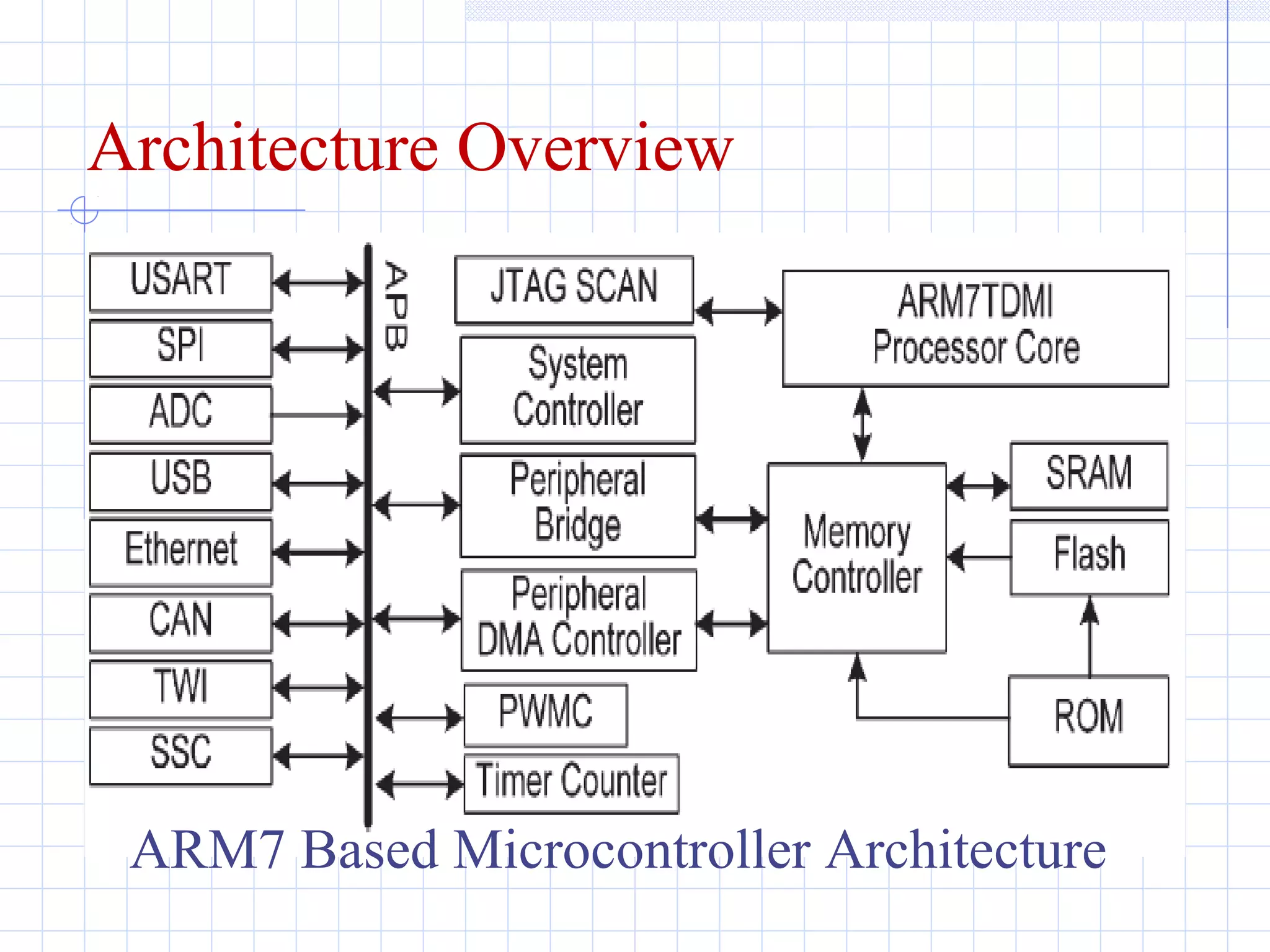

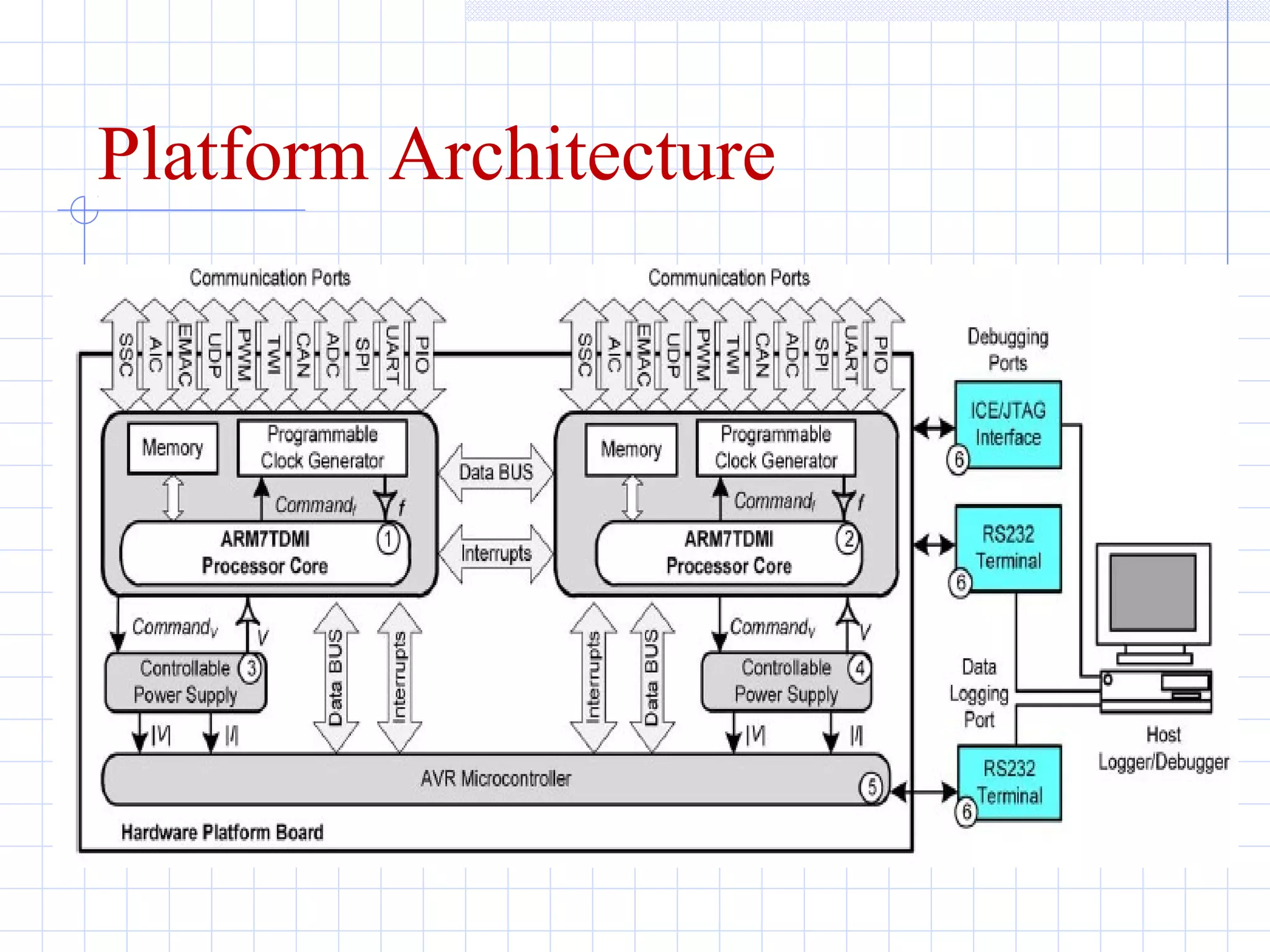

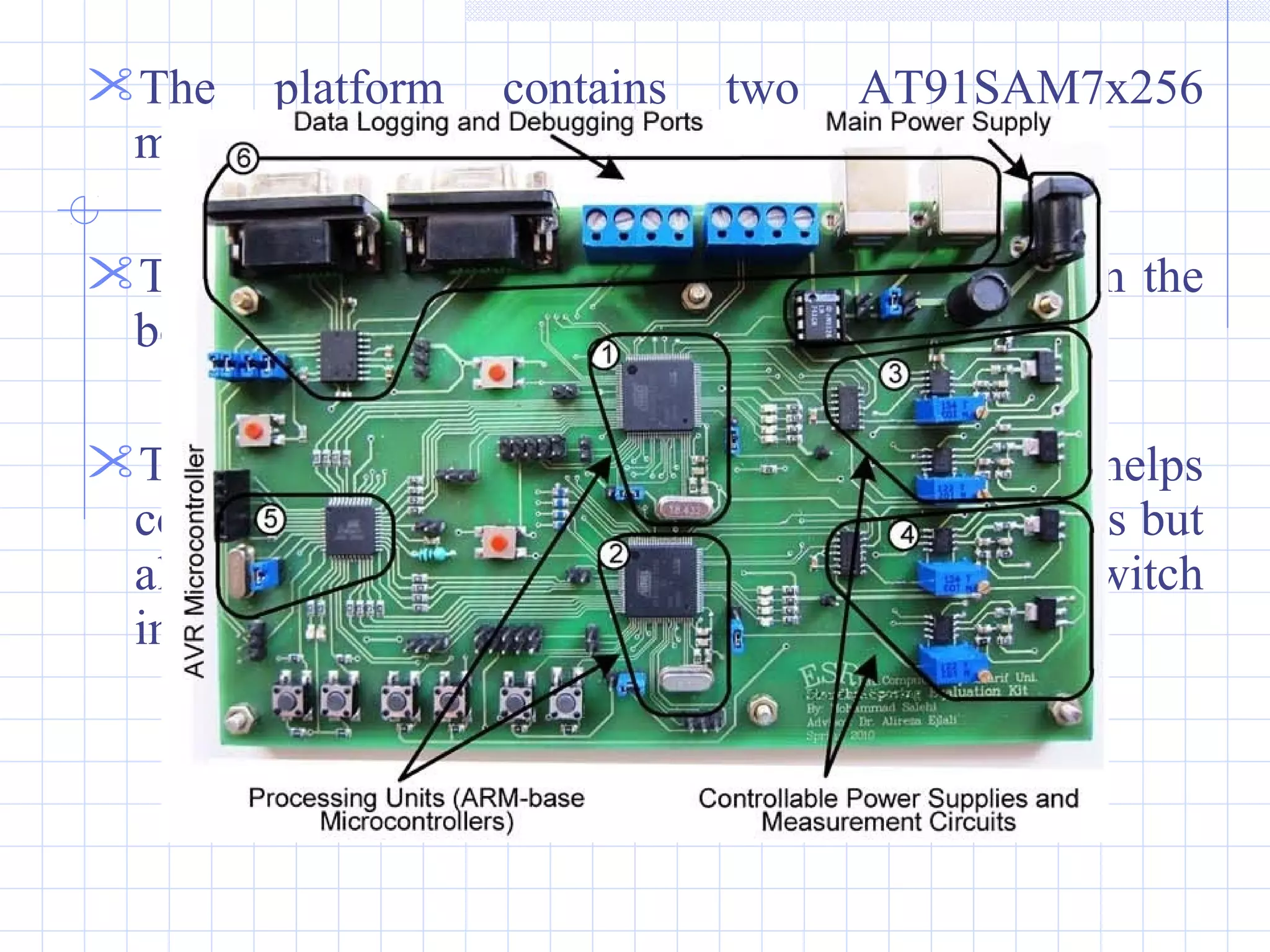

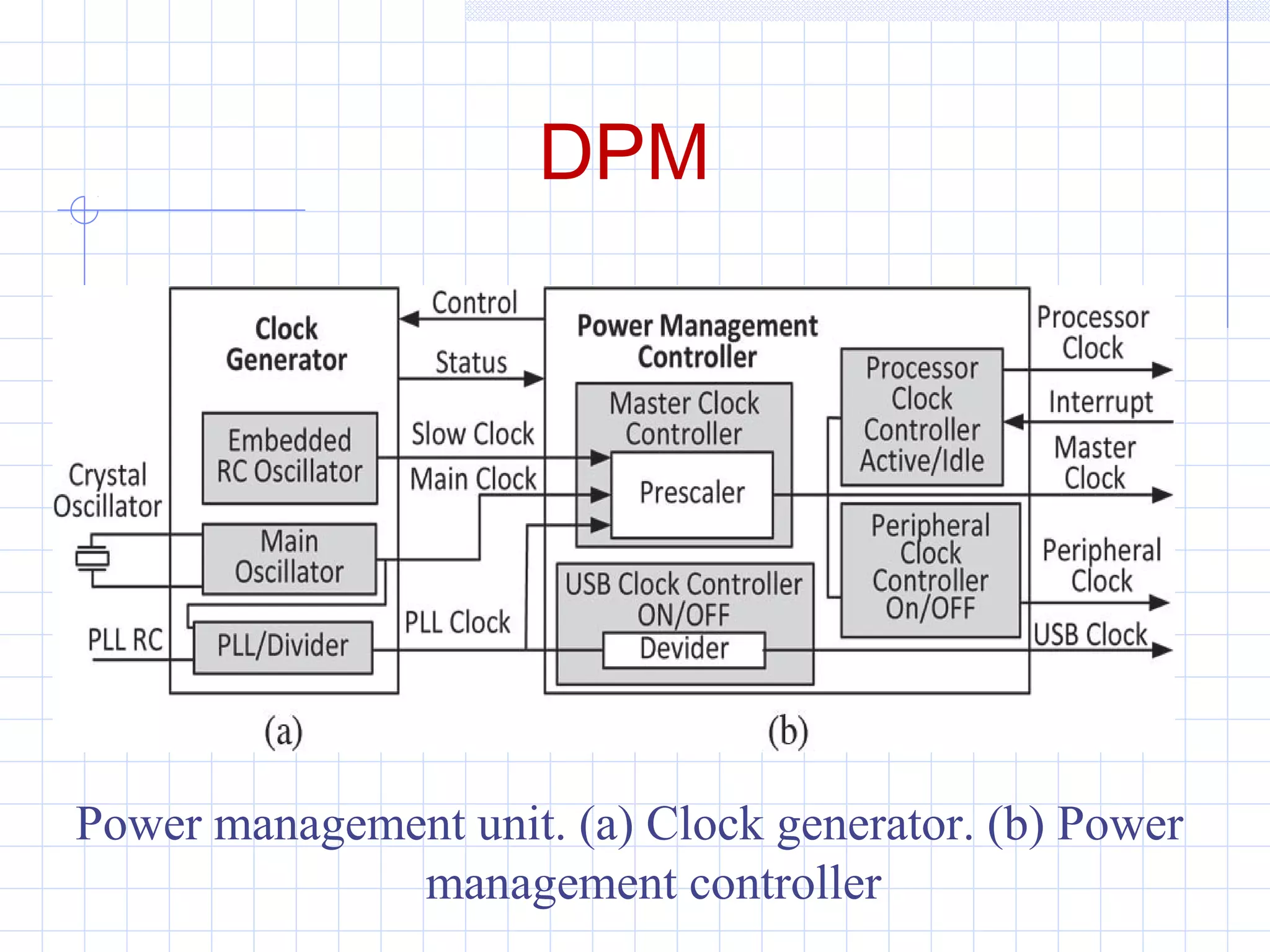

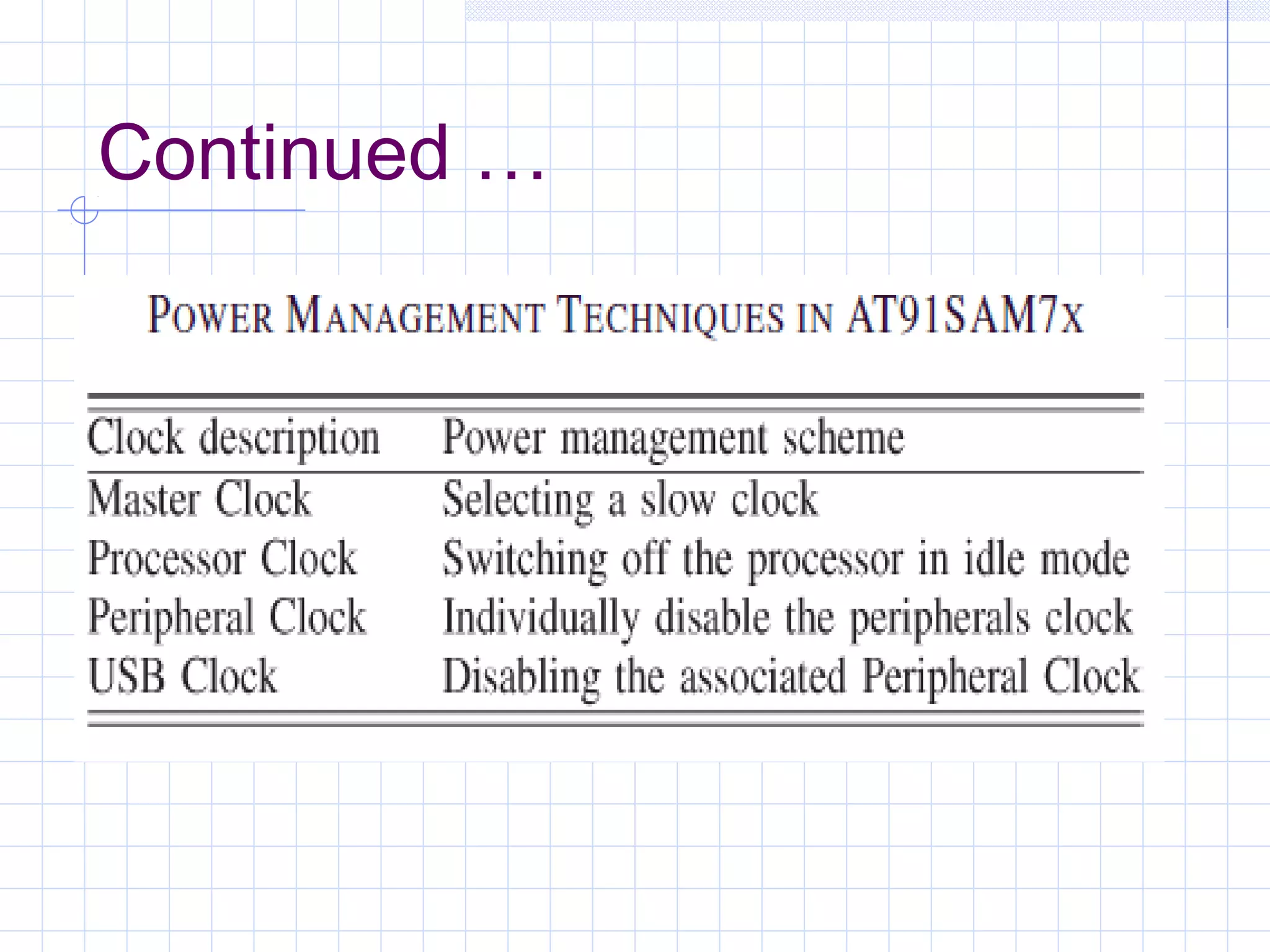

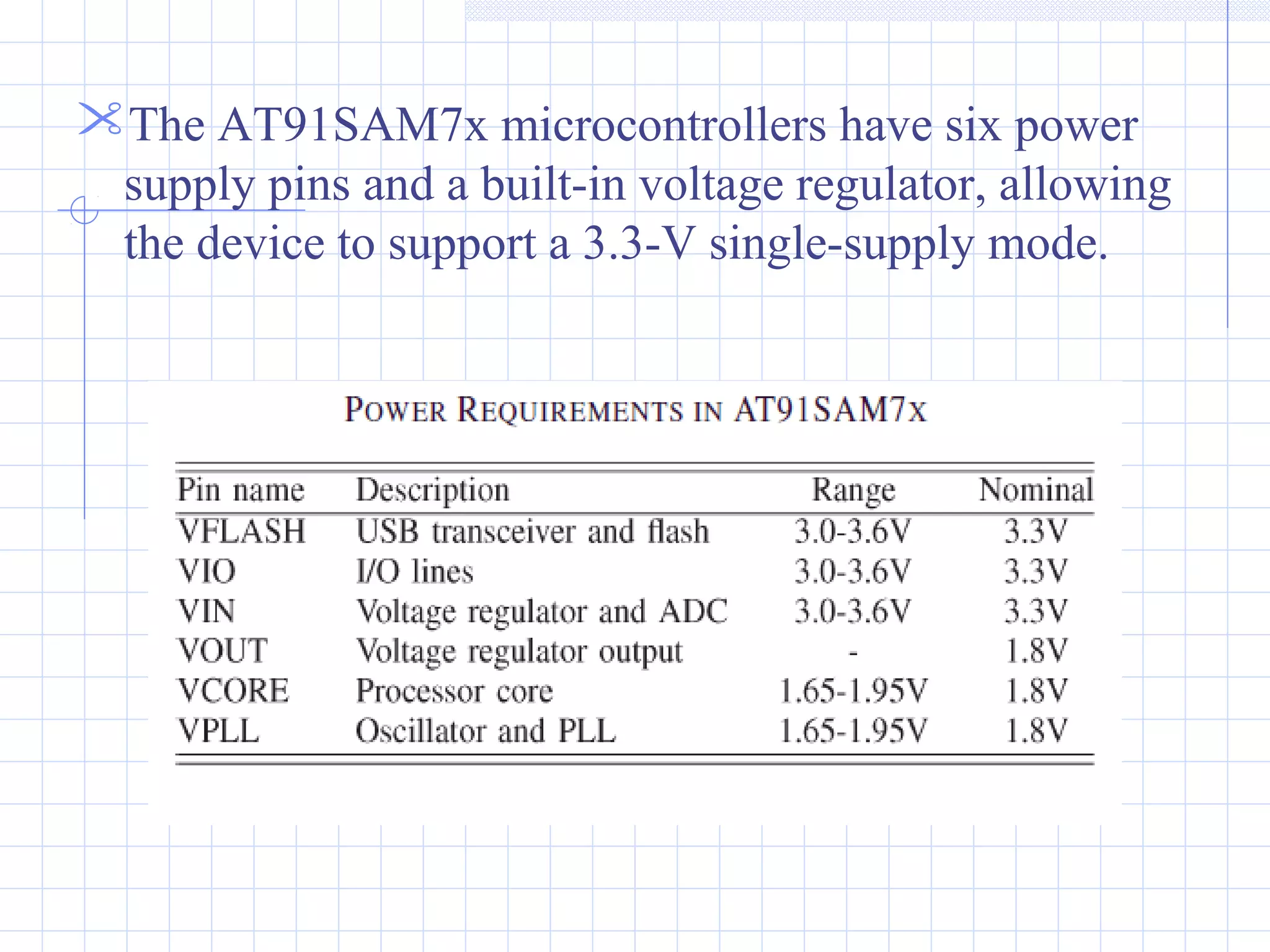

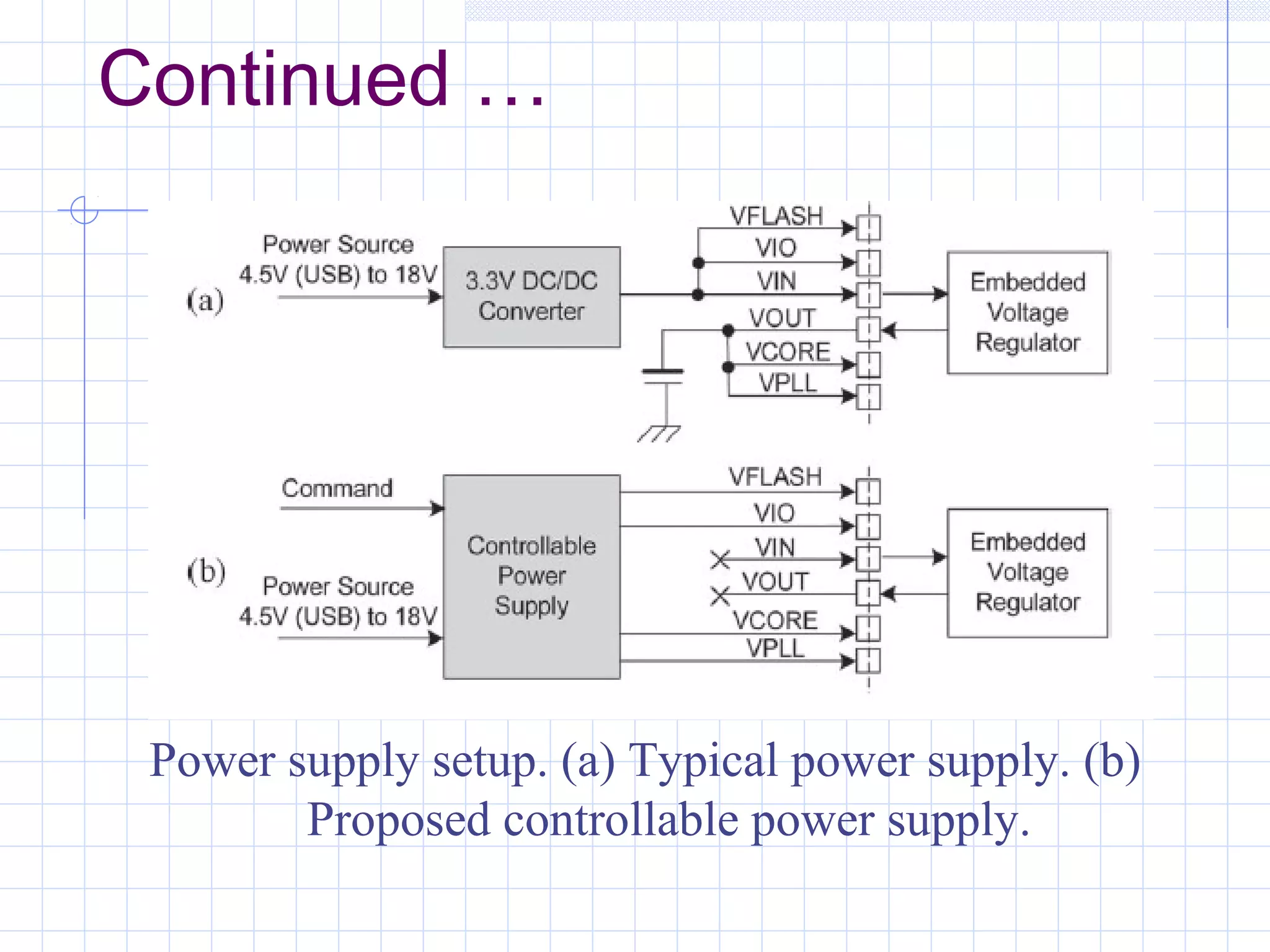

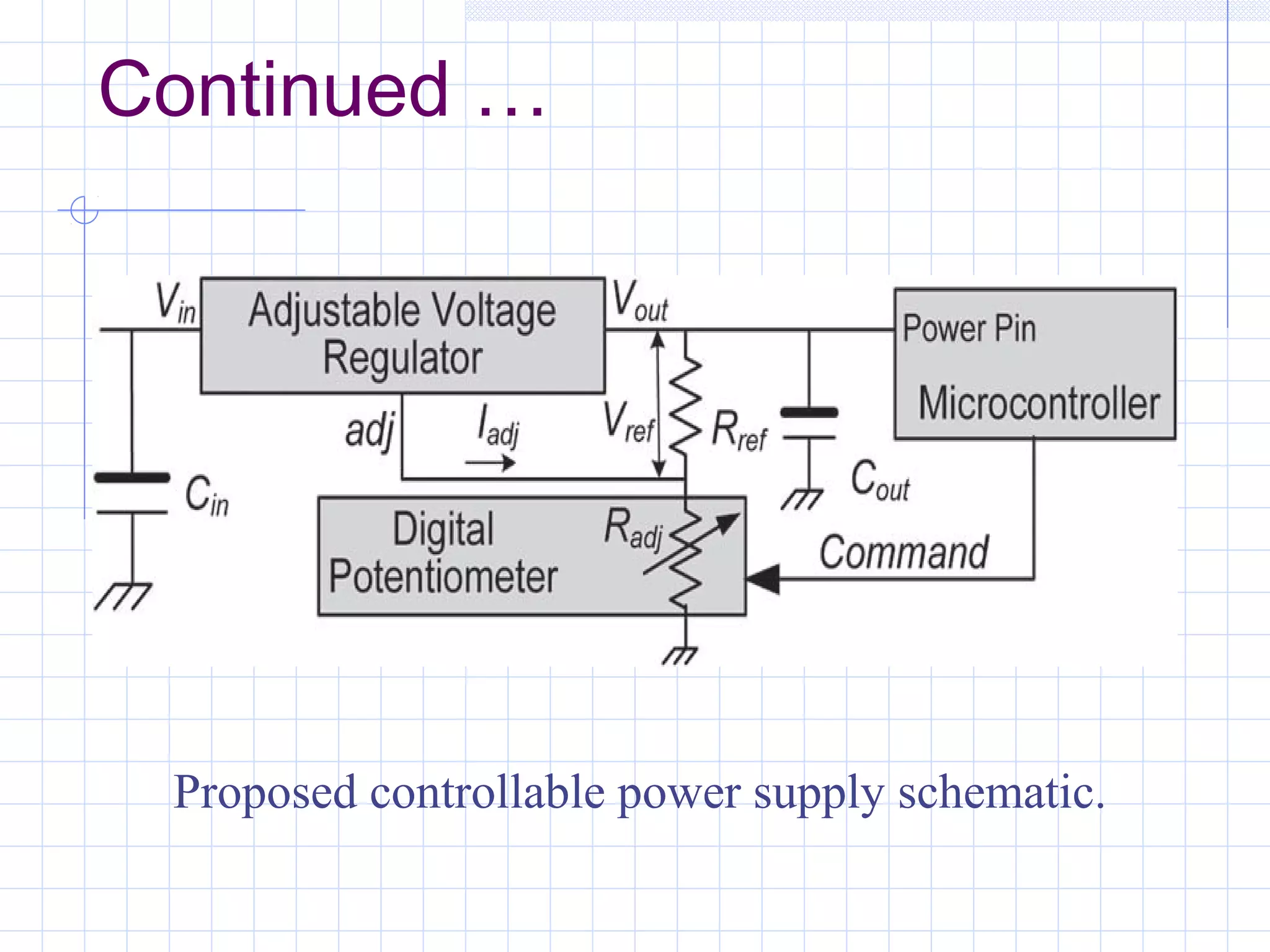

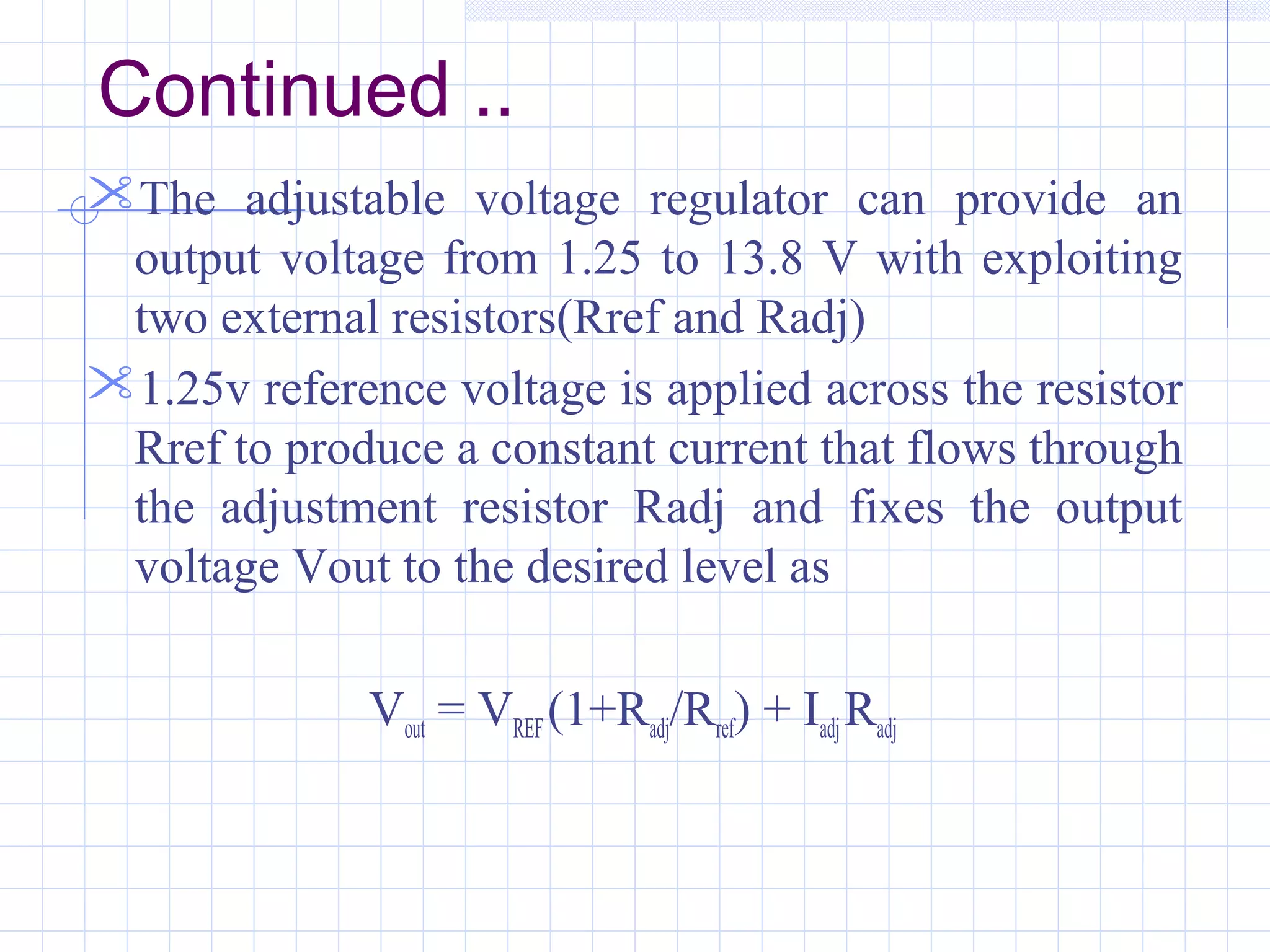

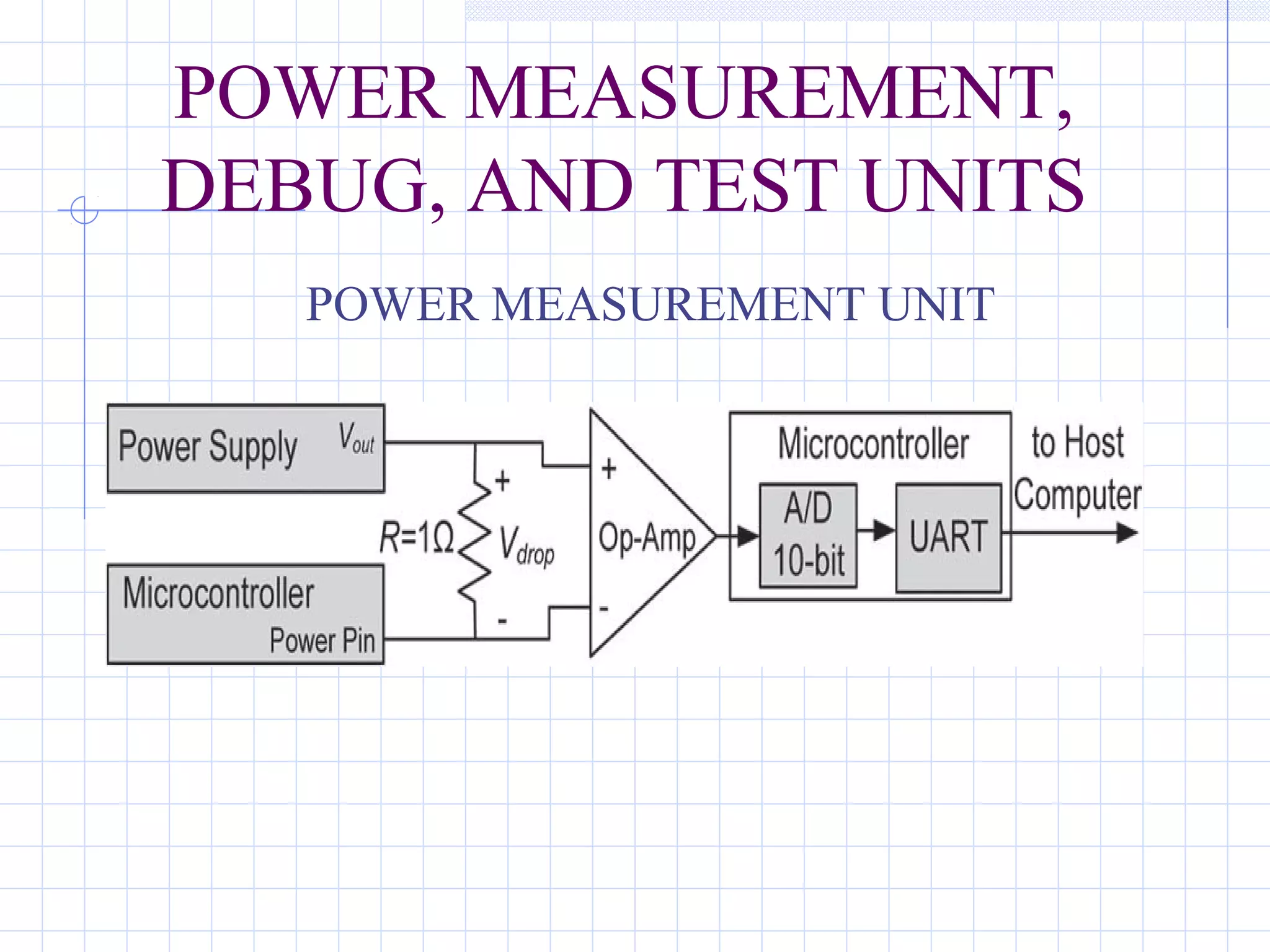

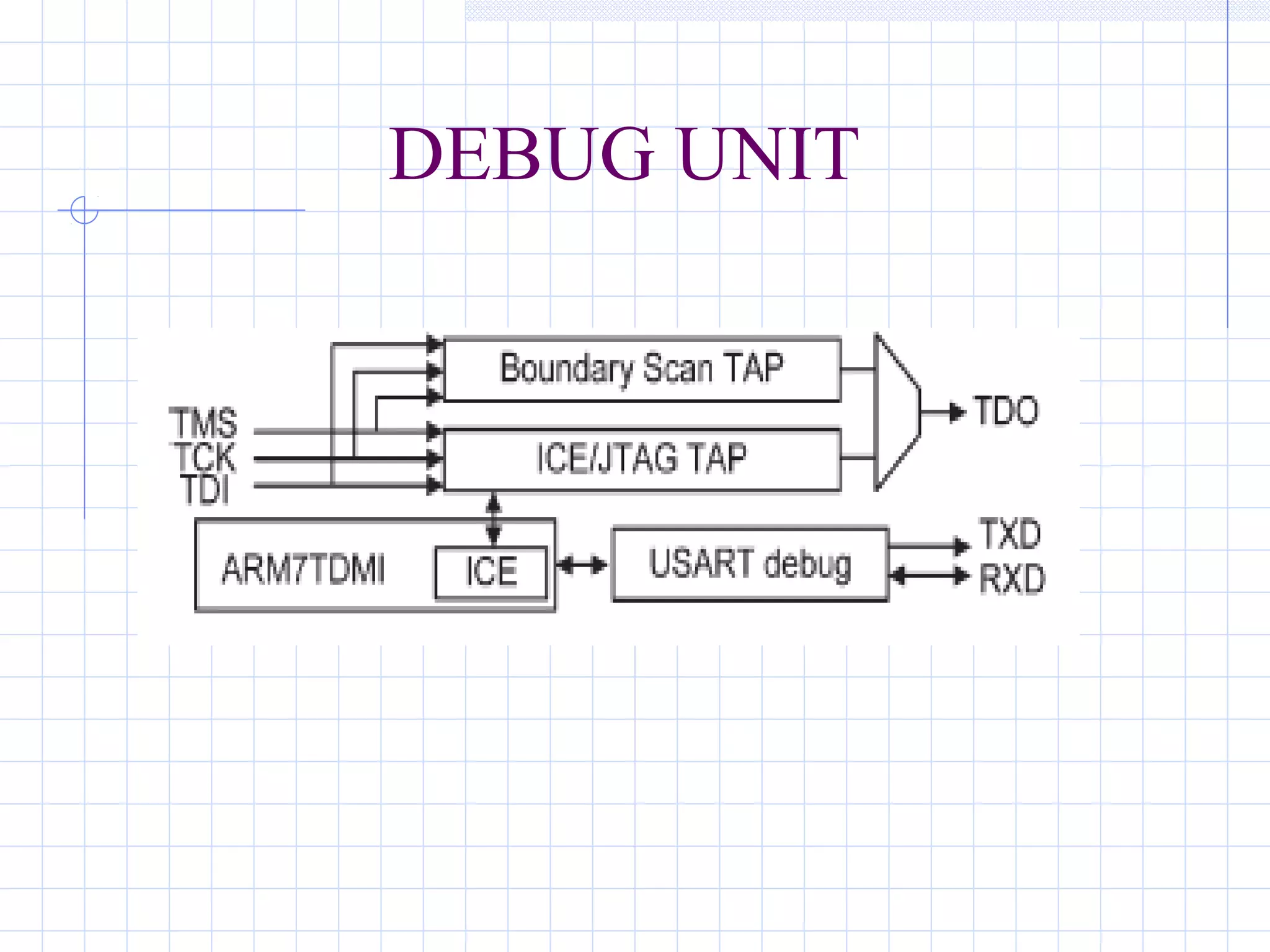

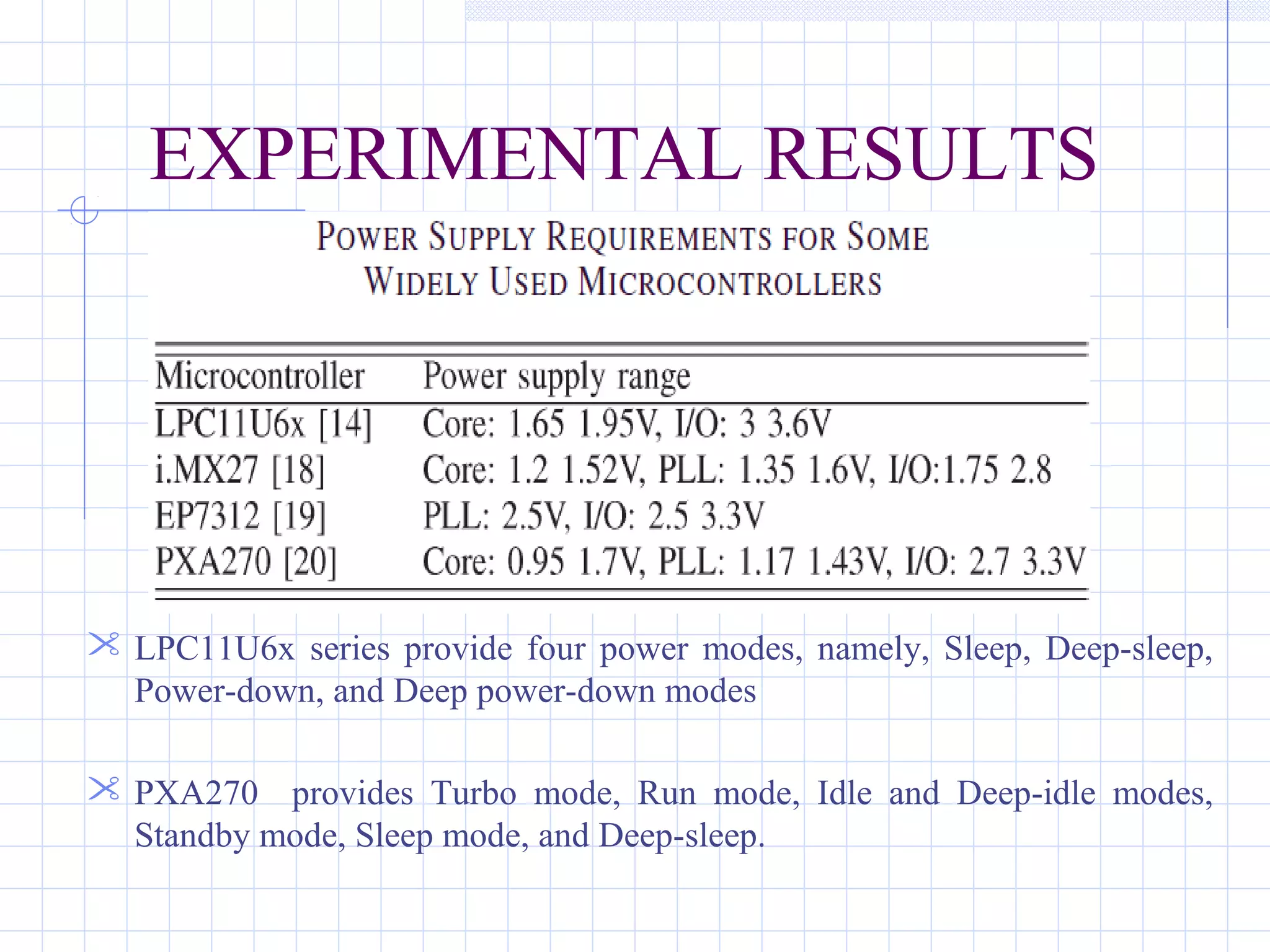

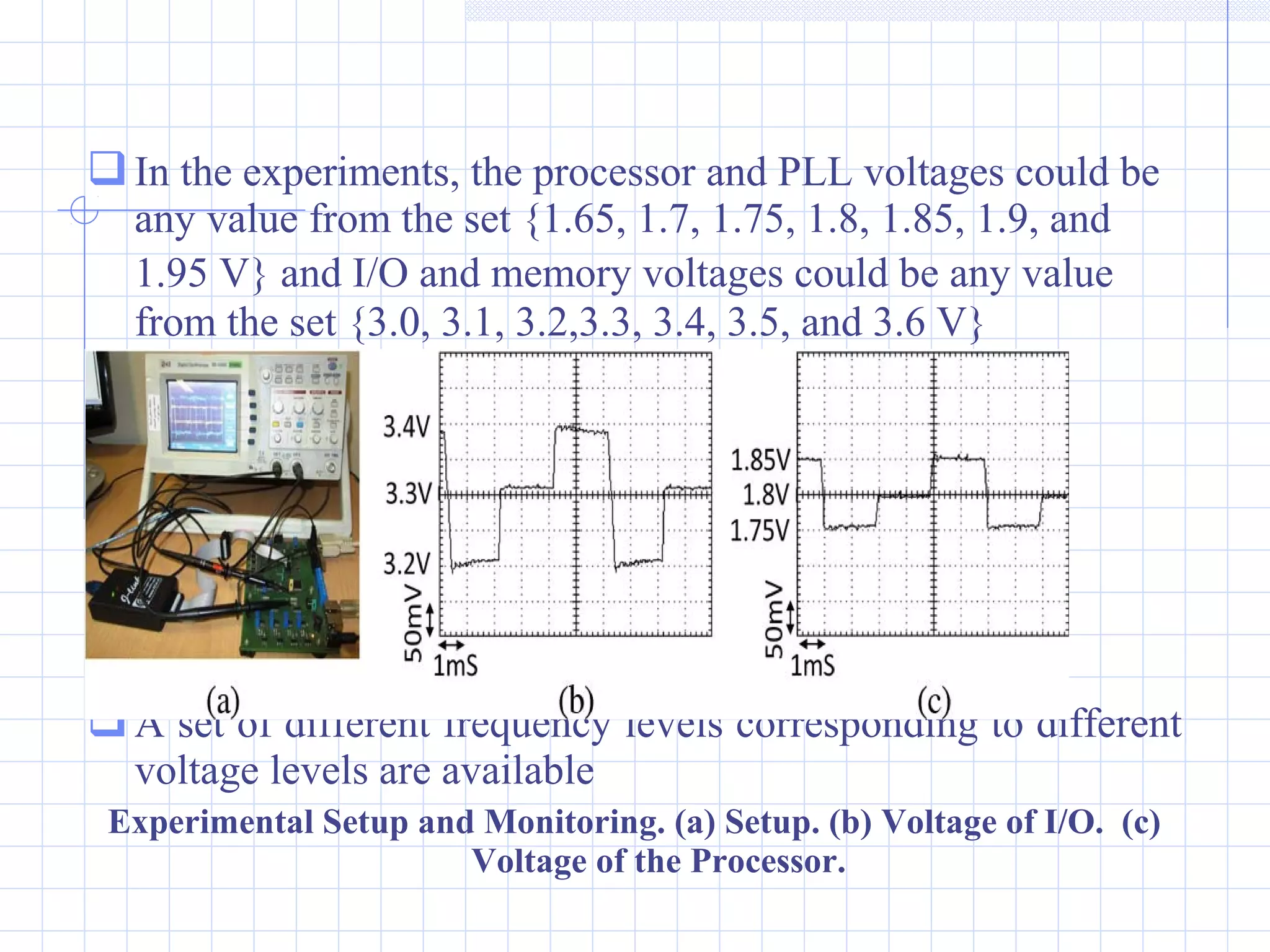

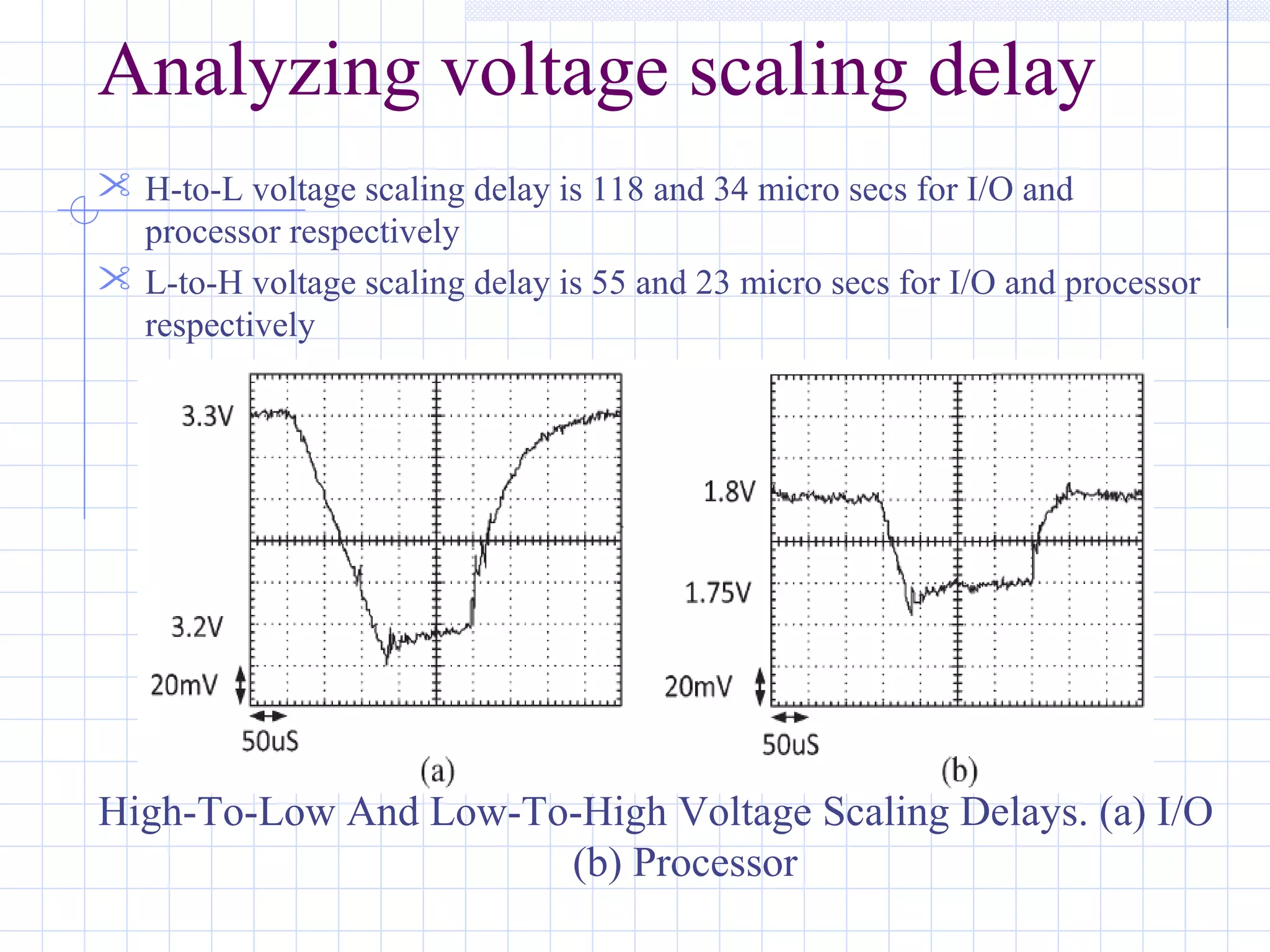

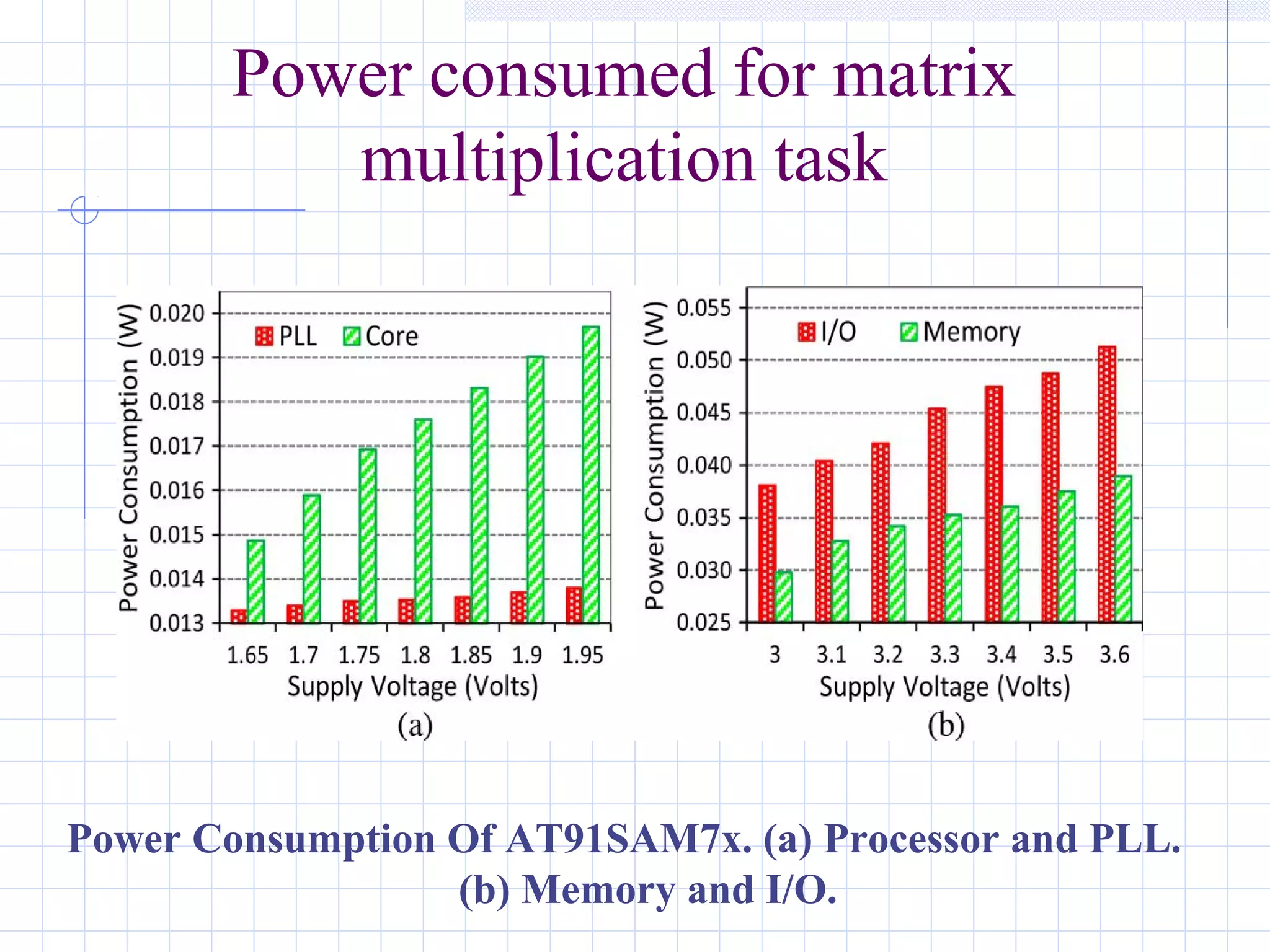

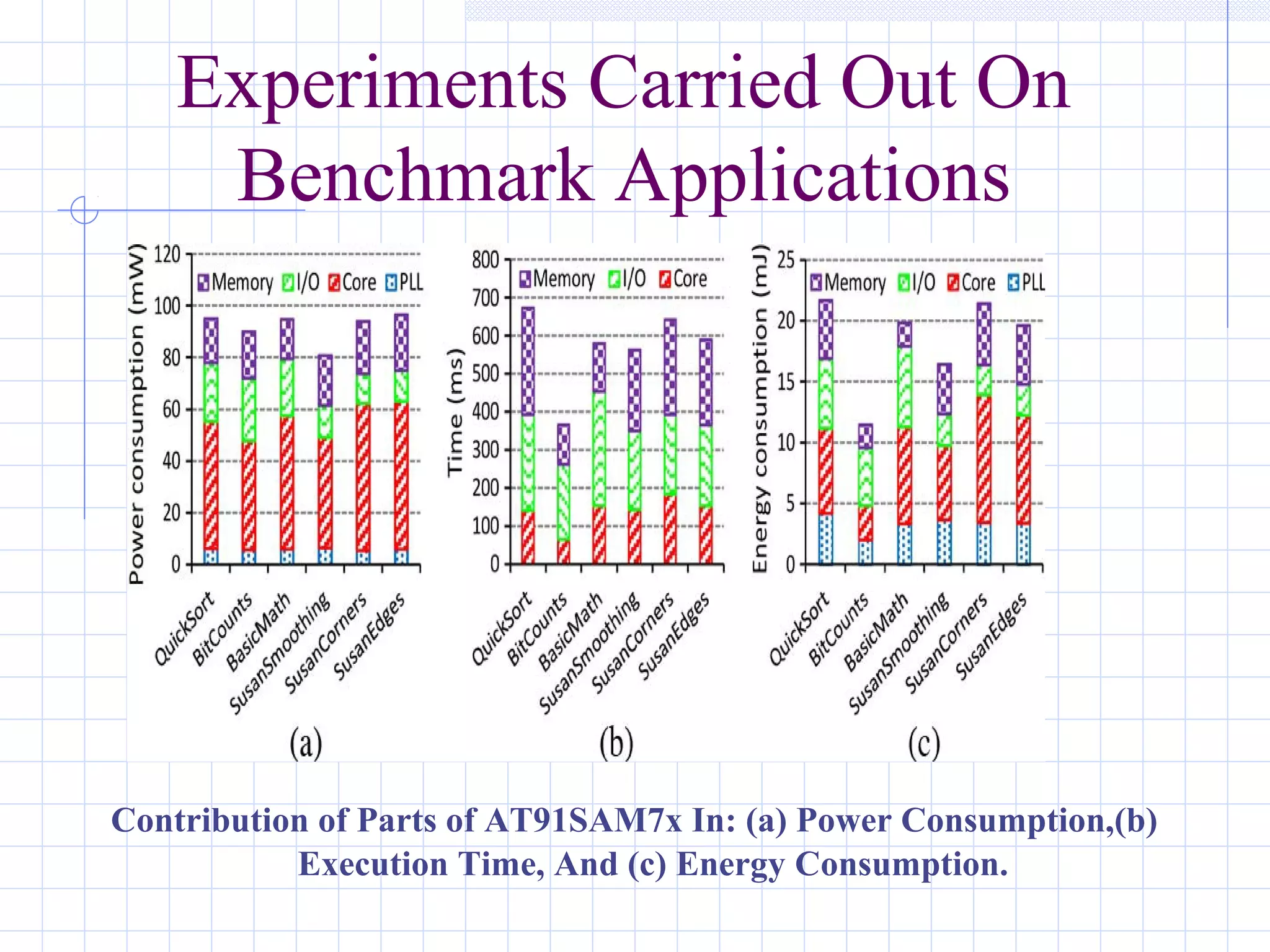

This document describes a hardware platform for evaluating low-energy multiprocessor embedded systems using commercial off-the-shelf devices. The platform uses two ARM7 microcontrollers that can each be powered independently and have their voltage and frequency scaled dynamically. It includes circuits to separately measure the energy and power consumption of different components. Experimental results show the delay and energy impacts of voltage scaling on various parts. The platform is intended to support research on energy management techniques for parallel processing systems.