Poster digital-070624

•

1 like•283 views

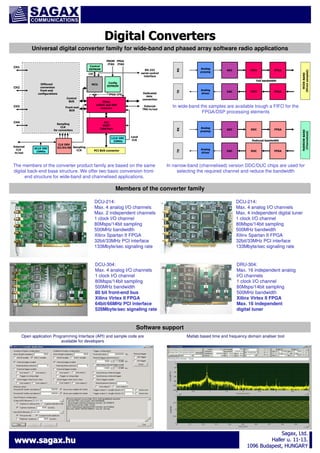

This document summarizes a universal digital converter family for software radio applications. It offers two front-end configurations: wide-band direct sampling and narrow-band channelized. In wide-band mode, samples are available through a FIFO for FPGA/DSP processing. In narrow-band mode, DDC/DUC chips are used to select channels and reduce bandwidth. The family includes products with up to 4 or 16 channels that sample at 80Msps with 14-bit resolution and 500MHz bandwidth, and interface with FPGAs and PCI buses. Open APIs and sample code are provided for developers.

Report

Share

Report

Share

Download to read offline

Recommended

More Related Content

What's hot

What's hot (20)

Basic Study on the WT12 Family of Bluetooth Devices

Basic Study on the WT12 Family of Bluetooth Devices

Similar to Poster digital-070624

This session includes a discussion on rapid prototyping concepts using Xilinx All Programmable FPGAs and SoCs with Analog Devices high speed and precision products. Covered in this session will be common use cases for Xilinx devices in DSP applications that interface to high speed analog. An overview will be provided of how Xilinx accelerates development with DSP platforms that can be used to quickly evaluate and prototype systems that include high speed analog, programmable logic, and embedded processing. Also covered will be an introduction to Xilinx’s new Vivado Design Suite development environment that shortens design cycles by providing an IP centric design flow, easy to use design analysis and debug, and high level design flows supporting C/C++ and MATLAB/Simulink.High Performance DSP with Xilinx All Programmable Devices (Design Conference ...

High Performance DSP with Xilinx All Programmable Devices (Design Conference ...Analog Devices, Inc.

Various approaches have been developed for integrating FPGA and GPP application components in a Software Communications Architecture (SCA) radio. Most of these have been less than successful, primarily due to overhead, latency and/or maintainability issues. Spectra IP Core is a second-generation solution to FPGA-GPP component integration that provides a low-latency, standards-based CORBA protocol with excellent performance metrics and the robustness of a proven, deployed solution. Building on PrismTech’s ICO v1, Spectra IP Core is a second-generation COTS product. This webcast will introduce the Spectra IP Core architecture, its main functions and its performance benchmarks. Although FPGA ‘middleware’ is a new concept for many FPGA developers, the capabilities provided by Spectra IP Core not only provide valuable integration ‘hooks’, but also help support a highly-efficient, proven radio component that simplifies the integration of high-level software development with digital design and accelerates the development of SCA-compliant FPGA components for SCA radios. These slides will be of great interest and value to project managers, systems engineers and architects as well as software and digital engineers involved in designing, building and testing SCA-compliant SDRs.Spectra IP Core ORB - high-performance, low-latency solution for FPGA-GPP com...

Spectra IP Core ORB - high-performance, low-latency solution for FPGA-GPP com...ADLINK Technology IoT

Similar to Poster digital-070624 (20)

The FlexTiles Development Platform offers Dual FPGA for 3D SoC Prototyping

The FlexTiles Development Platform offers Dual FPGA for 3D SoC Prototyping

High Performance DSP with Xilinx All Programmable Devices (Design Conference ...

High Performance DSP with Xilinx All Programmable Devices (Design Conference ...

Spectra IP Core ORB - high-performance, low-latency solution for FPGA-GPP com...

Spectra IP Core ORB - high-performance, low-latency solution for FPGA-GPP com...

Introducing OMAP-L138/AM1808 Processor Architecture and Hawkboard Peripherals

Introducing OMAP-L138/AM1808 Processor Architecture and Hawkboard Peripherals

DESIGN CHOICES FOR EMBEDDED REAL-TIME CONTROL SYSTEMS @ 4th FPGA Camp

DESIGN CHOICES FOR EMBEDDED REAL-TIME CONTROL SYSTEMS @ 4th FPGA Camp

[HES2014] HackRF A Low Cost Software Defined Radio Platform by Benjamin Vernoux![[HES2014] HackRF A Low Cost Software Defined Radio Platform by Benjamin Vernoux](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

![[HES2014] HackRF A Low Cost Software Defined Radio Platform by Benjamin Vernoux](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

[HES2014] HackRF A Low Cost Software Defined Radio Platform by Benjamin Vernoux

More from Bertalan EGED

More from Bertalan EGED (20)

Recently uploaded

Recently uploaded (20)

08448380779 Call Girls In Friends Colony Women Seeking Men

08448380779 Call Girls In Friends Colony Women Seeking Men

Factors to Consider When Choosing Accounts Payable Services Providers.pptx

Factors to Consider When Choosing Accounts Payable Services Providers.pptx

Advantages of Hiring UIUX Design Service Providers for Your Business

Advantages of Hiring UIUX Design Service Providers for Your Business

08448380779 Call Girls In Diplomatic Enclave Women Seeking Men

08448380779 Call Girls In Diplomatic Enclave Women Seeking Men

Boost PC performance: How more available memory can improve productivity

Boost PC performance: How more available memory can improve productivity

TrustArc Webinar - Stay Ahead of US State Data Privacy Law Developments

TrustArc Webinar - Stay Ahead of US State Data Privacy Law Developments

Boost Fertility New Invention Ups Success Rates.pdf

Boost Fertility New Invention Ups Success Rates.pdf

How to Troubleshoot Apps for the Modern Connected Worker

How to Troubleshoot Apps for the Modern Connected Worker

08448380779 Call Girls In Civil Lines Women Seeking Men

08448380779 Call Girls In Civil Lines Women Seeking Men

The Codex of Business Writing Software for Real-World Solutions 2.pptx

The Codex of Business Writing Software for Real-World Solutions 2.pptx

Presentation on how to chat with PDF using ChatGPT code interpreter

Presentation on how to chat with PDF using ChatGPT code interpreter

Poster digital-070624

- 1. Digital Converters Universal digital converter family for wide-band and phased array software radio applications Front-end BUS CH4 Sampling CLK for converters FPGA LOGIC and DSP resource SCLK OSC 10MHz CLK DRV X2/X4/X8 Sampling CLK External TRG in/out PCI HOST Interface LCLK OSC 33MHz External CLK in/out Dedicated data connection FPGA Analog driver DAC Analog preamp ADC Local CLK PCI BUS connector The members of the converter product family are based on the same digital back-end base structure. We offer two basic conversion frontend structure for wide-band and channelised applications. FIFO FPGA In wide-band the samples are available trough a FIFO for the FPGA/DSP processing elements RX CH3 FIFO Full bandwidth FPGA CFG Control BUS ADC Config EEPROM DDC FPGA Reduced bandwidth TX CH2 MCU TX Different conversion front-end configurations Analog preamp Analog driver DAC DUC FPGA NARROW-BAND (Channelized) RS-232 serial control interface I2C WIDE-BAND (Direct sampled) PROM FPGA JTAG JTAG RX Control EEPROM CH1 In narrow-band (channelised) version DDC/DUC chips are used for selecting the required channel and reduce the bandwidth Members of the converter family DCU-214: DCUMax. 4 analog I/O channels Max. 2 independent channels 1 clock I/O channel 80Msps/14bit sampling 500MHz bandwidth Xilinx Spartan II FPGA 32bit/33MHz PCI interface 133Mbyte/sec signaling rate DCU-214: DCUMax. 4 analog I/O channels Max. 4 independent digital tuner 1 clock I/O channel 80Msps/14bit sampling 500MHz bandwidth Xilinx Spartan II FPGA 32bit/33MHz PCI interface 133Mbyte/sec signaling rate DCU-304: DCUMax. 4 analog I/O channels 1 clock I/O channel 80Msps/14bit sampling 500MHz bandwidth 80 bit front-end bus frontXilinx Virtex II FPGA 64bit/66MHz PCI interface 528Mbyte/sec signaling rate DRU-304: DRUMax. 16 independent analog I/O channels 1 clock I/O channel 80Msps/14bit sampling 500MHz bandwidth Xilinx Virtex II FPGA Max. 16 independent digital tuner Software support Open application Programming Interface (API) and sample code are available for developers www.sagax.hu Matlab based time and frequency domain analiser tool Sagax, Ltd. Ltd. Haller u. 11-13. 111096 Budapest, HUNGARY