Internal memory

•Download as PPTX, PDF•

3 likes•2,178 views

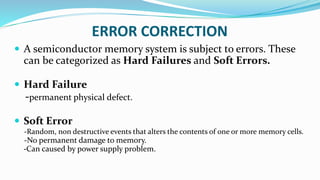

A semiconductor memory system can experience hard failures from permanent physical defects or soft errors from random, non-destructive events that change memory cell contents without permanent damage. Error correcting codes add redundant bits when data is stored to detect and possibly correct errors by regenerating codes when data is read out and comparing them. ECC memory can detect common internal data corruption to prevent data loss in applications where reliability is critical.

Report

Share

Report

Share

Recommended

Memory hierarchy

The document discusses the memory hierarchy in computer architecture. It describes the memory hierarchy as separating computer storage into different levels based on response time, with faster but smaller memory closer to the processor. The levels include internal processor registers and cache, main system RAM, online mass storage, and offline bulk storage. Designing for performance requires considering how data moves through this hierarchy and minimizing how far data must travel.

DDR2 SDRAM

This document summarizes the key aspects of a DDR2 SDRAM controller, including:

1) It describes the differences between DDR1 and DDR2 memory technologies, such as lower power consumption and higher data rates in DDR2.

2) It provides a block diagram of the main components and I/O signals of a DDR2 SDRAM controller.

3) It explains the basic functionality of a DDR2 SDRAM controller, including initialization, refresh operations, and read and write operations.

DMA operation

1. Direct Memory Access (DMA) allows input/output devices to directly access main memory, bypassing the CPU to speed up memory transfers. This is managed by a DMA controller.

2. During a DMA transfer, the DMA controller gains control of the address bus, data bus, and control bus from the microprocessor to transfer data directly between an I/O port and memory.

3. The DMA controller has several options for transferring data, including cycle stealing for single byte transfers, burst mode for block transfers using address sequencing, and hidden DMA which occurs transparently when the CPU is not using the bus.

Associative memory

An associative memory, or content-addressable memory (CAM), allows data to be stored and retrieved based on its content rather than its location. It consists of a memory array where each word is compared in parallel to search terms. Words that match set their corresponding bit in a match register. This allows the location of matching words to be identified very quickly. Associative memory is more expensive than random access memory but is useful when search time is critical. It is accessed simultaneously based on data content rather than a specific address.

Direct access memory

DMA stands for Direct memory access and is a method of transferring data from the computers RAM to another part of the computer without processing it using the CPU.

Assembly Language Basics

This document outlines the basics of assembly language, including basic elements, statements, program data, variables, constants, instructions, translation to assembly language, and program structure. It discusses statement syntax, valid names, operation and operand fields. It also covers common instructions like MOV, ADD, SUB, INC, DEC, and NEG. Finally, it discusses program segments, memory models, and how to define the data, stack, and code segments.

Memory organization

Memory organization

Memory Organization in Computer Architecture. A memory unit is the collection of storage units or devices together. The memory unit stores the binary information in the form of bits. ... Volatile Memory: This loses its data, when power is switched off.

Micro programmed control

presentation on micro programmed controlling.topic of somputer science architecture(csa) of sem 1 in delhi university.

Recommended

Memory hierarchy

The document discusses the memory hierarchy in computer architecture. It describes the memory hierarchy as separating computer storage into different levels based on response time, with faster but smaller memory closer to the processor. The levels include internal processor registers and cache, main system RAM, online mass storage, and offline bulk storage. Designing for performance requires considering how data moves through this hierarchy and minimizing how far data must travel.

DDR2 SDRAM

This document summarizes the key aspects of a DDR2 SDRAM controller, including:

1) It describes the differences between DDR1 and DDR2 memory technologies, such as lower power consumption and higher data rates in DDR2.

2) It provides a block diagram of the main components and I/O signals of a DDR2 SDRAM controller.

3) It explains the basic functionality of a DDR2 SDRAM controller, including initialization, refresh operations, and read and write operations.

DMA operation

1. Direct Memory Access (DMA) allows input/output devices to directly access main memory, bypassing the CPU to speed up memory transfers. This is managed by a DMA controller.

2. During a DMA transfer, the DMA controller gains control of the address bus, data bus, and control bus from the microprocessor to transfer data directly between an I/O port and memory.

3. The DMA controller has several options for transferring data, including cycle stealing for single byte transfers, burst mode for block transfers using address sequencing, and hidden DMA which occurs transparently when the CPU is not using the bus.

Associative memory

An associative memory, or content-addressable memory (CAM), allows data to be stored and retrieved based on its content rather than its location. It consists of a memory array where each word is compared in parallel to search terms. Words that match set their corresponding bit in a match register. This allows the location of matching words to be identified very quickly. Associative memory is more expensive than random access memory but is useful when search time is critical. It is accessed simultaneously based on data content rather than a specific address.

Direct access memory

DMA stands for Direct memory access and is a method of transferring data from the computers RAM to another part of the computer without processing it using the CPU.

Assembly Language Basics

This document outlines the basics of assembly language, including basic elements, statements, program data, variables, constants, instructions, translation to assembly language, and program structure. It discusses statement syntax, valid names, operation and operand fields. It also covers common instructions like MOV, ADD, SUB, INC, DEC, and NEG. Finally, it discusses program segments, memory models, and how to define the data, stack, and code segments.

Memory organization

Memory organization

Memory Organization in Computer Architecture. A memory unit is the collection of storage units or devices together. The memory unit stores the binary information in the form of bits. ... Volatile Memory: This loses its data, when power is switched off.

Micro programmed control

presentation on micro programmed controlling.topic of somputer science architecture(csa) of sem 1 in delhi university.

External memory - Computer Architecture

Magnetic disks remain the most important component of external memory. Data is recorded on disks through magnetic read and write heads. Disks are organized into tracks and sectors for efficient data access. RAID systems provide data redundancy or higher performance through striping and mirroring across multiple disks. Optical disks like CDs and DVDs store data through microscopic pits and lands read by lasers, and use constant linear velocity to increase storage capacity toward the disk edge.

Assembly level language

This document provides an overview of assembly language programming. It discusses what assembly language is, the advantages of using assembly language, how assemblers work to translate assembly code into machine code, the role of linkers in combining object files, and how debuggers can be used to debug assembly code. It also covers various assembly language directives like PROC, ENDP, CALL, RET, DB, DW, DD, and DS which are used to define procedures, call procedures, and reserve and initialize memory. The document concludes with a brief description of macros in assembly language.

Cache coherence ppt

This document discusses cache coherence in single and multiprocessor systems. It provides techniques to avoid inconsistencies between cache and main memory including write-through, write-back, and instruction caching. For multiprocessors, it discusses issues with sharing writable data, process migration, and I/O activity. Software solutions involve compiler and OS management while hardware uses coherence protocols like snoopy and directory protocols.

Active and main memory database

Active databases automatically respond to events inside or outside the system using rules. Main memory databases reside permanently in main memory for faster access than disk-based databases. Active databases support event detection and rule-based responses, while main memory databases have direct memory access without disk overhead. Both have applications in real-time systems where speed is critical.

Memory Management

This document provides an overview of memory management techniques in operating systems, including both static and dynamic allocation approaches. It discusses fixed and variable partitioning for static allocation, as well as first-fit, next-fit, best-fit, and worst-fit algorithms for dynamic allocation. The document also covers fragmentation, base-limit registers, swapping, paging, and segmentation for virtual memory management. The key aspects of paging include using page tables to map virtual to physical addresses, allowing sharing and abstracting physical organization. Segmentation divides memory into logical segments specified by segment tables.

Assembly language programming

This document presents information on assembly level programming. It discusses how assembly level programming uses mnemonics that are assembled into object code, making it less error-prone than machine level programming. It also outlines the programming tools used for assembly level programming, including editors, assemblers, linkers, loaders, and debuggers. Finally, it notes that assembly level programming is commonly used in embedded systems with limited resources.

Introduction to Assembly Language

The document discusses assembly language and its relationship to computer architecture and programming. It covers the different views of computer design including the programmer's view through instruction set architecture and the logic designer's view through machine organization. It also summarizes how a high-level language program is converted into executable files through compilation, assembly, and linking.

Direct Memory Access & Interrrupts

The document discusses direct memory access (DMA) and interrupts. It describes how DMA allows direct data transfer between memory and I/O devices without involving the CPU. This is handled by a DMA controller through a request-grant handshake using HOLD and HLDA pins. The document also categorizes different types of interrupts like hardware, software and exceptions. It explains how interrupts alter program flow and are serviced by interrupt service routines (ISRs) through an interrupt vector table.

Memory Addressing

This document discusses computer architecture concepts such as machine language, assembly language, and instruction set architecture. It then describes different addressing architectures including memory-to-memory, register-to-register, and register-memory. Various addressing modes are also defined, such as implied, immediate, indirect, relative, and indexed addressing modes. Finally, the document briefly discusses stack instructions and the use of a stack pointer register.

I/O System

The document discusses input/output (I/O) processing and the role of the operating system in managing I/O operations and devices. It covers I/O hardware components like ports, buses, and controllers. It also describes the different models for interaction between I/O controllers and CPUs, including polling, interrupts, and direct memory access (DMA). Finally, it discusses I/O application interfaces and blocking vs non-blocking I/O.

Computer architecture input output organization

Computer Architecture Input Output Organization seminar

Mustansiriya University

Department of Education

Computer Science

Computer Organization : CPU, Memory and I/O organization

This document provides information on CPU, memory, and I/O organization. It begins with an overview of the main components of a computer including the processor unit, memory unit, and input/output unit. It then describes the CPU in more detail including the arithmetic logic unit, control unit, and CPU block diagram. The document discusses the system bus and its various lines. It also covers CPU registers, instruction cycles, and status and control flags. The document provides an overview of instruction set architecture and compares RISC and CISC processor designs.

Assemblers

This document discusses assembly language and assemblers. It begins by explaining that assembly language provides a more readable and convenient way to program compared to machine language. It then describes how an assembler works, translating assembly language programs into machine code. The elements of assembly language are defined, including mnemonic operation codes, symbolic operands, and data declarations. The document also covers instruction formats, sample assembly language programs, and the processing an assembler performs to generate machine code from assembly code.

PCI BUS

The PCI bus is a local computer bus standard used to connect hardware devices inside a computer. It was developed in the early 1990s to standardize how expansion cards connected to the motherboard. Key features of PCI include plug and play capability, configuration ROMs that store device information, and interrupt request lines. During initialization, the configuration software reads the ROM on each device to determine its type and assign resources like addresses and interrupts.

Micro program example

This document summarizes the key components of a microprogrammed computer system, including the control memory, registers, instruction format, microinstruction format, and microoperations. It provides details on how a microprogram is used to define the bit values for each of the 128 words in the control memory to implement routines for instructions like fetch, decode, and execution. The symbolic microprogram needs to be translated to binary for storage in the control memory.

Ram and-rom-chips

RAM is the main memory that allows bidirectional transfer of data via its data bus. It has a capacity of 128 bytes addressed by a 7-bit address. ROM can only read and can store more data than RAM in the same size chip. A memory address map assigns addresses to RAM and ROM chips. RAM uses address lines 1-7 and is selected by address lines 8-9 through a decoder. ROM uses address lines 1-9 and is selected by address line 10.

memory and storage devices

1. The document discusses different types of computer memory and storage devices. It describes RAM, ROM, SRAM, and DRAM memory types and how RAM is used for temporary data storage.

2. Storage devices discussed include floppy disks, hard disks, magnetic tape, CDs, DVDs, and other optical discs. Floppy disks contain flexible plastic disks and were used to transfer small amounts of data between computers.

3. Hard disks differ in that they contain rigid metal platters that spin faster than floppy disks and are sealed inside the computer. Magnetic tape is cheaper for storing files and documents and transferring information between computers.

Components of ddbms

Components of DDBMS, Computer workstations or remote devices,Network hardware and software components,Communications media,transaction processor (TP), data processor (DP),

Types of Addressing modes- COA

Addressing mode is the way of addressing a memory location in instruction. Microcontroller needs data or operands on which the operation is to be performed. The method of specifying source of operand and output of result in an instruction is known as addressing mode.

There are various methods of giving source and destination address in instruction, thus there are various types of Addressing Modes. Here you will find the different types of Addressing Modes that are supported in Micro Controller 8051. Types of Addressing Modes are explained below:

1.Register Addressing Mode

2.Direct Addressing Mode

3.Register Indirect Addressing Mode

4.Immediate Addressing Mode

5.Index Addressing Mode

Explanation:

Register Addressing Mode: In this addressing mode, the source of data or destination of result is Register. In this type of addressing mode the name of the register is given in the instruction where the data to be read or result is to be stored.

Example: ADD A, R5 ( The instruction will do the addition of data in Accumulator with data in register R5)

Direct Addressing Mode: In this type of Addressing Mode, the address of data to be read is directly given in the instruction. In case, for storing result the address given in instruction is used to store the result.

Example: MOV A, 46H ( This instruction will move the contents of memory location 46H to Accumulator)

Register Indirect Addressing Mode: In Register Indirect Addressing Mode, as its name suggests the data is read or stored in register indirectly. That is, we provide the register in the instruction, in which the address of the other register is stored or which points to other register where data is stored or to be stored.

Example: MOV A, @R0 ( This instruction will move the data to accumulator from the register whose address is stored in register R0 ).

Also Read: Architecture Of 8051

Immediate Addressing Mode : In Immediate Addressing Mode , the data immediately follows the instruction. This means that data to be used is already given in the instruction itself.

Example: MOV A, #25H ( This instruction will move the data 25H to Accumulator. The # sign shows that preceding term is data, not the address.)

Index Addressing Mode: Offset is added to the base index register to form the effective address if the memory location.This Addressing Mode is used for reading lookup tables in Program Memory. The Address of the exact location of the table is formed by adding the Accumulator Data to the base pointer.

Example: MOVC, @A+DPTR ( This instruction will move the data from the memory to Accumulator; the address is made by adding the contents of Accumulator and Data Pointer.

Input & Output

The document discusses input and output in computer systems. It describes three main techniques for transferring data between the CPU and I/O devices: programmed I/O, interrupt-driven I/O, and direct memory access (DMA). Programmed I/O involves the CPU continuously polling I/O devices, interrupt-driven I/O uses interrupts to signal the CPU when data is ready, and DMA allows high-speed transfer of data directly between memory and I/O devices without CPU involvement.

Internal memory

A computer uses a hierarchy of internal and external memory systems. Internal memory includes RAM, ROM, and cache, which provide fast access but are more expensive per byte. RAM allows independent access to each memory location and is used for main memory. ROM permanently stores data and is used for boot programs. Cached memory uses SRAM for faster access than RAM. External memory includes hard disks and USB drives, which provide large, inexpensive storage but are much slower to access.

05 internal memory

1. The document discusses different types of semiconductor memory including RAM, ROM, PROM, EPROM, EEPROM, and flash memory.

2. It describes the operation and structure of both dynamic RAM (DRAM) and static RAM (SRAM). DRAM uses capacitors to store bits and requires refreshing, while SRAM uses flip-flops and does not require refreshing.

3. The document also covers various RAM technologies including synchronous DRAM (SDRAM), double data rate SDRAM (DDR SDRAM), Rambus DRAM (RDRAM), error correction codes, and cache DRAM.

More Related Content

What's hot

External memory - Computer Architecture

Magnetic disks remain the most important component of external memory. Data is recorded on disks through magnetic read and write heads. Disks are organized into tracks and sectors for efficient data access. RAID systems provide data redundancy or higher performance through striping and mirroring across multiple disks. Optical disks like CDs and DVDs store data through microscopic pits and lands read by lasers, and use constant linear velocity to increase storage capacity toward the disk edge.

Assembly level language

This document provides an overview of assembly language programming. It discusses what assembly language is, the advantages of using assembly language, how assemblers work to translate assembly code into machine code, the role of linkers in combining object files, and how debuggers can be used to debug assembly code. It also covers various assembly language directives like PROC, ENDP, CALL, RET, DB, DW, DD, and DS which are used to define procedures, call procedures, and reserve and initialize memory. The document concludes with a brief description of macros in assembly language.

Cache coherence ppt

This document discusses cache coherence in single and multiprocessor systems. It provides techniques to avoid inconsistencies between cache and main memory including write-through, write-back, and instruction caching. For multiprocessors, it discusses issues with sharing writable data, process migration, and I/O activity. Software solutions involve compiler and OS management while hardware uses coherence protocols like snoopy and directory protocols.

Active and main memory database

Active databases automatically respond to events inside or outside the system using rules. Main memory databases reside permanently in main memory for faster access than disk-based databases. Active databases support event detection and rule-based responses, while main memory databases have direct memory access without disk overhead. Both have applications in real-time systems where speed is critical.

Memory Management

This document provides an overview of memory management techniques in operating systems, including both static and dynamic allocation approaches. It discusses fixed and variable partitioning for static allocation, as well as first-fit, next-fit, best-fit, and worst-fit algorithms for dynamic allocation. The document also covers fragmentation, base-limit registers, swapping, paging, and segmentation for virtual memory management. The key aspects of paging include using page tables to map virtual to physical addresses, allowing sharing and abstracting physical organization. Segmentation divides memory into logical segments specified by segment tables.

Assembly language programming

This document presents information on assembly level programming. It discusses how assembly level programming uses mnemonics that are assembled into object code, making it less error-prone than machine level programming. It also outlines the programming tools used for assembly level programming, including editors, assemblers, linkers, loaders, and debuggers. Finally, it notes that assembly level programming is commonly used in embedded systems with limited resources.

Introduction to Assembly Language

The document discusses assembly language and its relationship to computer architecture and programming. It covers the different views of computer design including the programmer's view through instruction set architecture and the logic designer's view through machine organization. It also summarizes how a high-level language program is converted into executable files through compilation, assembly, and linking.

Direct Memory Access & Interrrupts

The document discusses direct memory access (DMA) and interrupts. It describes how DMA allows direct data transfer between memory and I/O devices without involving the CPU. This is handled by a DMA controller through a request-grant handshake using HOLD and HLDA pins. The document also categorizes different types of interrupts like hardware, software and exceptions. It explains how interrupts alter program flow and are serviced by interrupt service routines (ISRs) through an interrupt vector table.

Memory Addressing

This document discusses computer architecture concepts such as machine language, assembly language, and instruction set architecture. It then describes different addressing architectures including memory-to-memory, register-to-register, and register-memory. Various addressing modes are also defined, such as implied, immediate, indirect, relative, and indexed addressing modes. Finally, the document briefly discusses stack instructions and the use of a stack pointer register.

I/O System

The document discusses input/output (I/O) processing and the role of the operating system in managing I/O operations and devices. It covers I/O hardware components like ports, buses, and controllers. It also describes the different models for interaction between I/O controllers and CPUs, including polling, interrupts, and direct memory access (DMA). Finally, it discusses I/O application interfaces and blocking vs non-blocking I/O.

Computer architecture input output organization

Computer Architecture Input Output Organization seminar

Mustansiriya University

Department of Education

Computer Science

Computer Organization : CPU, Memory and I/O organization

This document provides information on CPU, memory, and I/O organization. It begins with an overview of the main components of a computer including the processor unit, memory unit, and input/output unit. It then describes the CPU in more detail including the arithmetic logic unit, control unit, and CPU block diagram. The document discusses the system bus and its various lines. It also covers CPU registers, instruction cycles, and status and control flags. The document provides an overview of instruction set architecture and compares RISC and CISC processor designs.

Assemblers

This document discusses assembly language and assemblers. It begins by explaining that assembly language provides a more readable and convenient way to program compared to machine language. It then describes how an assembler works, translating assembly language programs into machine code. The elements of assembly language are defined, including mnemonic operation codes, symbolic operands, and data declarations. The document also covers instruction formats, sample assembly language programs, and the processing an assembler performs to generate machine code from assembly code.

PCI BUS

The PCI bus is a local computer bus standard used to connect hardware devices inside a computer. It was developed in the early 1990s to standardize how expansion cards connected to the motherboard. Key features of PCI include plug and play capability, configuration ROMs that store device information, and interrupt request lines. During initialization, the configuration software reads the ROM on each device to determine its type and assign resources like addresses and interrupts.

Micro program example

This document summarizes the key components of a microprogrammed computer system, including the control memory, registers, instruction format, microinstruction format, and microoperations. It provides details on how a microprogram is used to define the bit values for each of the 128 words in the control memory to implement routines for instructions like fetch, decode, and execution. The symbolic microprogram needs to be translated to binary for storage in the control memory.

Ram and-rom-chips

RAM is the main memory that allows bidirectional transfer of data via its data bus. It has a capacity of 128 bytes addressed by a 7-bit address. ROM can only read and can store more data than RAM in the same size chip. A memory address map assigns addresses to RAM and ROM chips. RAM uses address lines 1-7 and is selected by address lines 8-9 through a decoder. ROM uses address lines 1-9 and is selected by address line 10.

memory and storage devices

1. The document discusses different types of computer memory and storage devices. It describes RAM, ROM, SRAM, and DRAM memory types and how RAM is used for temporary data storage.

2. Storage devices discussed include floppy disks, hard disks, magnetic tape, CDs, DVDs, and other optical discs. Floppy disks contain flexible plastic disks and were used to transfer small amounts of data between computers.

3. Hard disks differ in that they contain rigid metal platters that spin faster than floppy disks and are sealed inside the computer. Magnetic tape is cheaper for storing files and documents and transferring information between computers.

Components of ddbms

Components of DDBMS, Computer workstations or remote devices,Network hardware and software components,Communications media,transaction processor (TP), data processor (DP),

Types of Addressing modes- COA

Addressing mode is the way of addressing a memory location in instruction. Microcontroller needs data or operands on which the operation is to be performed. The method of specifying source of operand and output of result in an instruction is known as addressing mode.

There are various methods of giving source and destination address in instruction, thus there are various types of Addressing Modes. Here you will find the different types of Addressing Modes that are supported in Micro Controller 8051. Types of Addressing Modes are explained below:

1.Register Addressing Mode

2.Direct Addressing Mode

3.Register Indirect Addressing Mode

4.Immediate Addressing Mode

5.Index Addressing Mode

Explanation:

Register Addressing Mode: In this addressing mode, the source of data or destination of result is Register. In this type of addressing mode the name of the register is given in the instruction where the data to be read or result is to be stored.

Example: ADD A, R5 ( The instruction will do the addition of data in Accumulator with data in register R5)

Direct Addressing Mode: In this type of Addressing Mode, the address of data to be read is directly given in the instruction. In case, for storing result the address given in instruction is used to store the result.

Example: MOV A, 46H ( This instruction will move the contents of memory location 46H to Accumulator)

Register Indirect Addressing Mode: In Register Indirect Addressing Mode, as its name suggests the data is read or stored in register indirectly. That is, we provide the register in the instruction, in which the address of the other register is stored or which points to other register where data is stored or to be stored.

Example: MOV A, @R0 ( This instruction will move the data to accumulator from the register whose address is stored in register R0 ).

Also Read: Architecture Of 8051

Immediate Addressing Mode : In Immediate Addressing Mode , the data immediately follows the instruction. This means that data to be used is already given in the instruction itself.

Example: MOV A, #25H ( This instruction will move the data 25H to Accumulator. The # sign shows that preceding term is data, not the address.)

Index Addressing Mode: Offset is added to the base index register to form the effective address if the memory location.This Addressing Mode is used for reading lookup tables in Program Memory. The Address of the exact location of the table is formed by adding the Accumulator Data to the base pointer.

Example: MOVC, @A+DPTR ( This instruction will move the data from the memory to Accumulator; the address is made by adding the contents of Accumulator and Data Pointer.

Input & Output

The document discusses input and output in computer systems. It describes three main techniques for transferring data between the CPU and I/O devices: programmed I/O, interrupt-driven I/O, and direct memory access (DMA). Programmed I/O involves the CPU continuously polling I/O devices, interrupt-driven I/O uses interrupts to signal the CPU when data is ready, and DMA allows high-speed transfer of data directly between memory and I/O devices without CPU involvement.

What's hot (20)

Computer Organization : CPU, Memory and I/O organization

Computer Organization : CPU, Memory and I/O organization

Viewers also liked

Internal memory

A computer uses a hierarchy of internal and external memory systems. Internal memory includes RAM, ROM, and cache, which provide fast access but are more expensive per byte. RAM allows independent access to each memory location and is used for main memory. ROM permanently stores data and is used for boot programs. Cached memory uses SRAM for faster access than RAM. External memory includes hard disks and USB drives, which provide large, inexpensive storage but are much slower to access.

05 internal memory

1. The document discusses different types of semiconductor memory including RAM, ROM, PROM, EPROM, EEPROM, and flash memory.

2. It describes the operation and structure of both dynamic RAM (DRAM) and static RAM (SRAM). DRAM uses capacitors to store bits and requires refreshing, while SRAM uses flip-flops and does not require refreshing.

3. The document also covers various RAM technologies including synchronous DRAM (SDRAM), double data rate SDRAM (DDR SDRAM), Rambus DRAM (RDRAM), error correction codes, and cache DRAM.

Internal memory

Dokumen tersebut membahas tentang berbagai jenis memori komputer seperti RAM, ROM, dan cache memory beserta karakteristik dan cara kerjanya. RAM dapat diubah tetapi data akan hilang bila dimatikan, sedangkan ROM tidak dapat diubah tetapi data tetap tersimpan bahkan bila dimatikan. Cache memory berfungsi untuk mempercepat akses prosesor ke data dengan menyimpan data yang sering diakses dari RAM.

Csc1401 lecture06 - internal memory

This document discusses internal memory organization and technologies. It begins with an overview of memory cell operation for DRAM and SRAM. It then covers various memory types including DRAM, SRAM, ROM, PROM, EPROM, and EEPROM. Advanced DRAM technologies like synchronous DRAM, Rambus DRAM, and double data rate SDRAM are also summarized. The document concludes with sections on error correction techniques and cache DRAM.

Internal storage of a computer system

RAM (random access memory) is the primary storage area in a computer for programs and data that the processor can access. It is temporary memory that stores bytes of data and instructions until the computer is powered down. RAM needs to match the processor's abilities and most operating systems require at least 1GB of RAM to run smoothly. ROM (read only memory) provides permanent storage for instructions and firmware needed to boot the computer. It stores data using fixed circuits that don't erase when powered down, including the BIOS (basic input/output system) which contains hardware information and boot instructions.

05 Internal Memory

This document summarizes different types of semiconductor memory, including dynamic RAM (DRAM), static RAM (SRAM), read-only memory (ROM), synchronous DRAM (SDRAM), double data rate SDRAM (DDR SDRAM), RAMBUS RAM, cache DRAM, and error correction techniques. It describes the basic structure and operation of DRAM and SRAM memory cells, as well as advanced organizations like SDRAM that can improve memory performance.

Computer Networks - Error Detection & Error Correction

This document provides information about error detection and correction techniques used in computer networks. It discusses different types of errors that can occur like single-bit and burst errors. It explains that redundancy is needed to detect or correct errors by adding extra bits. Detection techniques discussed include parity checks, checksumming, and cyclic redundancy checks. Parity checks can only detect odd number of errors. Cyclic redundancy checks use polynomial arithmetic to generate a checksum. Forward error correction allows detection and correction of errors by adding redundant bits to distinguish different error possibilities. Hamming code is an example of an error correcting code that can detect and correct single bit errors.

Intel Chip , How do they do It

The document summarizes the process for manufacturing computer chips. It describes how silicon is purified from sand and formed into crystals. The crystals are sliced into wafers which are polished smooth. Multiple layers are then added through processes like applying photoresist, exposing it to UV light, etching away exposed areas, and bombarding it with ions to alter conductivity. Copper is electroplated to connect transistors. The wafers undergo testing before being cut into dies and packaged with a heatspreader.

Error Correction And Hamming Code Ibrar

Error correction techniques include retransmission of data when errors are detected and forward error correction where error correction codes are used to automatically correct errors. Hamming codes can detect and correct errors by using redundancy bits in the data and calculating parity checks to determine the position of errors. The document provides an example of how hamming codes work by adding redundancy bits to input data and using the parity checks to detect errors in the encoded data.

Error Correction Ppt

This document discusses issues around error correction when teaching English as a second language. It raises questions about what should be corrected (grammar, pronunciation, etc.), how corrections should be done (explicitly, implicitly, etc.), and when during a lesson corrections should occur. The document also notes a discrepancy between what teachers and students prefer - teachers generally favor selective corrections while students would like all mistakes addressed. It argues the goal should be effective communication and corrections should target errors that cause breakdowns in understanding.

Basic information about Computer memory

This document discusses the three main types of computer memory: cache memory, primary/main memory, and secondary memory. Cache memory acts as a buffer between the CPU and main memory, holding frequently used data and programs for fast access by the CPU. Primary memory is the working memory that holds active data and instructions, while secondary memory provides permanent storage of data on disks, CDs, DVDs, and is slower than primary memory.

Error detection and correction

This document discusses error detection and correction in digital communication. It describes how coding schemes add redundancy to messages through techniques like block coding and convolution coding to detect or correct errors. The encoder adds redundant bits to original messages to create relationships between bits that the decoder can use to check for errors. It also explains the use of modular arithmetic, specifically modulo-2 arithmetic which uses only 1s and 0s, for error detection and correction operations.

Error Detection And Correction

The document discusses error detection and correction techniques used in data communication. It describes different types of errors like single bit errors and burst errors. It then explains various error detection techniques like vertical redundancy check (VRC), longitudinal redundancy check (LRC), and cyclic redundancy check (CRC). VRC adds a parity bit, LRC calculates parity bits for each column, and CRC uses a generator polynomial to calculate redundant bits. The document also discusses Hamming code, an error correcting code that uses redundant bits to detect and correct single bit errors.

How to Make Awesome SlideShares: Tips & Tricks

Turbocharge your online presence with SlideShare. We provide the best tips and tricks for succeeding on SlideShare. Get ideas for what to upload, tips for designing your deck and more.

Getting Started With SlideShare

SlideShare is a global platform for sharing presentations, infographics, videos and documents. It has over 18 million pieces of professional content uploaded by experts like Eric Schmidt and Guy Kawasaki. The document provides tips for setting up an account on SlideShare, uploading content, optimizing it for searchability, and sharing it on social media to build an audience and reputation as a subject matter expert.

Viewers also liked (16)

Computer Networks - Error Detection & Error Correction

Computer Networks - Error Detection & Error Correction

Similar to Internal memory

Coa presentation3

This document provides information about computer organization and architecture. It discusses the motherboard as the central component that connects all other components like the CPU, RAM, expansion slots and ports. It describes how the chipset and its components like the northbridge and southbridge facilitate data exchange. It covers CPU components like the ALU and registers, and characteristics like clock speed and instruction sets. It also discusses the memory hierarchy including caches, RAM and disk storage. In summary, the document is an overview of key components and concepts in computer organization and architecture.

Imd 203 - Ch07

The document discusses upgrading and troubleshooting memory (RAM) on a personal computer. It covers different types of RAM technologies including SIMMs, DIMMs, and RIMMs. It provides instructions on how to upgrade RAM by adding compatible memory modules to empty slots on the motherboard. The document also discusses how to troubleshoot issues like memory errors by checking the memory type and size, reseating modules, and testing modules in different slots.

Chapter 7 Memory

The document discusses upgrading and troubleshooting memory (RAM) on a personal computer. It covers different types of RAM technologies like SIMMs, DIMMs, and RIMMs. It provides instructions on how to upgrade RAM by adding compatible memory modules to empty slots on the motherboard. Troubleshooting tips include checking that new memory is suitable for the motherboard, reseating modules if not detected properly, and testing modules individually to isolate issues.

Computer and its types

A computer is an electronic device that can accept data as input, manipulate the data according to programmed instructions, produce output, and store results for future use. Computers are used in nearly all aspects of modern life including business, education, healthcare, science, engineering, manufacturing, government, and more. A computer consists of an input unit, output unit, central processing unit, and memory. The central processing unit contains an arithmetic logic unit and control unit that work together to process instructions and manipulate data stored in memory.

Information processing cycle

The document summarizes the information processing cycle which includes 4 main steps: (1) input, (2) processing, (3) output, and (4) storage. It provides details about each step: input involves collecting data from various input devices, processing is performed by the CPU and involves calculations, output presents the results through output devices like monitors and printers, and storage saves data for future use through various storage devices like hard disks, solid state drives, tapes, and flash memory.

11 & 12

The document provides an overview of computer hardware and software components. It discusses how data is stored in binary form in computers and defines the primary functions of hardware as input, processing, output, and storage. The two main input devices are listed as the keyboard and mouse, while the two main output devices are the monitor and printer. Electronic hardware requires a method for the CPU to communicate, software to control it, and electricity to power it. The document also reviews operating system functions and common OS types, as well as components of the computer boot process.

Lecture 2 - Computer Hardware & Operating Systems

An educational hardware system consists of computer hardware components like the central processing unit (CPU), primary storage, secondary storage, and input/output devices. The CPU contains the processor, memory, and buses that connect all the parts. Primary storage like RAM is used for temporary data and instructions during processing while secondary storage such as hard disks store data long-term. Common computer components include the motherboard, video and sound cards, ports, and power supply inside the system unit.

COMPUTER COMPONENTS

A computer system consists of hardware and software. The hardware includes components like the motherboard, processor, memory, storage devices, and input/output components. Software includes operating systems, applications, and utilities. A computer's processor controls the execution of instructions from programs and can perform arithmetic, logical, and data movement operations. Memory in the form of RAM is used as the main working space for active programs and data. RAM is volatile and must be continually refreshed to prevent data corruption.

Computer hardware

The document discusses the components and functioning of a computer system. It describes how a computer accepts data as input, processes it using the central processing unit (CPU) and other components, and produces output. The CPU contains a control unit and arithmetic logic unit (ALU) that work together to control data flow and perform calculations. The computer also includes storage devices like RAM, ROM, hard disks, and optical drives to permanently save data and programs.

Introduction to Computer Hardware slides ppt

The document provides information about computer hardware components including the system unit, motherboard, processor, memory, and storage devices. It discusses the system unit as containing the main electronic components including the motherboard, processor, memory, and disk systems. The motherboard is described as the main circuit board where hardware components connect and contains the BIOS. Types of memory including RAM and ROM are outlined. Finally, magnetic and optical storage devices such as hard disks, CDs, and DVDs are introduced.

Computer organisation ppt

The document discusses computer organization and microprocessors. It begins by explaining that computer organization deals with the hardware components of a computer system, including input/output devices, the central processing unit, storage devices, and primary memory. It then discusses the basics of microprocessors, noting that the CPU performs tasks using a microprocessor integrated circuit. The microprocessor is made up of an arithmetic logic unit, control unit, and registers. The document then covers characteristics of microprocessors like clock speed, instruction set, and word size. It also discusses different types of memory devices, ports, and interfaces that are part of computer hardware.

Storage Devices

The document provides information about storage devices, including primary storage (RAM, ROM, cache) and secondary storage (hard disk drives). It discusses the components, technologies, and interfaces of hard disks. RAM can be static RAM, dynamic RAM (including FPM, EDO, SDRAM, DDR RAM), or cache memory. ROM includes masked ROM, programmable ROM, EPROM, and EEPROM. Errors in memory can be soft errors or hard errors. Secondary storage devices like hard disks use magnetic recording and have components like platters, read/write heads, and error correction codes to ensure data integrity.

Components of the System Unit.pdf

The system unit, or computer case, houses the main electronic components of a computer. It contains the motherboard, processor, memory, storage devices, ports, and power supply. The motherboard serves as the central circuit board to which these components connect. At the heart of the system unit are the processor and memory, which work together to process instructions and data and temporarily store active programs and information. Additional components like graphics cards, sound cards, and network adapters can be installed via expansion slots to add functionality to the system unit.

Electro -Mechanical components/devices

This document provides information on various electro-mechanical devices and components of a computer system. It describes electromechanical devices that have both electrical and mechanical processes, such as motors and switches. It then discusses the evolution of computer components, including the motherboard, expansion cards like video/graphics cards, RAM memory, and registers. It explains how these components work and interact together within a computer system.

11. Computer Systems Hardware 1

The document summarizes the five main units of a computer system: input, output, storage, arithmetic, and control units. It describes the functions of hardware components like integrated circuits, memory (RAM and ROM), and the processor. The processor has a control unit that retrieves and decodes instructions from memory and an arithmetic logic unit that performs calculations. Instructions are fetched, decoded, executed, and retired in sequence using the von Neumann architecture.

Computer Hardware Components

The document discusses various computer hardware components. It describes that a computer system consists of hardware like the case, storage drives, and peripherals. The hardware components include the computer case, power supply, motherboard, CPU, cooling systems, memory, and adapter cards. The case contains the internal components and comes in different form factors. The power supply provides power to the components.

IRJET- Design And VLSI Verification of DDR SDRAM Controller Using VHDL

The document describes the design and verification of a DDR SDRAM controller using VHDL. It discusses the architecture and functional blocks of the DDR SDRAM controller, which includes a SDRAM controller module, control interface module, command module, and data path module. The control interface module decodes commands from the host and tracks refresh requests. The command module generates the appropriate commands to the SDRAM based on the decoded commands and addresses. The data path module handles read and write data transfer operations at double data rate to achieve higher bandwidth compared to SDRAM. The DDR SDRAM controller was implemented in Verilog HDL and simulated and synthesized using appropriate tools.

Lesson three hardware basics

The document discusses the basic functions and components of a computer system. It explains how the bootstrap loader initializes the operating system during startup by testing hardware, loading the OS into memory, and passing control to the boot record. The major components of a computer include the motherboard, CPU, RAM, expansion slots, input/output ports, and monitors.

MICROPROCESSOR,BASICS AND MEMORY CONCEPT

YOU CAN STUDY WITH THIS ABOUT INPUT DEVICES, OUTPUT DIVICES ,BUS SYSTEM,RAM,ROM,CD,DVD,FLOPPY DISK ,ETC

Computer Memory Finder

The document is an A-Z glossary of computer memory terminology from the website MemoryFinder.org. It defines terms related to computer hardware components, memory technologies, and specifications. Some key terms defined include RAM, ROM, cache memory, buses, bytes, chips, latency, and memory modules. The glossary provides concise explanations of over 50 important concepts for understanding computer memory and components.

Similar to Internal memory (20)

IRJET- Design And VLSI Verification of DDR SDRAM Controller Using VHDL

IRJET- Design And VLSI Verification of DDR SDRAM Controller Using VHDL

Recently uploaded

The History of Stoke Newington Street Names

Presented at the Stoke Newington Literary Festival on 9th June 2024

www.StokeNewingtonHistory.com

How to Build a Module in Odoo 17 Using the Scaffold Method

Odoo provides an option for creating a module by using a single line command. By using this command the user can make a whole structure of a module. It is very easy for a beginner to make a module. There is no need to make each file manually. This slide will show how to create a module using the scaffold method.

CACJapan - GROUP Presentation 1- Wk 4.pdf

Macroeconomics- Movie Location

This will be used as part of your Personal Professional Portfolio once graded.

Objective:

Prepare a presentation or a paper using research, basic comparative analysis, data organization and application of economic information. You will make an informed assessment of an economic climate outside of the United States to accomplish an entertainment industry objective.

ANATOMY AND BIOMECHANICS OF HIP JOINT.pdf

it describes the bony anatomy including the femoral head , acetabulum, labrum . also discusses the capsule , ligaments . muscle that act on the hip joint and the range of motion are outlined. factors affecting hip joint stability and weight transmission through the joint are summarized.

Hindi varnamala | hindi alphabet PPT.pdf

हिंदी वर्णमाला पीपीटी, hindi alphabet PPT presentation, hindi varnamala PPT, Hindi Varnamala pdf, हिंदी स्वर, हिंदी व्यंजन, sikhiye hindi varnmala, dr. mulla adam ali, hindi language and literature, hindi alphabet with drawing, hindi alphabet pdf, hindi varnamala for childrens, hindi language, hindi varnamala practice for kids, https://www.drmullaadamali.com

The simplified electron and muon model, Oscillating Spacetime: The Foundation...

Discover the Simplified Electron and Muon Model: A New Wave-Based Approach to Understanding Particles delves into a groundbreaking theory that presents electrons and muons as rotating soliton waves within oscillating spacetime. Geared towards students, researchers, and science buffs, this book breaks down complex ideas into simple explanations. It covers topics such as electron waves, temporal dynamics, and the implications of this model on particle physics. With clear illustrations and easy-to-follow explanations, readers will gain a new outlook on the universe's fundamental nature.

Introduction to AI for Nonprofits with Tapp Network

Dive into the world of AI! Experts Jon Hill and Tareq Monaur will guide you through AI's role in enhancing nonprofit websites and basic marketing strategies, making it easy to understand and apply.

A Survey of Techniques for Maximizing LLM Performance.pptx

A Survey of Techniques for Maximizing LLM Performance

ISO/IEC 27001, ISO/IEC 42001, and GDPR: Best Practices for Implementation and...

Denis is a dynamic and results-driven Chief Information Officer (CIO) with a distinguished career spanning information systems analysis and technical project management. With a proven track record of spearheading the design and delivery of cutting-edge Information Management solutions, he has consistently elevated business operations, streamlined reporting functions, and maximized process efficiency.

Certified as an ISO/IEC 27001: Information Security Management Systems (ISMS) Lead Implementer, Data Protection Officer, and Cyber Risks Analyst, Denis brings a heightened focus on data security, privacy, and cyber resilience to every endeavor.

His expertise extends across a diverse spectrum of reporting, database, and web development applications, underpinned by an exceptional grasp of data storage and virtualization technologies. His proficiency in application testing, database administration, and data cleansing ensures seamless execution of complex projects.

What sets Denis apart is his comprehensive understanding of Business and Systems Analysis technologies, honed through involvement in all phases of the Software Development Lifecycle (SDLC). From meticulous requirements gathering to precise analysis, innovative design, rigorous development, thorough testing, and successful implementation, he has consistently delivered exceptional results.

Throughout his career, he has taken on multifaceted roles, from leading technical project management teams to owning solutions that drive operational excellence. His conscientious and proactive approach is unwavering, whether he is working independently or collaboratively within a team. His ability to connect with colleagues on a personal level underscores his commitment to fostering a harmonious and productive workplace environment.

Date: May 29, 2024

Tags: Information Security, ISO/IEC 27001, ISO/IEC 42001, Artificial Intelligence, GDPR

-------------------------------------------------------------------------------

Find out more about ISO training and certification services

Training: ISO/IEC 27001 Information Security Management System - EN | PECB

ISO/IEC 42001 Artificial Intelligence Management System - EN | PECB

General Data Protection Regulation (GDPR) - Training Courses - EN | PECB

Webinars: https://pecb.com/webinars

Article: https://pecb.com/article

-------------------------------------------------------------------------------

For more information about PECB:

Website: https://pecb.com/

LinkedIn: https://www.linkedin.com/company/pecb/

Facebook: https://www.facebook.com/PECBInternational/

Slideshare: http://www.slideshare.net/PECBCERTIFICATION

How to Fix the Import Error in the Odoo 17

An import error occurs when a program fails to import a module or library, disrupting its execution. In languages like Python, this issue arises when the specified module cannot be found or accessed, hindering the program's functionality. Resolving import errors is crucial for maintaining smooth software operation and uninterrupted development processes.

Executive Directors Chat Leveraging AI for Diversity, Equity, and Inclusion

Let’s explore the intersection of technology and equity in the final session of our DEI series. Discover how AI tools, like ChatGPT, can be used to support and enhance your nonprofit's DEI initiatives. Participants will gain insights into practical AI applications and get tips for leveraging technology to advance their DEI goals.

Advanced Java[Extra Concepts, Not Difficult].docx![Advanced Java[Extra Concepts, Not Difficult].docx](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

![Advanced Java[Extra Concepts, Not Difficult].docx](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

This is part 2 of my Java Learning Journey. This contains Hashing, ArrayList, LinkedList, Date and Time Classes, Calendar Class and more.

A Strategic Approach: GenAI in Education

Artificial Intelligence (AI) technologies such as Generative AI, Image Generators and Large Language Models have had a dramatic impact on teaching, learning and assessment over the past 18 months. The most immediate threat AI posed was to Academic Integrity with Higher Education Institutes (HEIs) focusing their efforts on combating the use of GenAI in assessment. Guidelines were developed for staff and students, policies put in place too. Innovative educators have forged paths in the use of Generative AI for teaching, learning and assessments leading to pockets of transformation springing up across HEIs, often with little or no top-down guidance, support or direction.

This Gasta posits a strategic approach to integrating AI into HEIs to prepare staff, students and the curriculum for an evolving world and workplace. We will highlight the advantages of working with these technologies beyond the realm of teaching, learning and assessment by considering prompt engineering skills, industry impact, curriculum changes, and the need for staff upskilling. In contrast, not engaging strategically with Generative AI poses risks, including falling behind peers, missed opportunities and failing to ensure our graduates remain employable. The rapid evolution of AI technologies necessitates a proactive and strategic approach if we are to remain relevant.

How to Manage Your Lost Opportunities in Odoo 17 CRM

Odoo 17 CRM allows us to track why we lose sales opportunities with "Lost Reasons." This helps analyze our sales process and identify areas for improvement. Here's how to configure lost reasons in Odoo 17 CRM

Azure Interview Questions and Answers PDF By ScholarHat

Azure Interview Questions and Answers PDF By ScholarHat

Recently uploaded (20)

How to Build a Module in Odoo 17 Using the Scaffold Method

How to Build a Module in Odoo 17 Using the Scaffold Method

The simplified electron and muon model, Oscillating Spacetime: The Foundation...

The simplified electron and muon model, Oscillating Spacetime: The Foundation...

Introduction to AI for Nonprofits with Tapp Network

Introduction to AI for Nonprofits with Tapp Network

Digital Artefact 1 - Tiny Home Environmental Design

Digital Artefact 1 - Tiny Home Environmental Design

A Survey of Techniques for Maximizing LLM Performance.pptx

A Survey of Techniques for Maximizing LLM Performance.pptx

ISO/IEC 27001, ISO/IEC 42001, and GDPR: Best Practices for Implementation and...

ISO/IEC 27001, ISO/IEC 42001, and GDPR: Best Practices for Implementation and...

Executive Directors Chat Leveraging AI for Diversity, Equity, and Inclusion

Executive Directors Chat Leveraging AI for Diversity, Equity, and Inclusion

Pride Month Slides 2024 David Douglas School District

Pride Month Slides 2024 David Douglas School District

How to Manage Your Lost Opportunities in Odoo 17 CRM

How to Manage Your Lost Opportunities in Odoo 17 CRM

Azure Interview Questions and Answers PDF By ScholarHat

Azure Interview Questions and Answers PDF By ScholarHat

Internal memory

- 1. ERROR CORRECTION A semiconductor memory system is subject to errors. These can be categorized as Hard Failures and Soft Errors. Hard Failure -permanent physical defect. Soft Error -Random, non destructive events that alters the contents of one or more memory cells. -No permanent damage to memory. -Can caused by power supply problem.

- 2. Error Correcting Code Function When data are to be read into memory, a calculation depicted as a function f is performed on the date to produce a code. Both the code and the data are stores, thus if an M-bit word of data is to be stored, and the code is of length K bits, then the actual size of the stored word in M+K bits. When the previously stored word is read out, the code is used to detect and possibly correct errors. A new set of K code bits is generated from The M data bits and compared with the fetched bits

- 3. Error Correcting Code Function The comparison yields one of the 3 results: -No errors are detected. The fetched data bits Are sent out. -An error is detected, and it is possible to correct the error. The data bits plus error correction bits are fed into a corrector, which produces a corrected set of M bits to be sent out. -An error is detected, but it is not possible To correct it. This condition is reported. A code is characterized by the number of bits errors in a word that it can correct and detect.

- 4. Hamming Error Correcting Code

- 5. ECC Memory Error-correcting code memory (ECC memory) is a type of computer data storage that can detect the most common kinds of internal data corruption. ECC memory used in most computers where data corruption cannot be tolerated under any circumstances, such as scientific or financial computing. *

- 6. What is Internal data corruption? Data corruption refers to errors in computer data that occur during writing reading, storage, transmission, or processing, which introduce unintended changes to the original data. Photo data corruption:

- 7. My Memory is ECC or Non-ECC? For Windows 7 you can run the following command in command prompt: wmic MEMORYCHIP get DataWidth,TotalWidth If the Total Width value is larger than the Data Width value you have ECC memory. Example output: //ECC Memory DataWidth TotalWidth 64 72 //Non-ECC Memory DataWidth TotalWidth 64 64

- 8. My Memory is ECC or Non-ECC? If you look at the physical memory module, ECC will usually have 9 (sometimes more) chips. Non-ECC will have only 8 (or rarely, 8x2=16).

- 9. Advantages and Disadvantages of using ECC Memory ADVANTAGES Data Integrity Easier Troubleshooting Advance Warning of Hardware Failure DISADVANTAGES Greater Expense Harder to Find Occasional False Positives Performance Penalty For ECC

- 10. ECC RAM vs. Non-ECC RAM

- 11. ECC Failure Rate Analysis ECC RAM is theoretically more stable and reliable than standard RAM, but many times theory does not match up with fact. To see if ECC RAM really is more reliable, we looked up our failure rates for ECC and non-ECC RAM over the past 3 years.

- 12. Advanced DRAM Organization One of the most critical system bottlenecks when using high performance processor is the interface to main internal memory The traditional DRAM chip is constrained both by its internal architecture and by interface to the processor’s memory bus A number of enhancements to the basic DRAM architecture have been explored:

- 13. Synchronous DRAM (SDRAM) One of the most widely used forms of DRAM Exchanges data with the processor synchronized to an external clock signal and running at the full speed of the processor/memory bus without imposing wait states With synchronous access the DRAM moves data in and out under control of the system clock The processor or other master issues the instruction and address information which is latched by the DRAM The DRAM then responds after a set number of clock cycles Meanwhile the master can safely do other task while the SDRAM is processing

- 18. Double Data Rate SDRAM (DDR SDRAM) SDRAM can only send data once per bus clock cycle Double-data rate SDRAM can send data twice per clock cycle, once on the rising of the clock pulse and once on the falling edge Developed by the JEDEC Solid State Technology Association ( Electronic Industries Alliance’s semiconductor engineering standardization body)

- 19. DDR SDRAM Road Timing RAS = row address select CAS = column address select DQ = data (in or out) DQS = DQ select Double data rate SDRAM can send data twice per clock cycle Rising edge Falling edge

- 20. DDR SDRAM for PCs

- 21. Cache DRAM (CDRAM) Developed by Mitsubishi Integrates a small SRAM cache onto a generic DRAM chip SRAM on the CDRAM can used in two ways: Cache mode of the CDRAM is effective for ordinary random access to memory Can also used as a buffer to support the serial access of a block of data

- 22. Types of DRAM SDRAM RDRAM DDR SDRAM CACHE DRAM