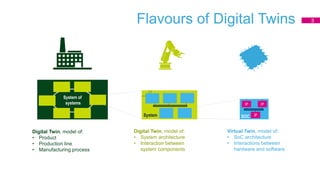

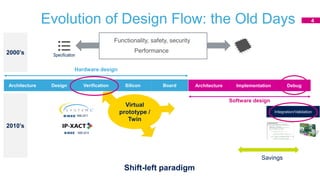

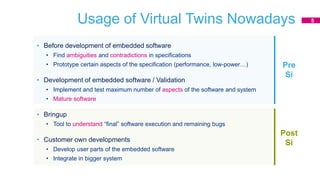

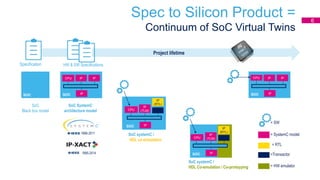

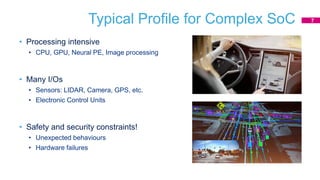

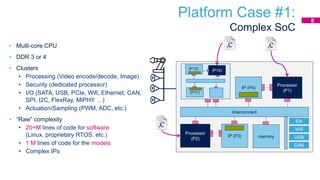

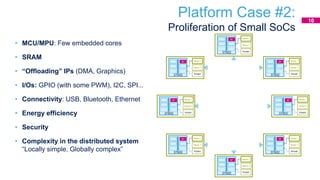

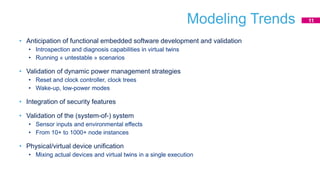

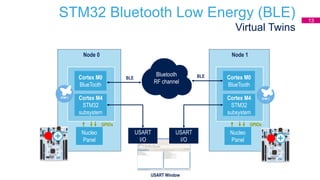

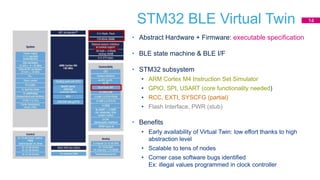

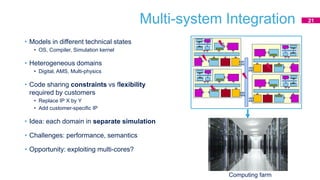

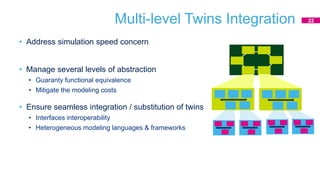

The document discusses the evolution and challenges of virtual twins in modeling, highlighting different types of digital twins, their applications in complex systems, and the advancements in design flow. It underlines the need for innovation in validation, security integration, and the handling of interconnected systems, particularly in automotive applications. Additionally, it emphasizes the importance of managing multiple levels of abstraction for effective integration and simulation in diverse technological domains.