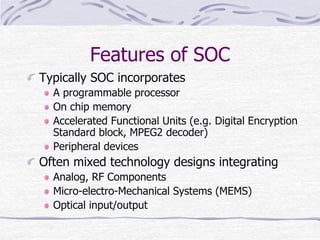

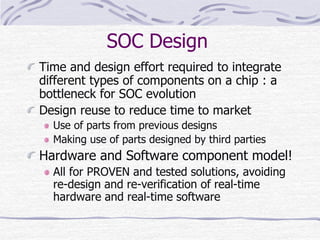

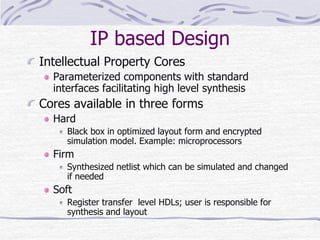

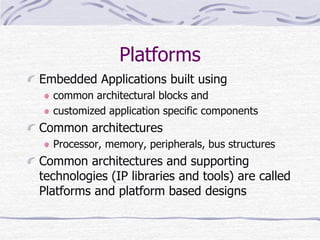

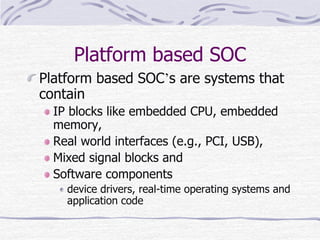

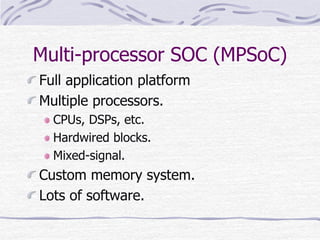

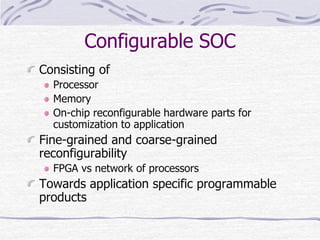

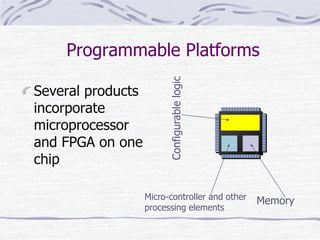

System on Chip (SOC) integrates multiple complex components previously designed as separate chips onto a single silicon chip. This provides benefits like reduced size, power consumption, and increased performance. An SOC typically includes a processor, memory, and peripheral interfaces integrated with analog and digital components. Platform-based SOC design uses pre-designed intellectual property blocks and software components to streamline development.

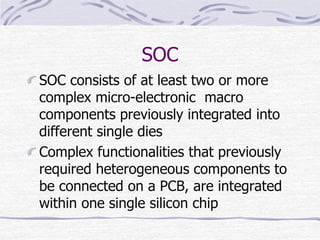

![Reconfigurable Computing

(RC)

What is it?

Compute by building a

circuit rather than

executing instructions.

Efficient for long

running computations

Video and image

processing

DSP

Network processing

Z[i] = a.X[i] + b.Y[i]

//program

Load rx, X

Mpy r1, rx, ra

Load ry, Y

Mpy r2, ry, rb

Add r3, r1, r2

Store r3, Z

+

X

* a

Y

* b

Z](https://image.slidesharecdn.com/systemonchipsoc-220823085423-23bd1a8e/85/System_on_Chip_SOC-ppt-34-320.jpg)

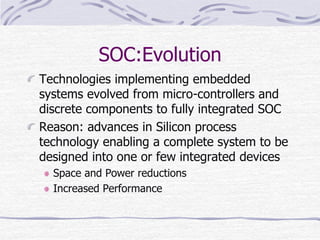

![Retargetable compilation

microarchitectural

model

for (i=0; i<N; i++)

c[i] = func1(a[i],b[i]);

application

code

front end

code

generation

object code

from ASIP core synthesis

instruction

set definition

Acknowledgement: Wayne Wolf](https://image.slidesharecdn.com/systemonchipsoc-220823085423-23bd1a8e/85/System_on_Chip_SOC-ppt-44-320.jpg)