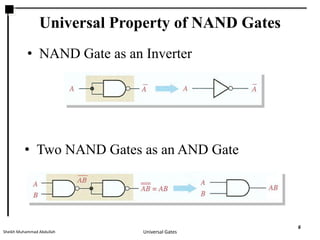

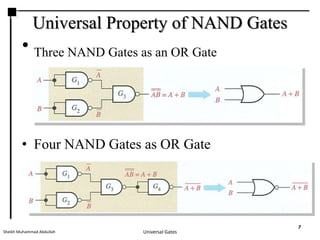

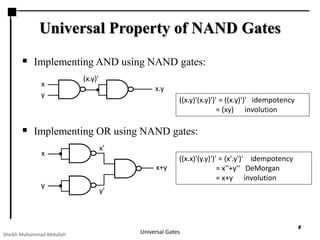

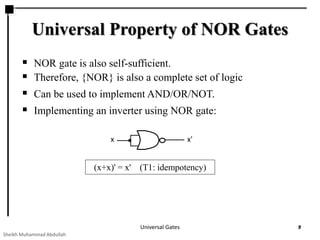

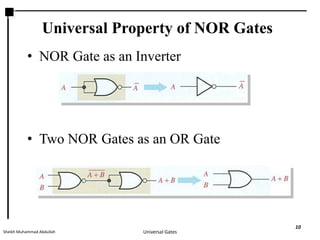

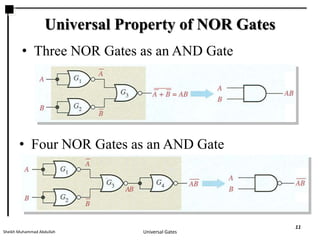

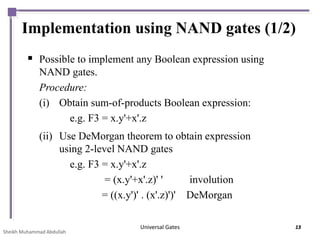

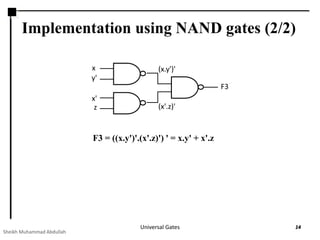

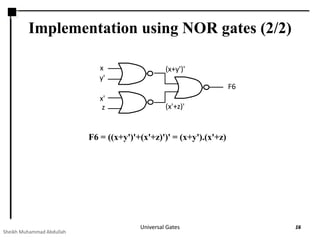

This presentation discusses NAND and NOR gates and their universal properties. It explains that NAND and NOR gates can be used to implement any other logic function, making them universal gates. The document provides examples of how to implement AND, OR, and INVERTER gates using only NAND gates or only NOR gates. It also gives procedures for implementing any Boolean logic expression using a network of only NAND gates or only NOR gates.