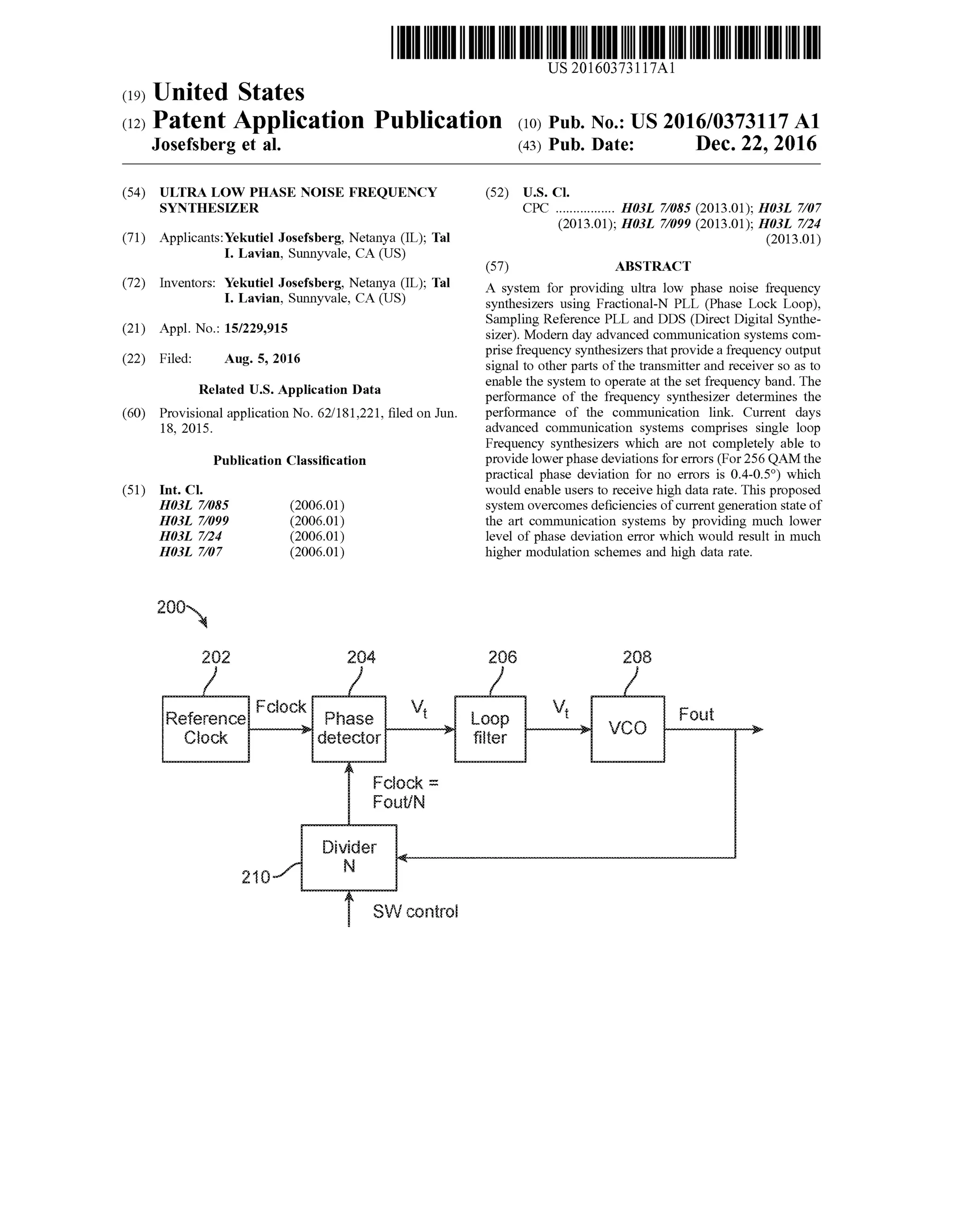

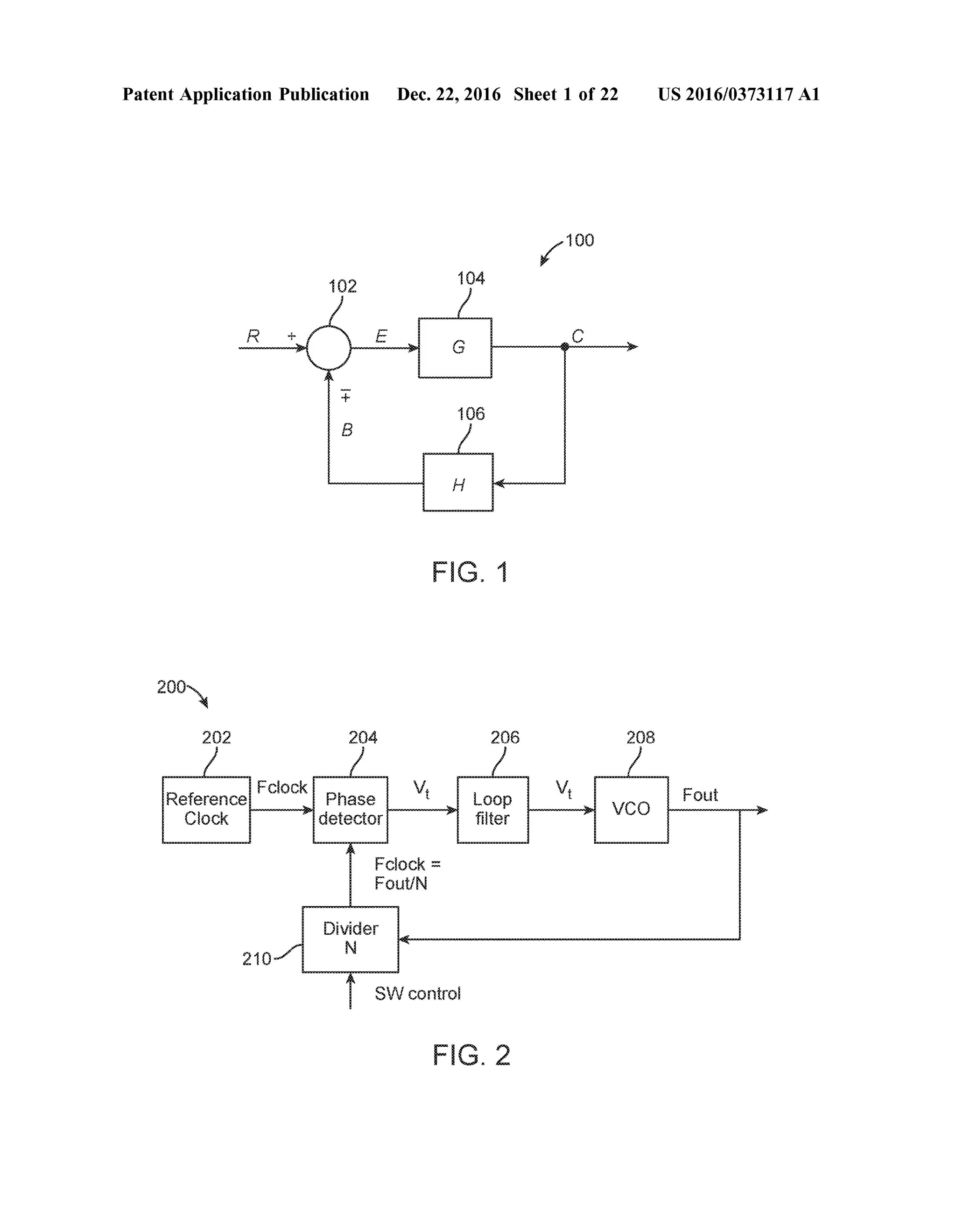

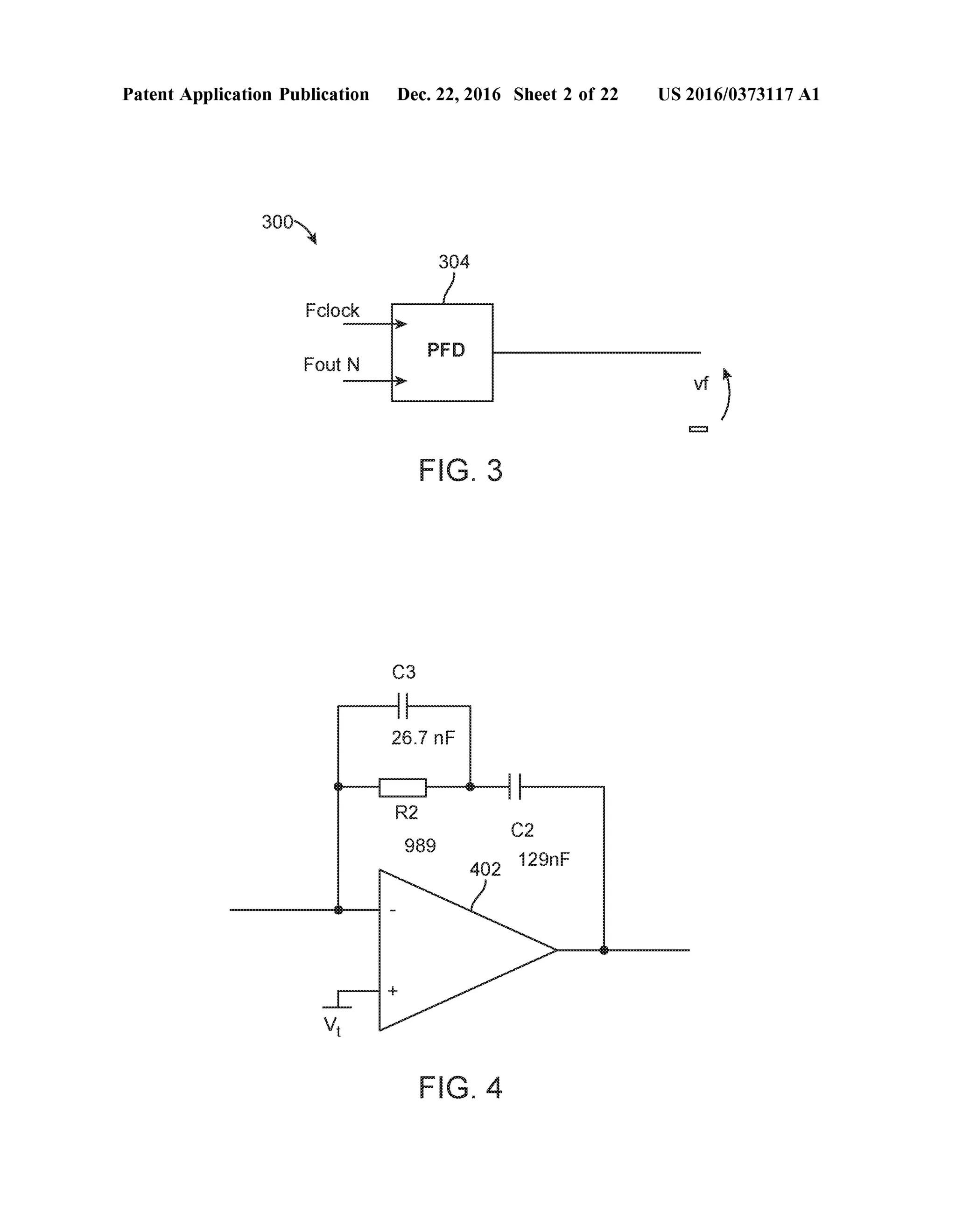

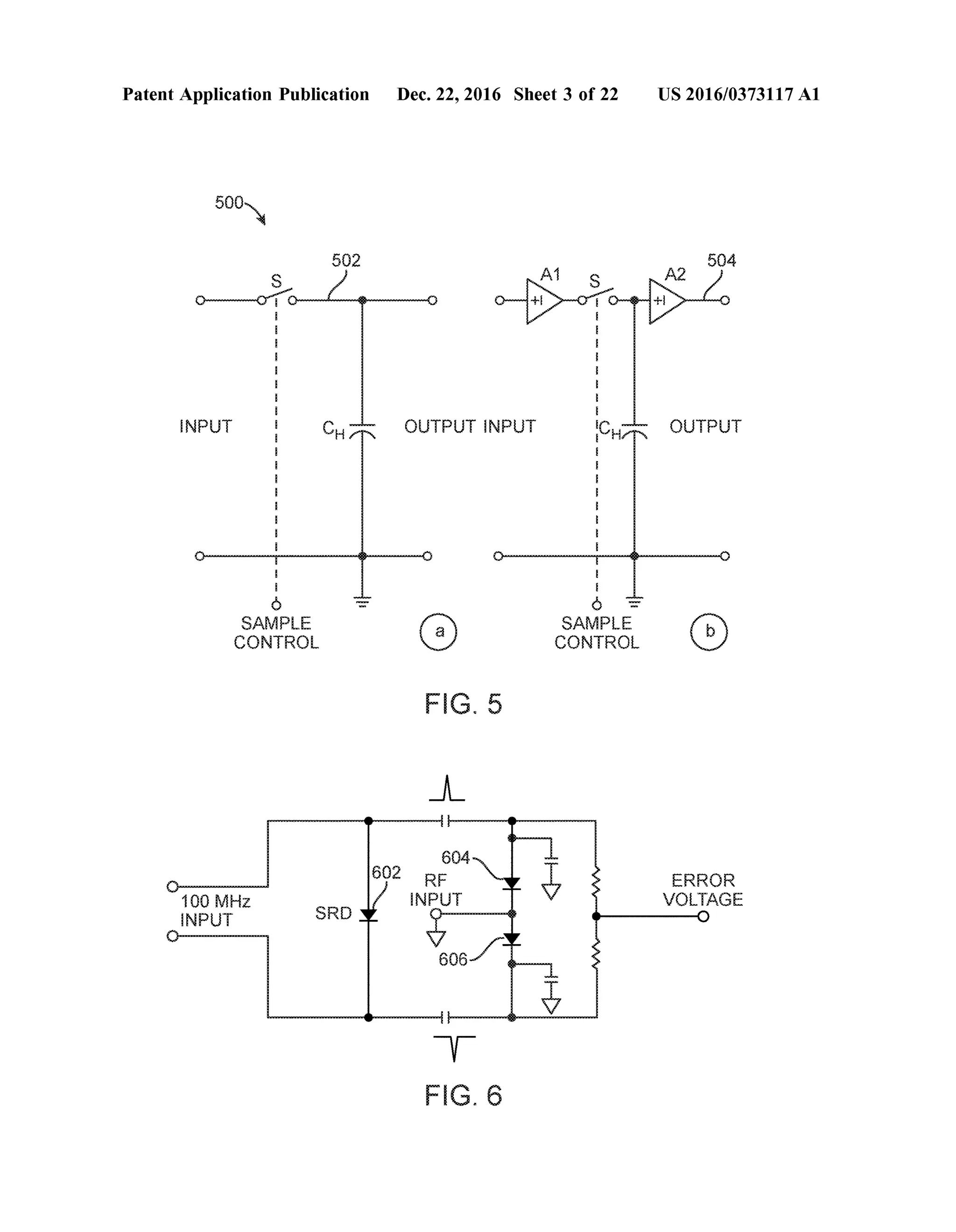

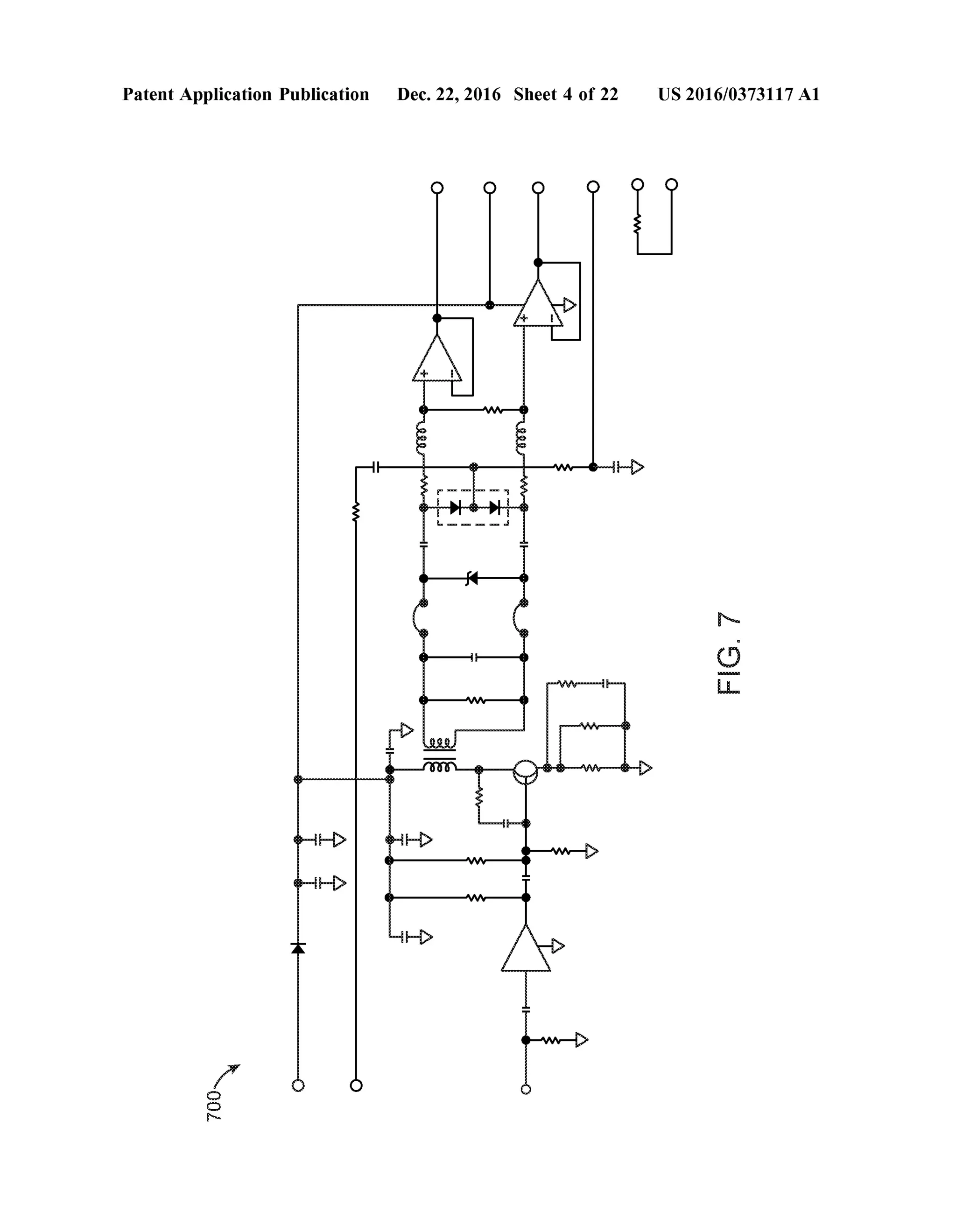

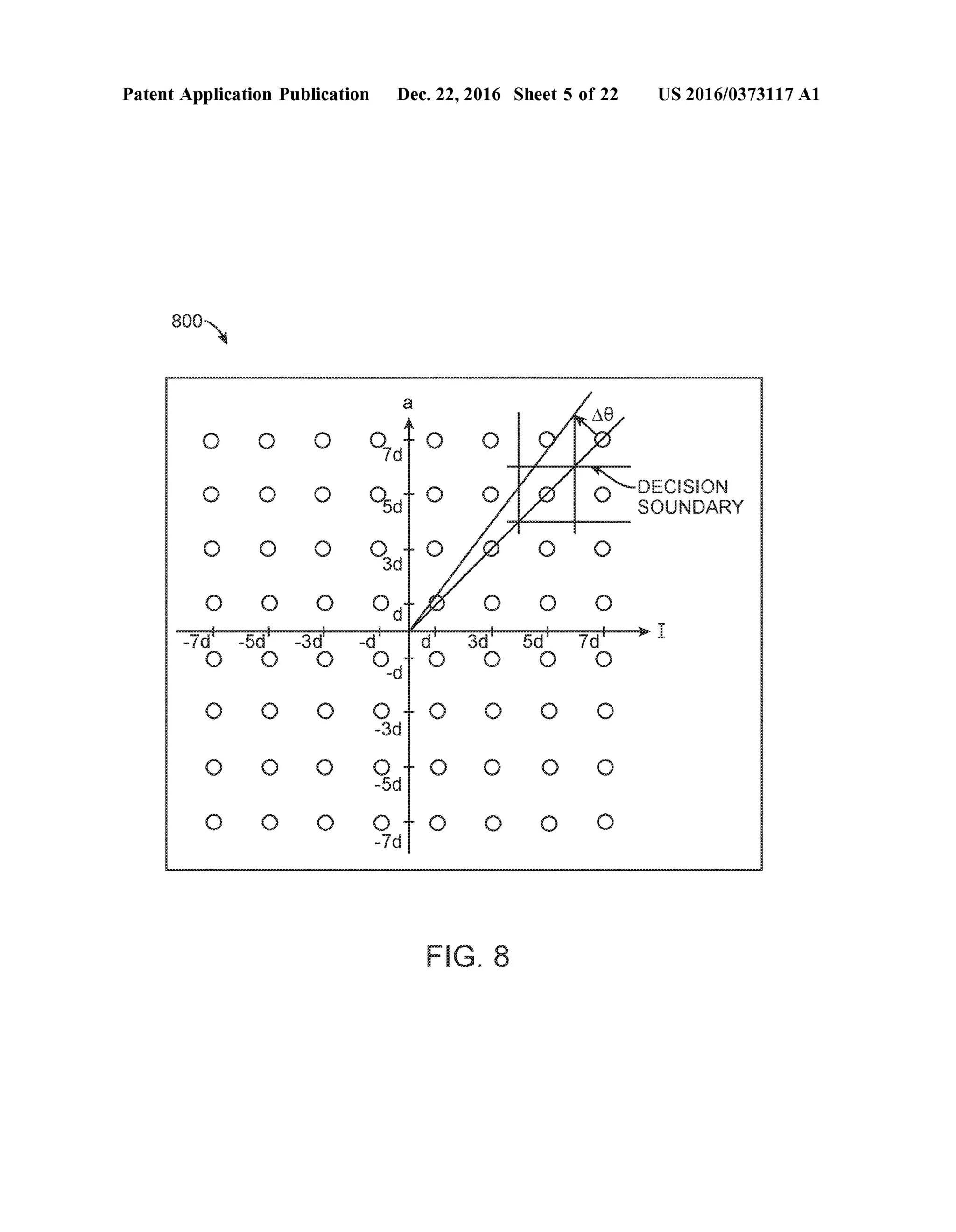

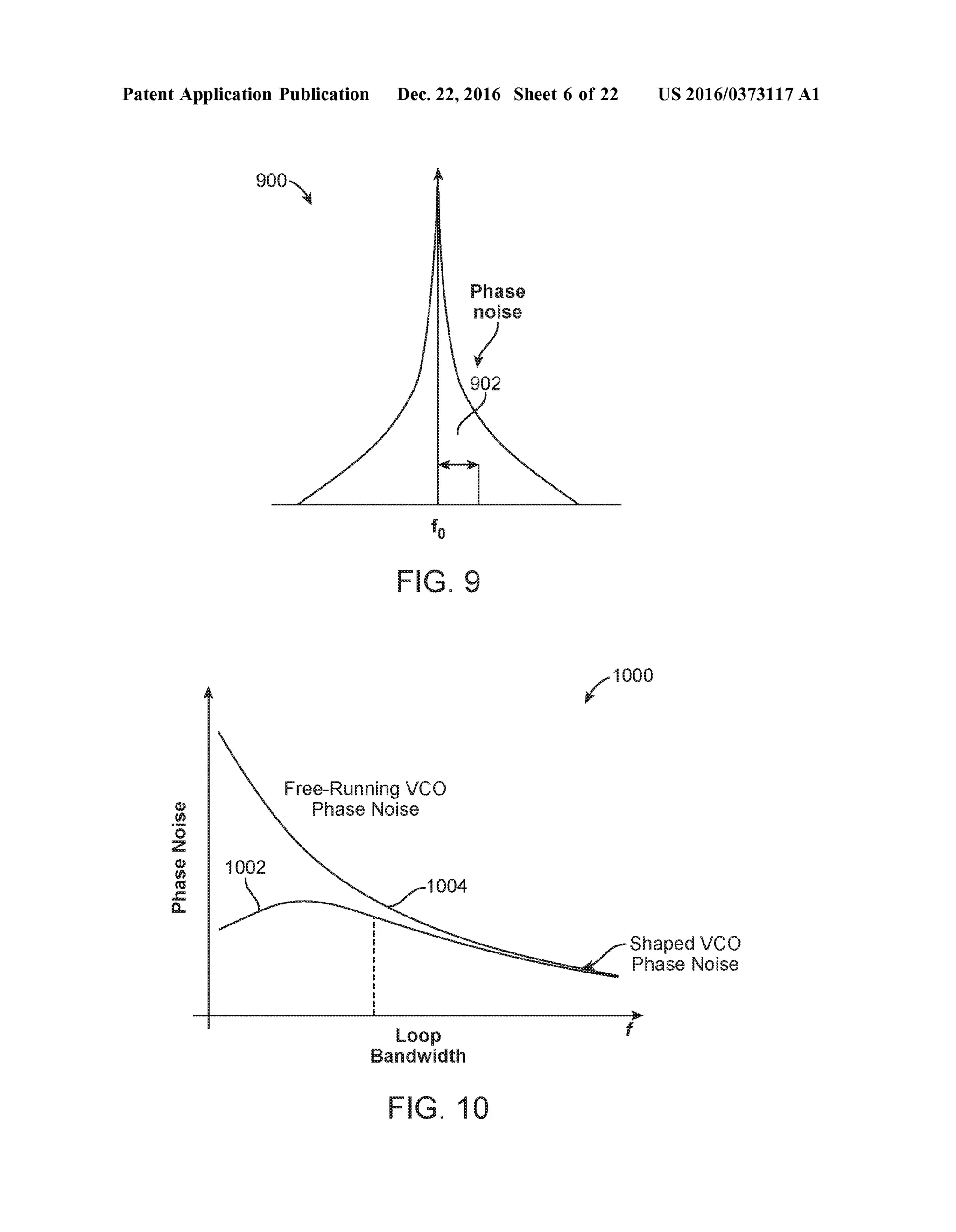

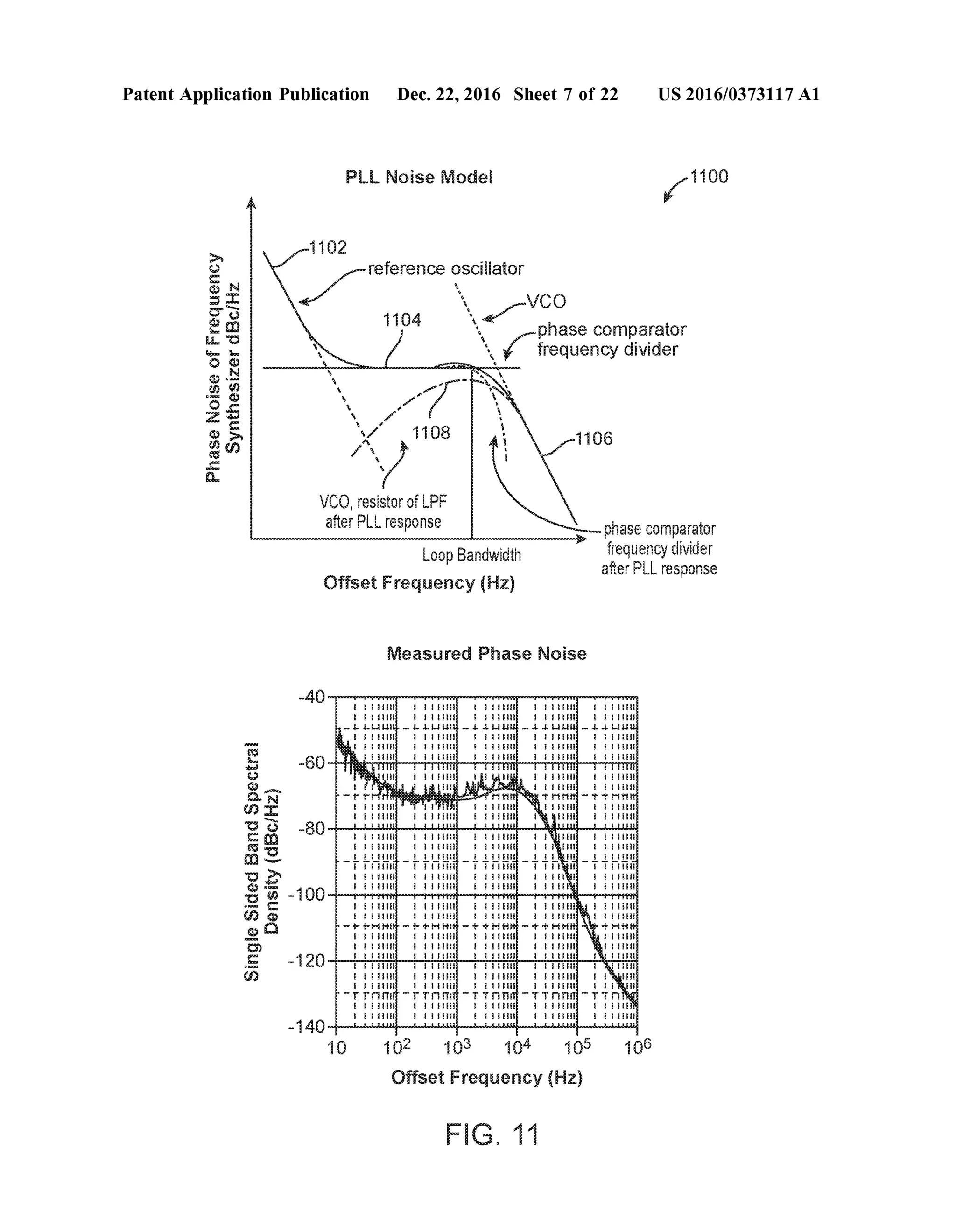

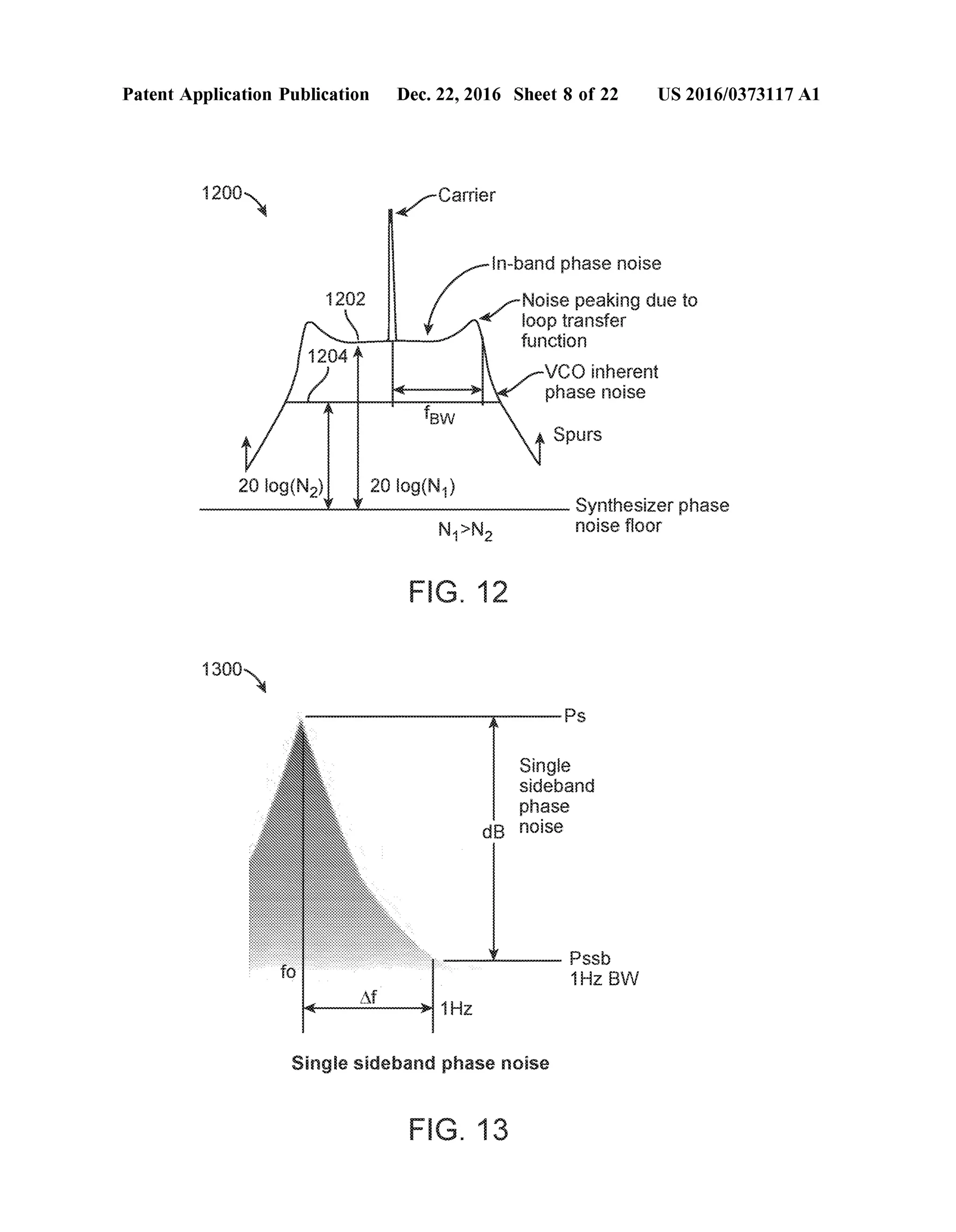

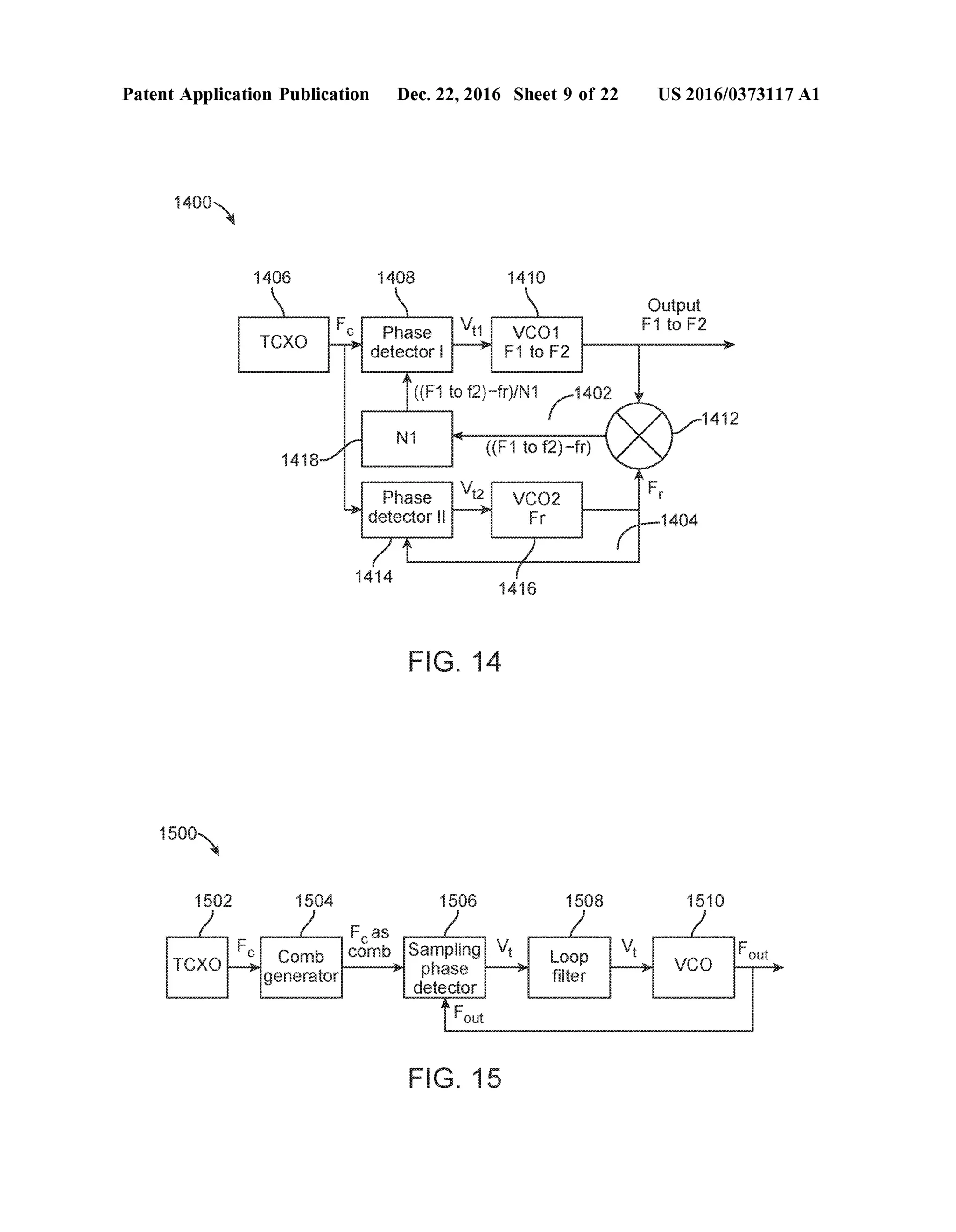

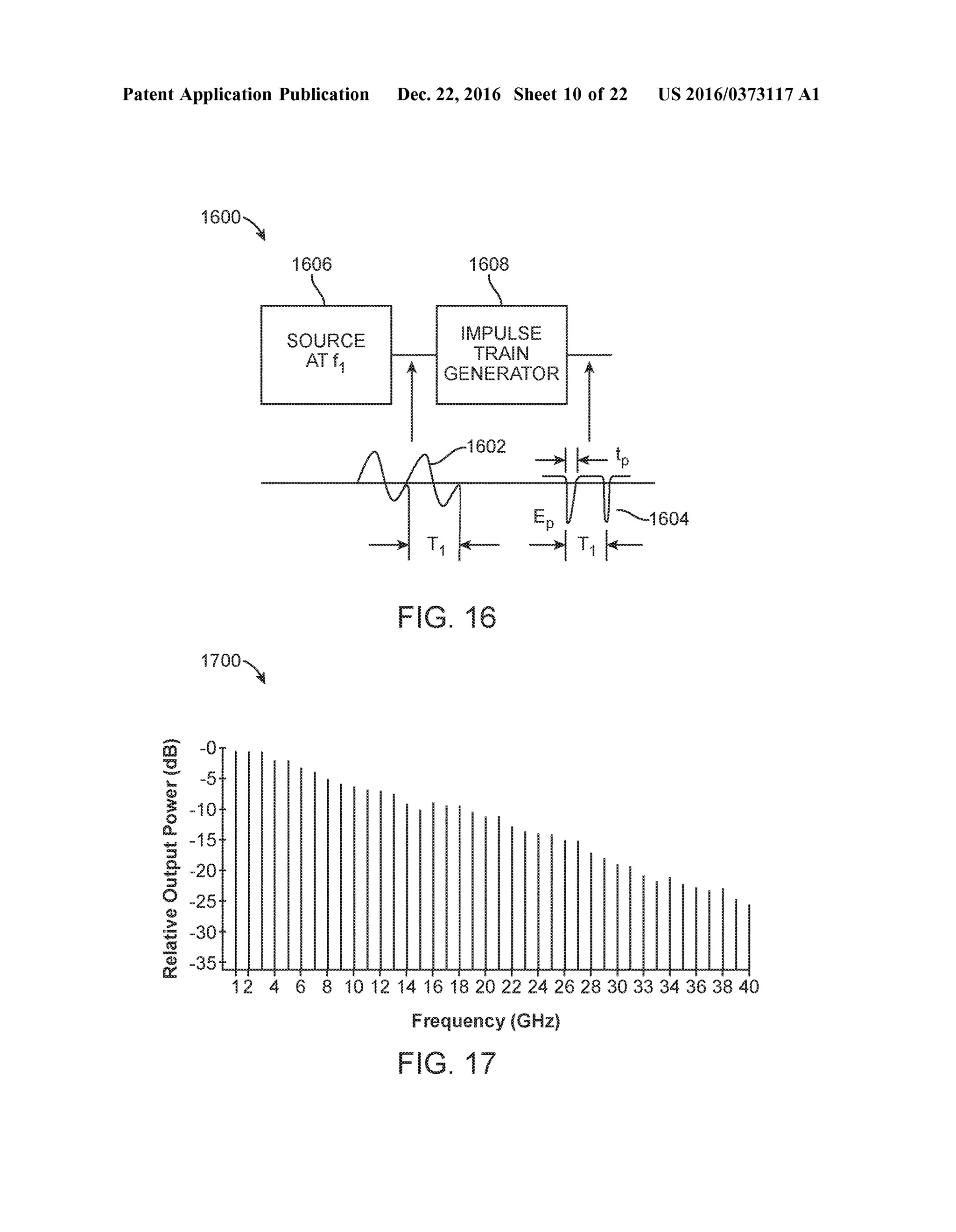

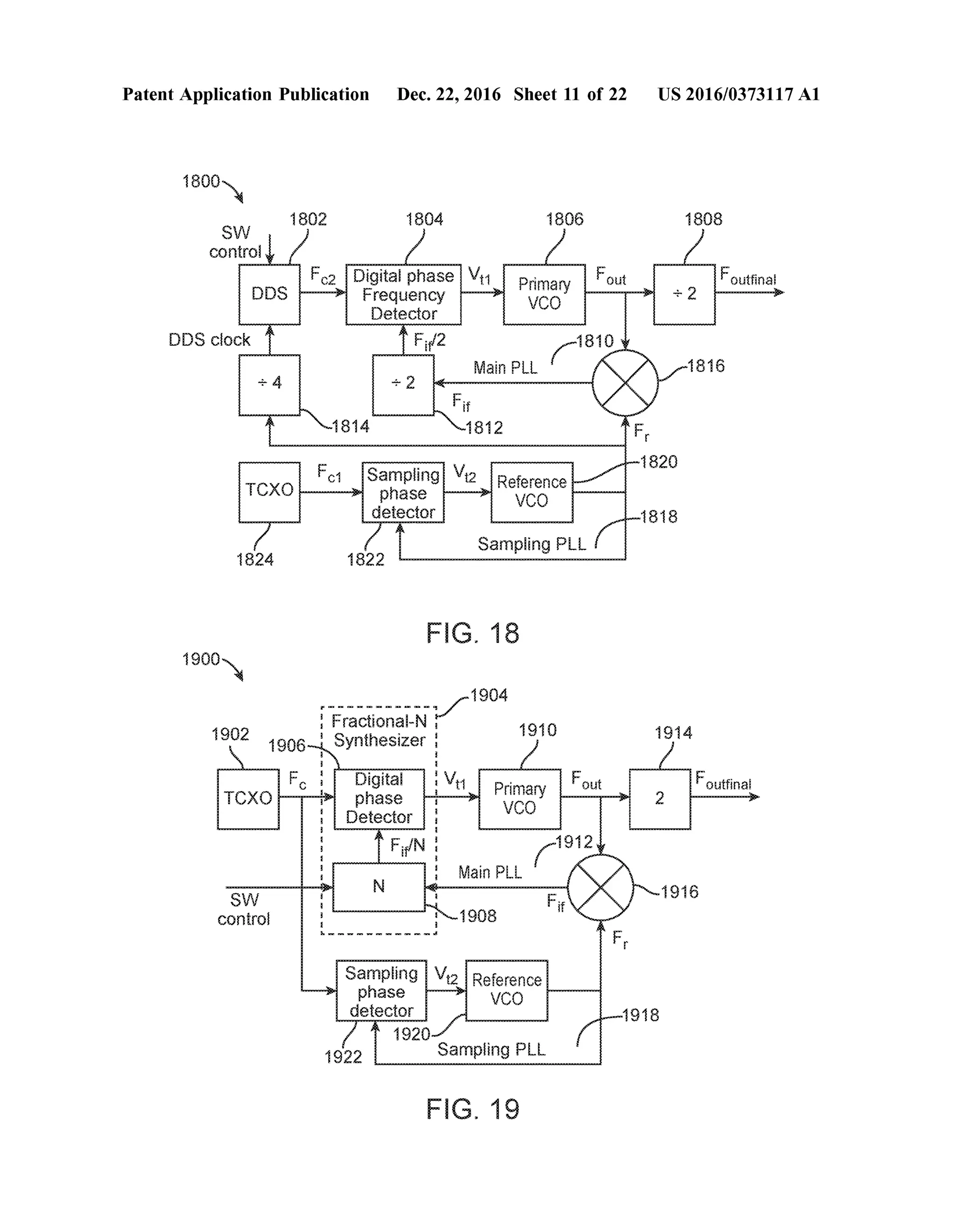

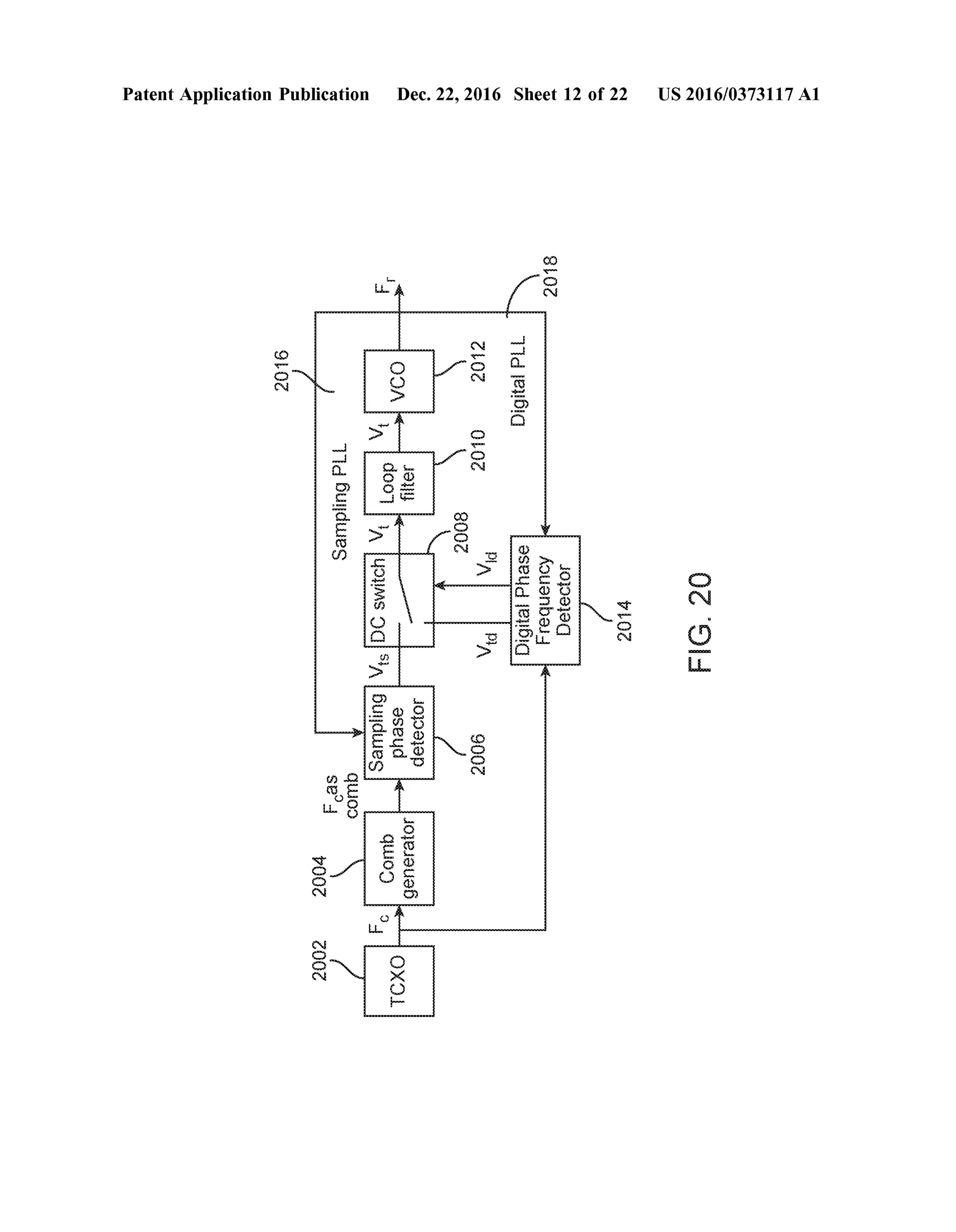

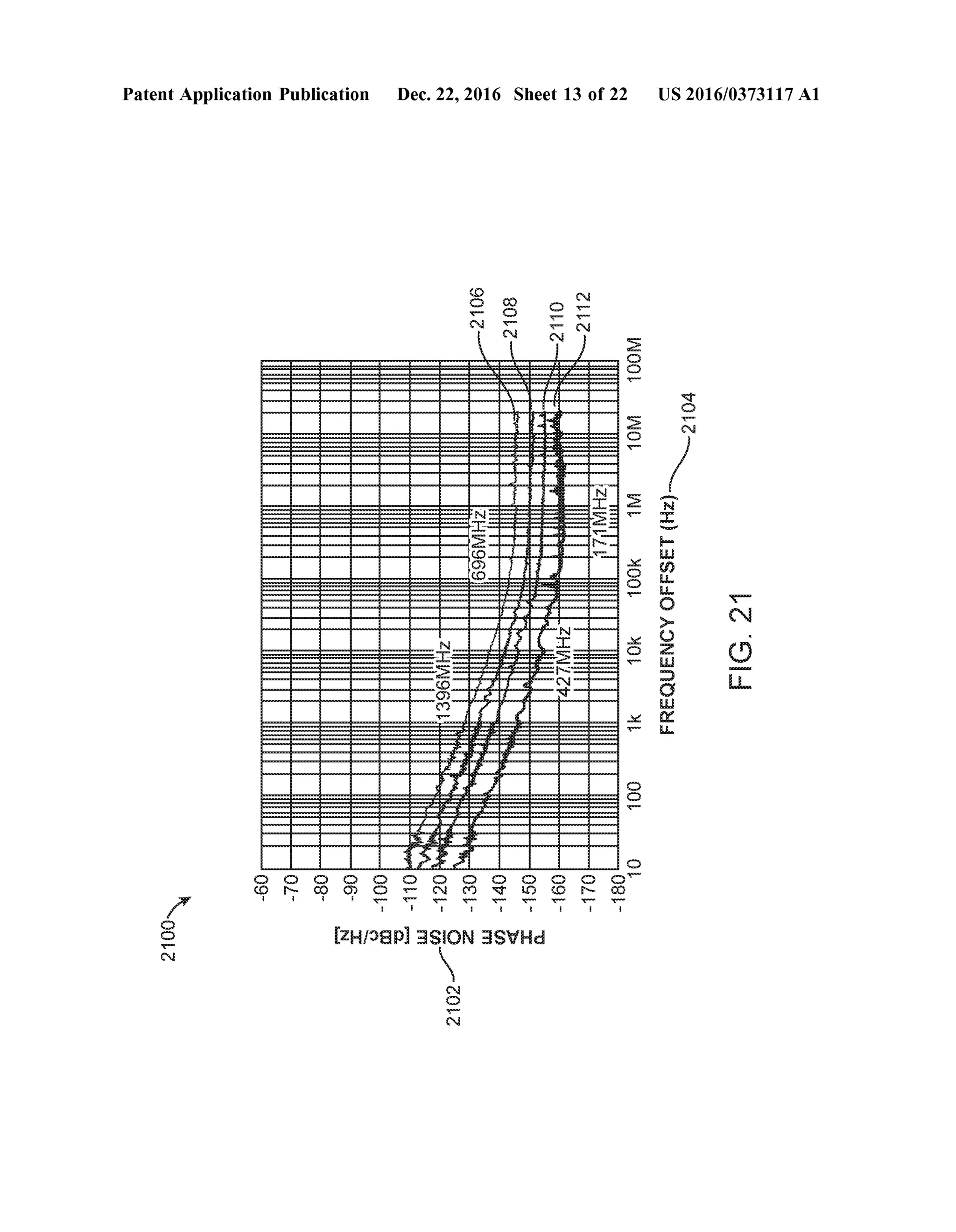

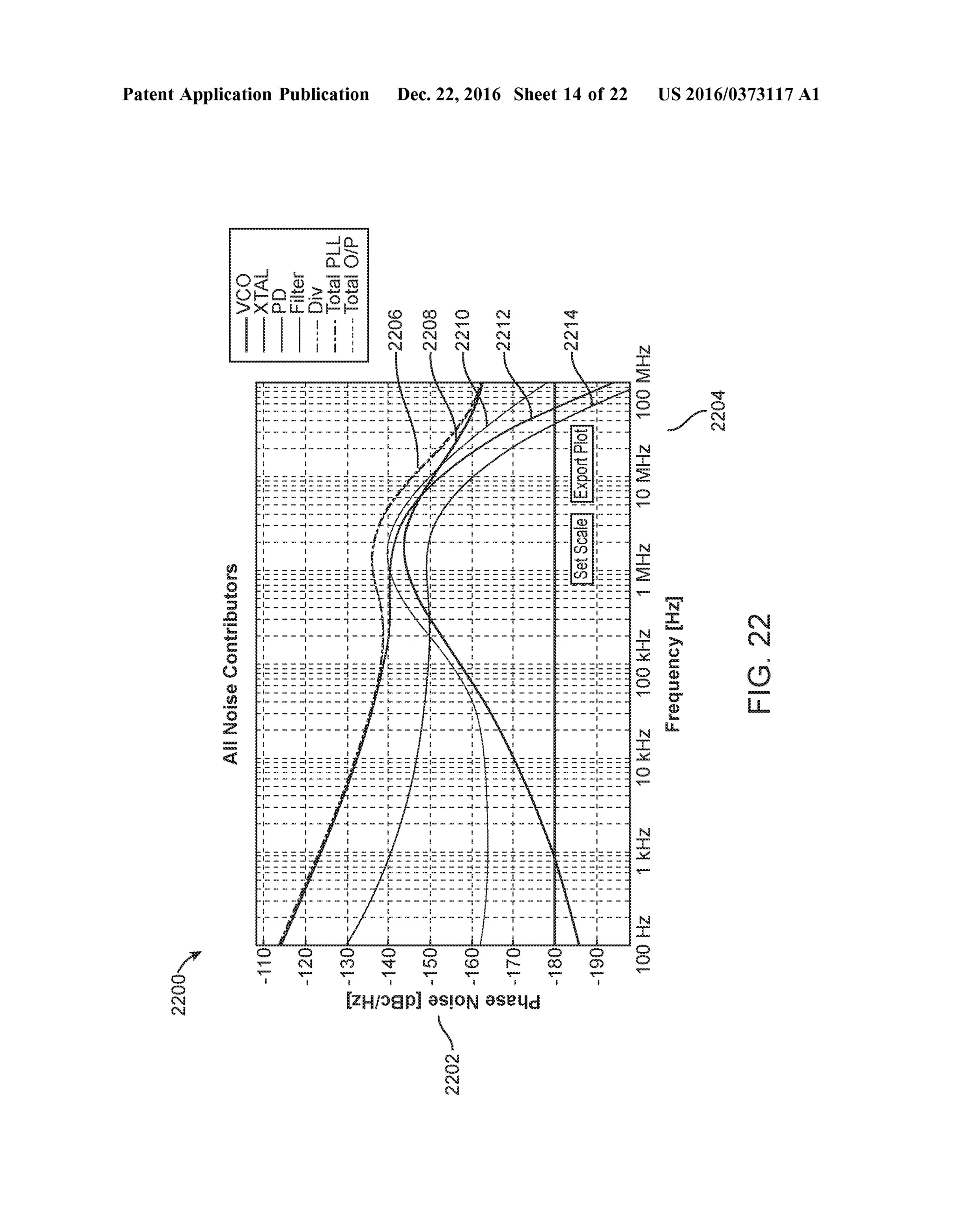

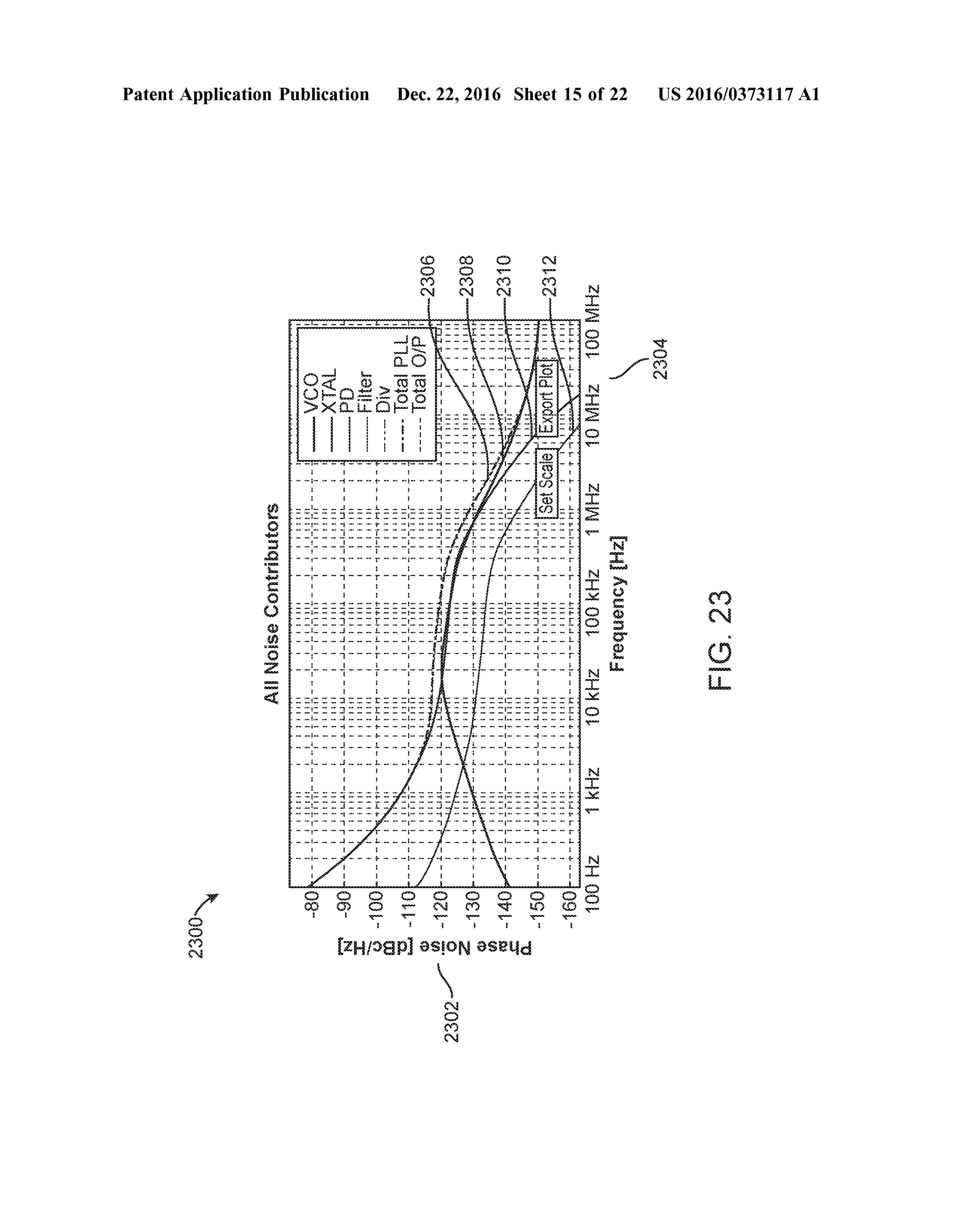

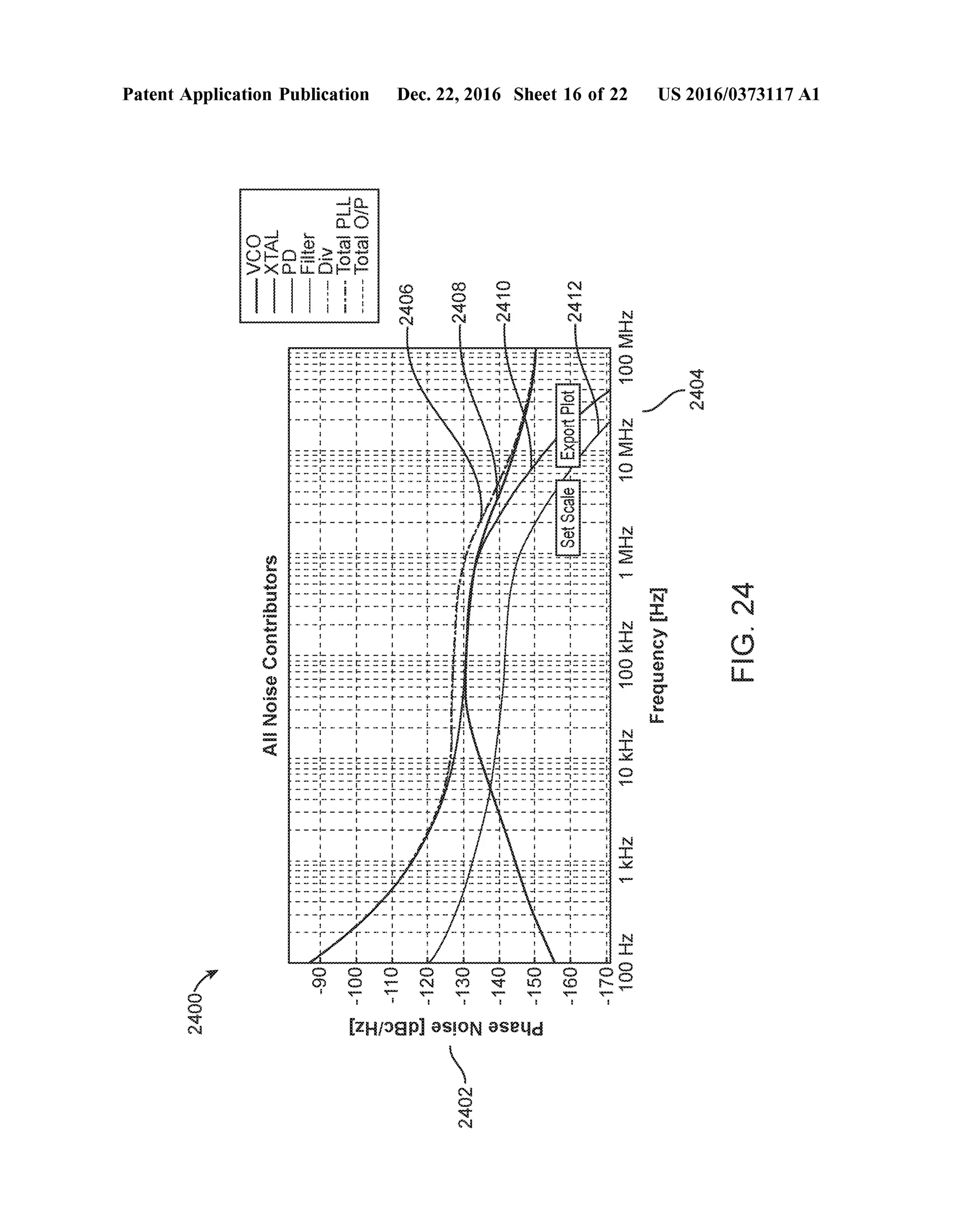

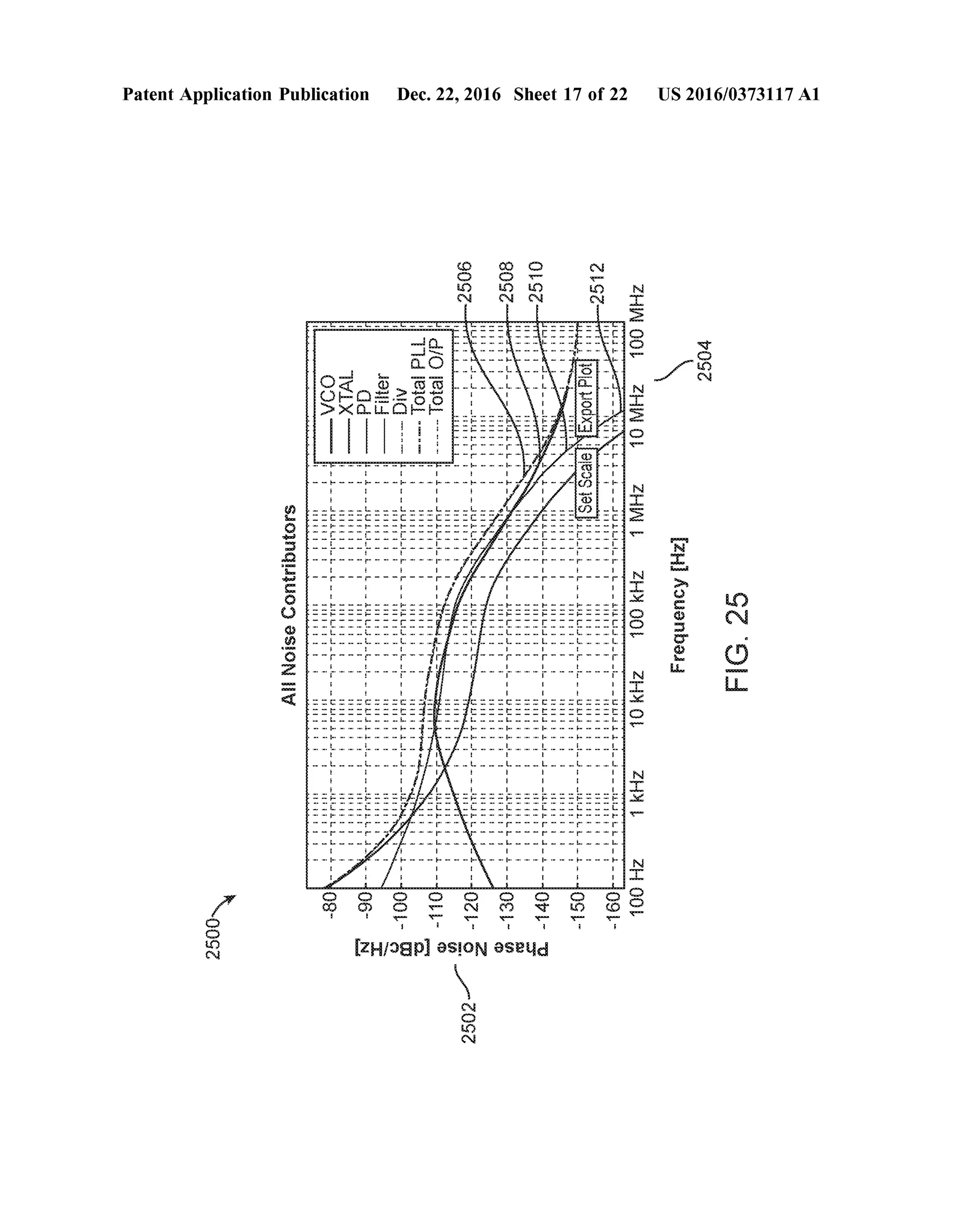

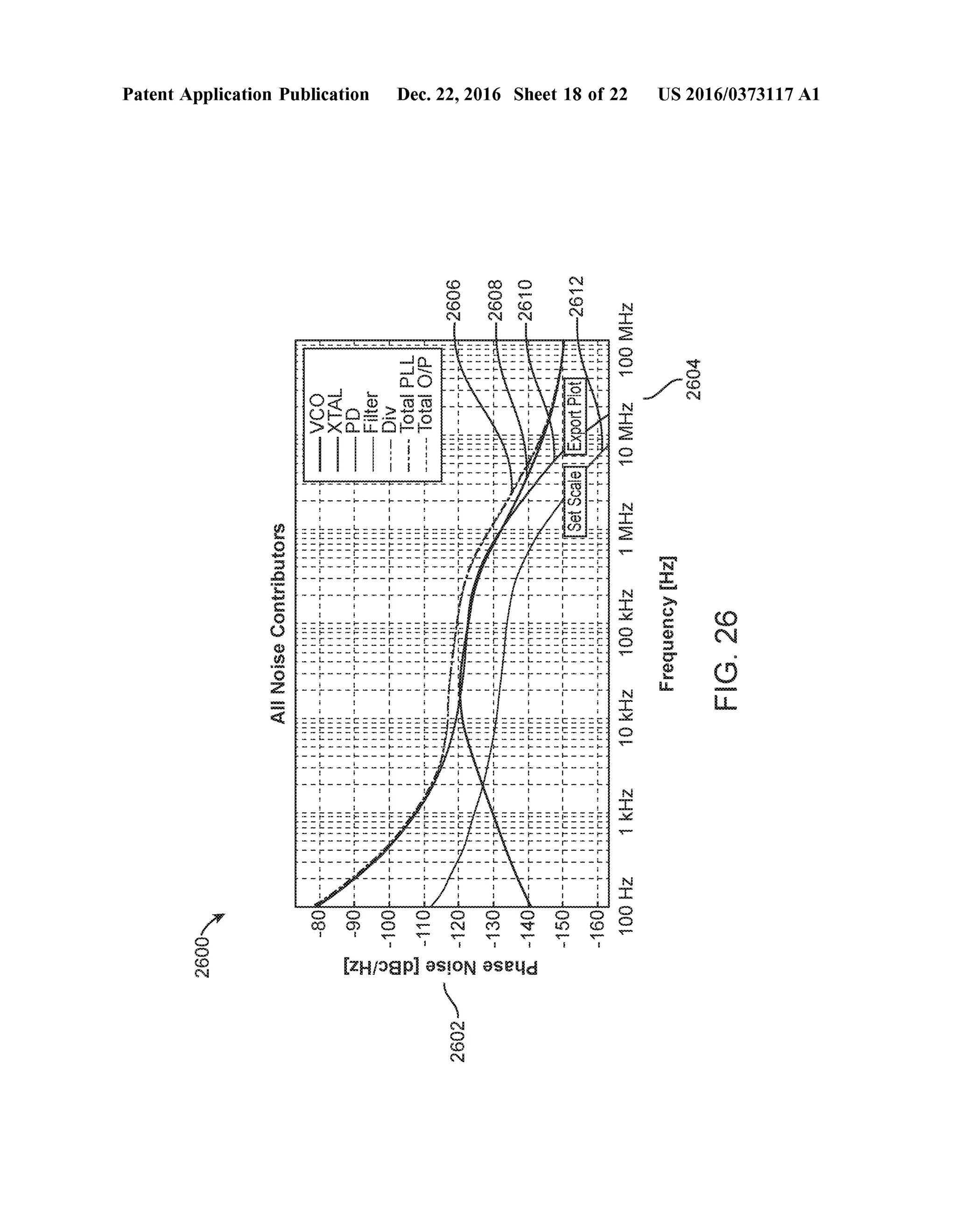

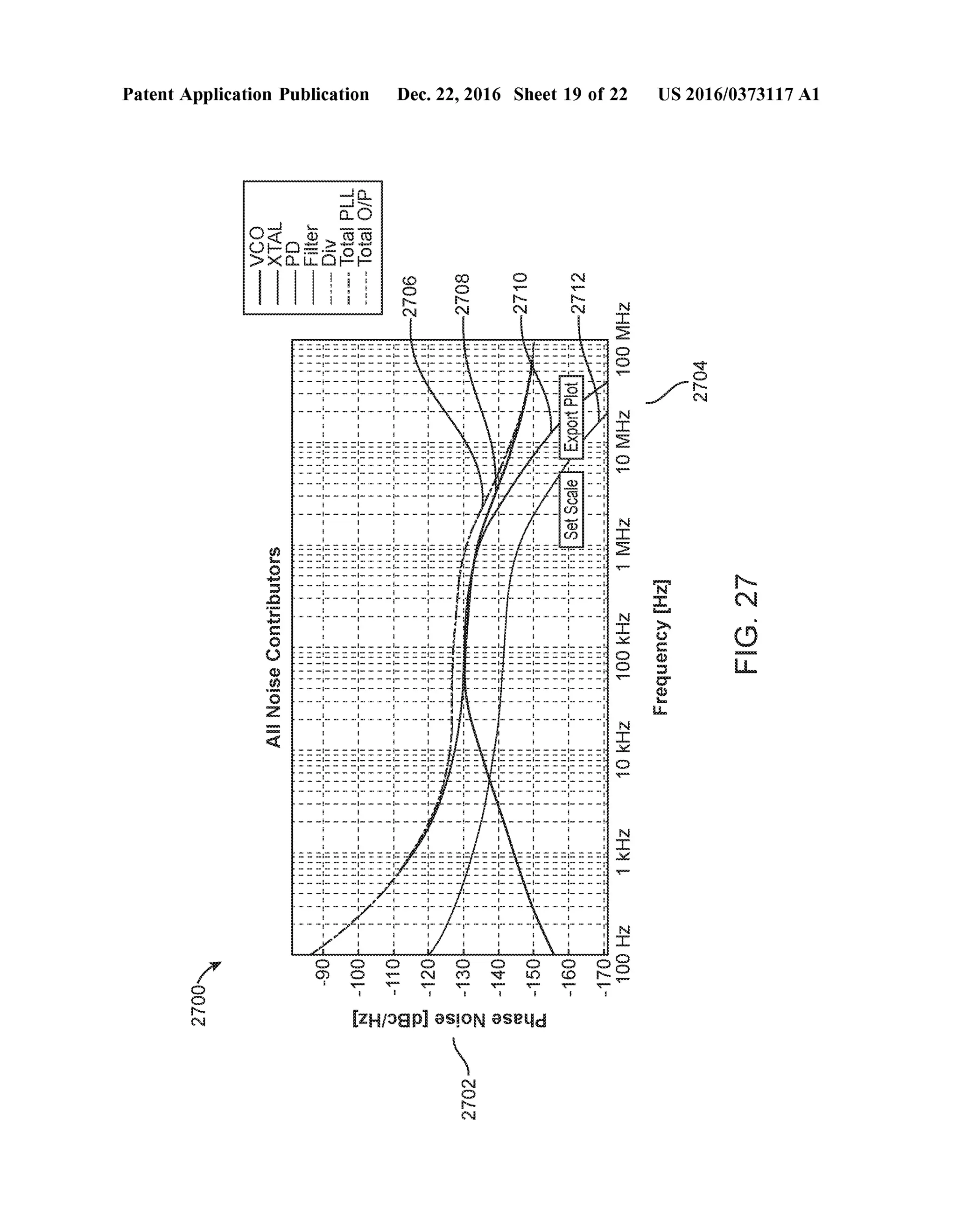

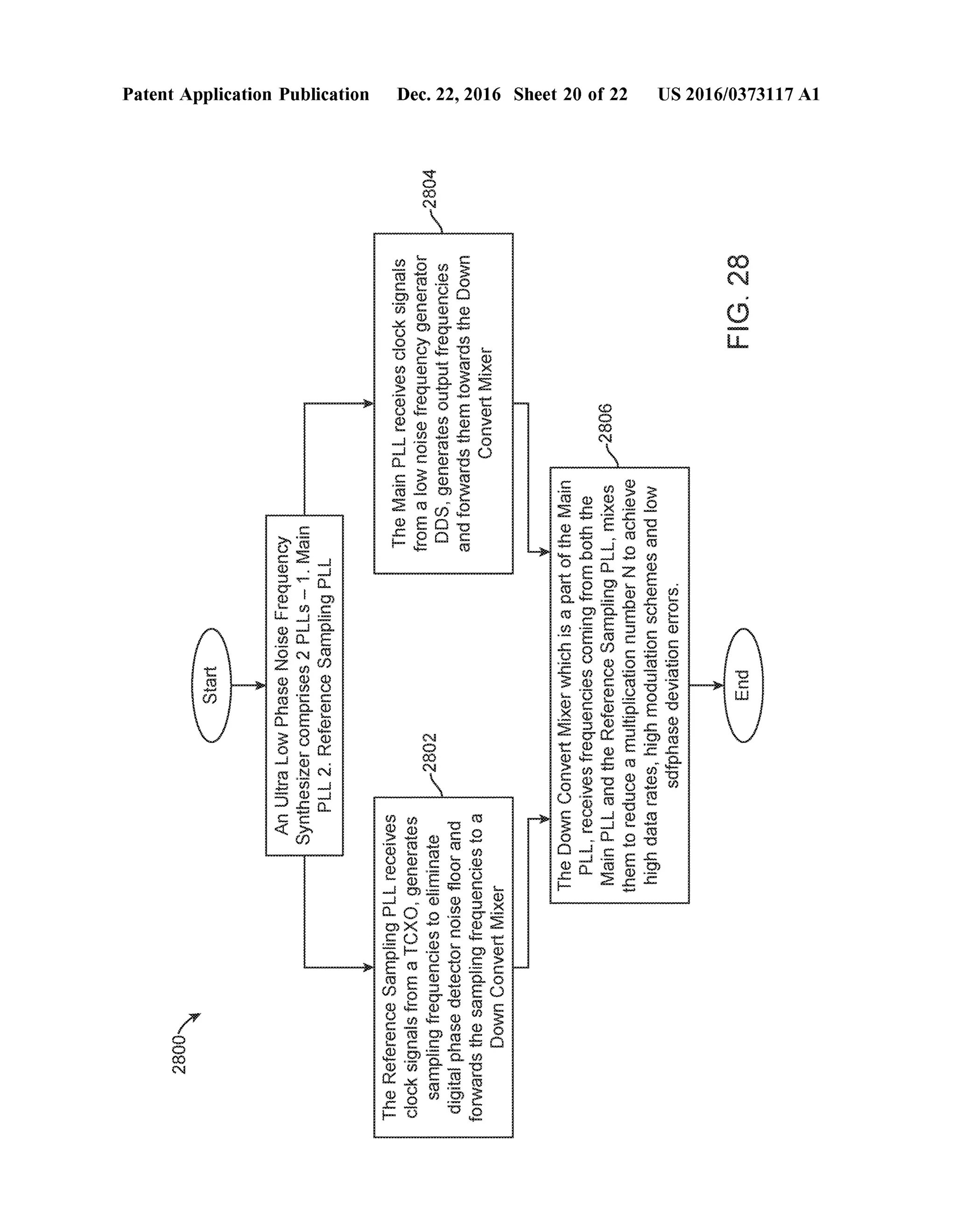

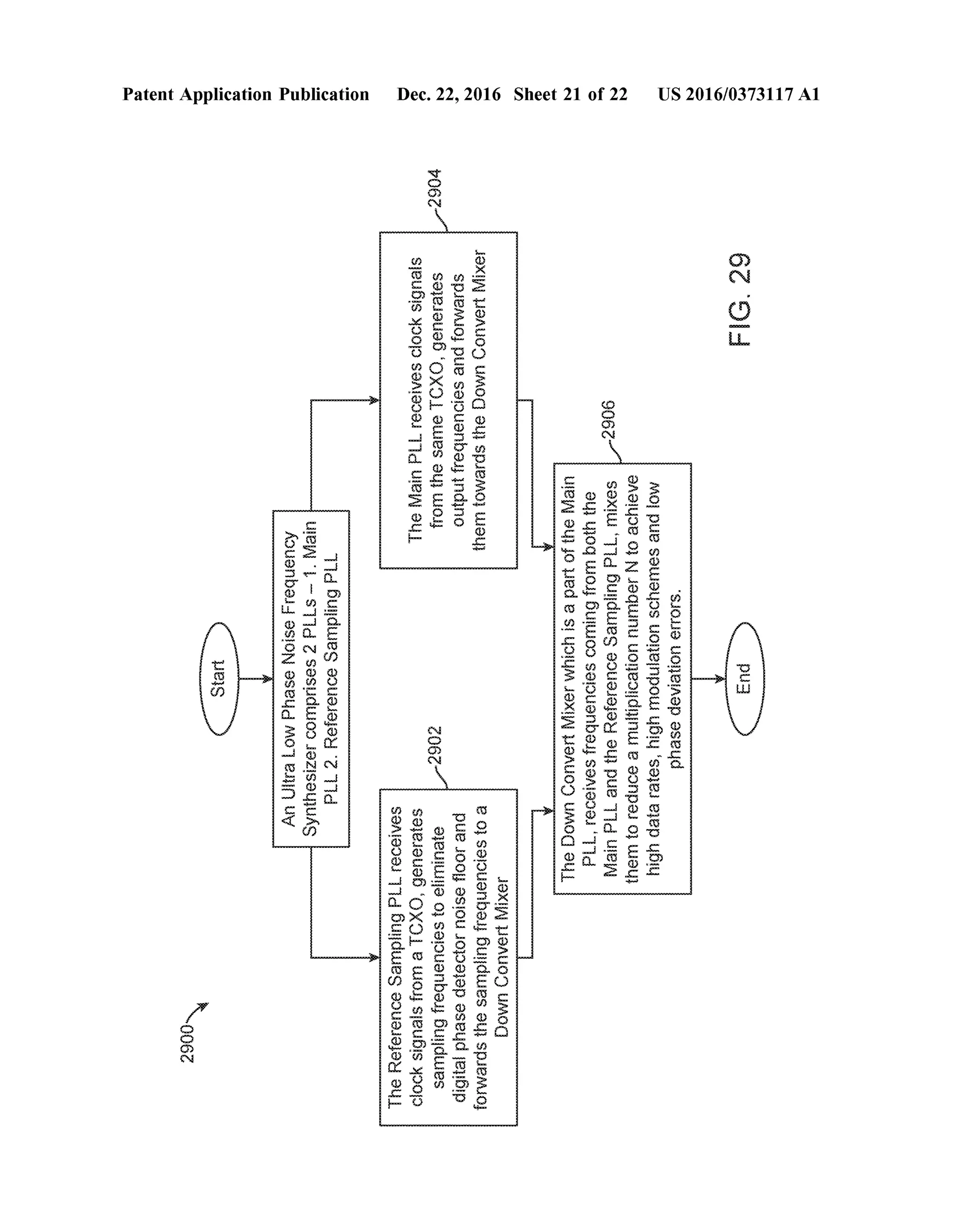

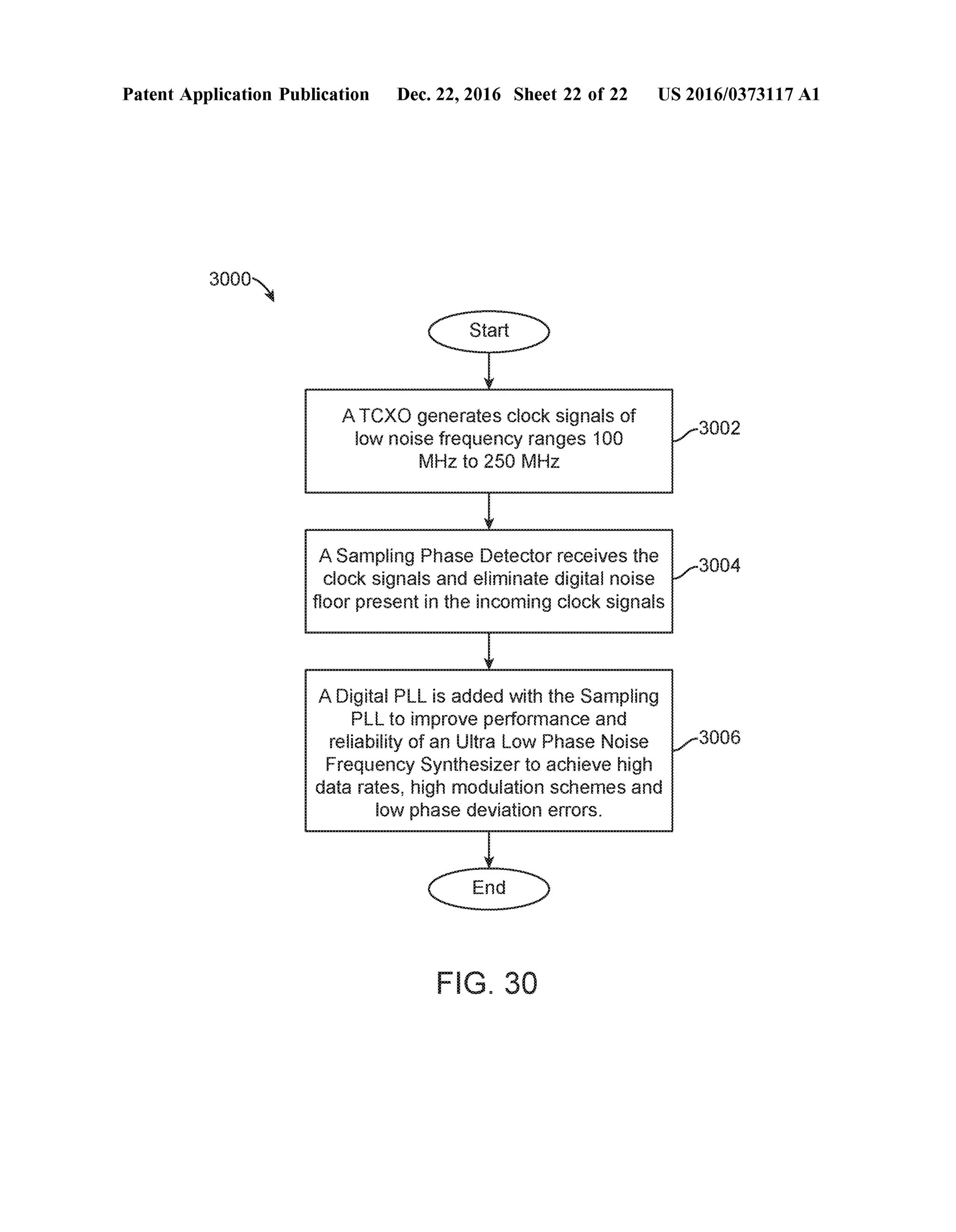

The document describes a patent application for an ultra low phase noise frequency synthesizer aimed at improving wireless communication systems. It outlines the system's components, including a fractional-N PLL (phase lock loop), sampling reference PLL, and direct digital synthesizer, which are designed to reduce phase noise and enhance modulation schemes for higher data rates. This innovation targets the performance limitations of current frequency synthesizers and addresses issues related to phase deviation errors.