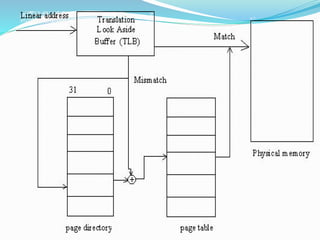

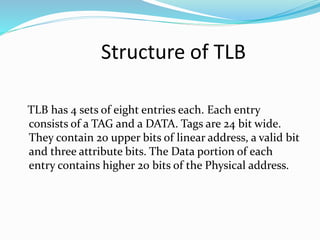

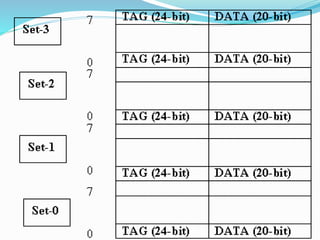

The document provides an overview of the Translation Lookaside Buffer (TLB), which acts as a cache for page table entries to simplify the process of translating linear addresses to physical addresses. It explains the function of the TLB, including its structure, how it works with content addressable memory, and the costly page walk process involved when a TLB miss occurs. The TLB optimizes memory access by storing recently accessed entries, enhancing performance through locality of reference.