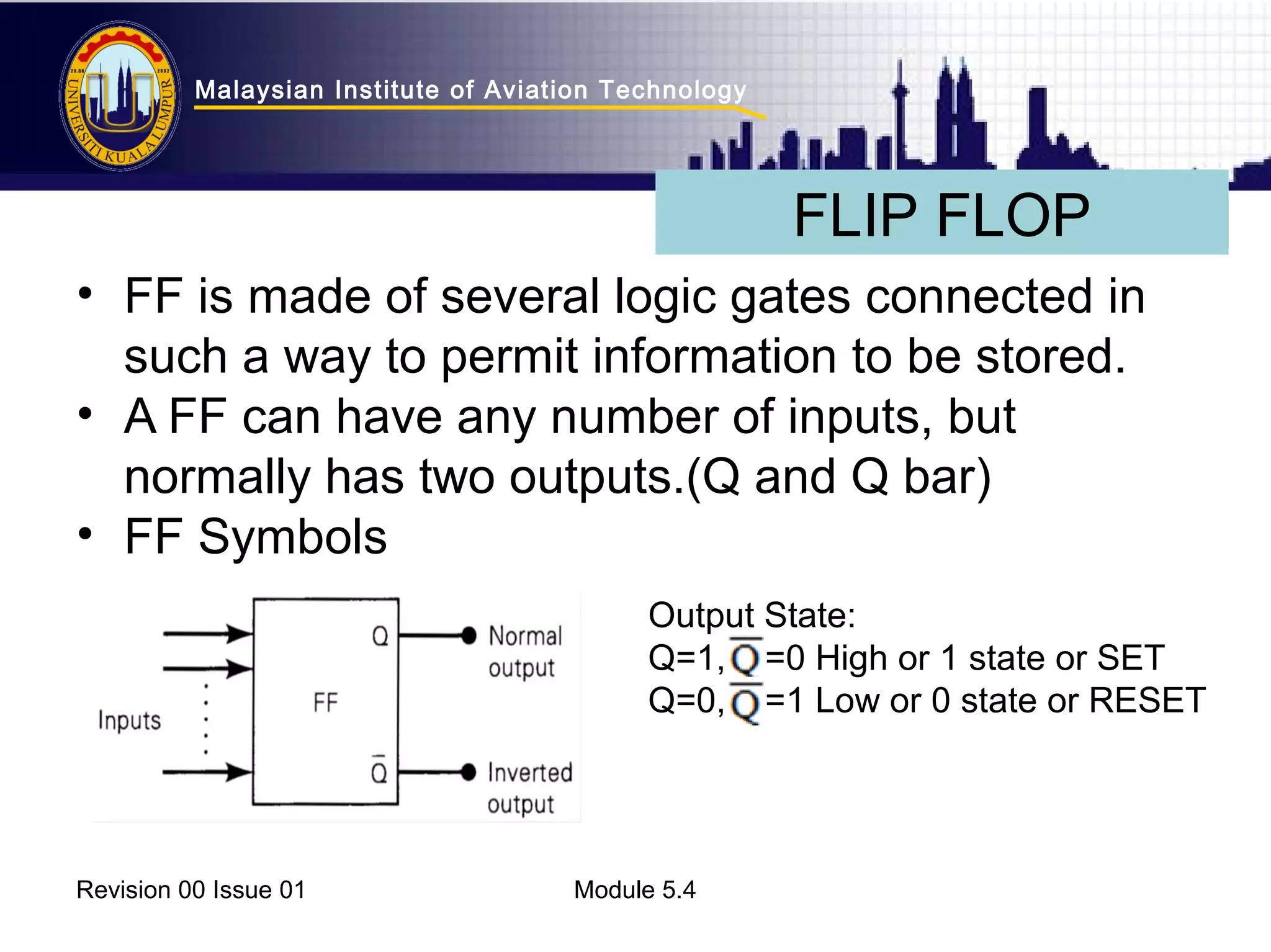

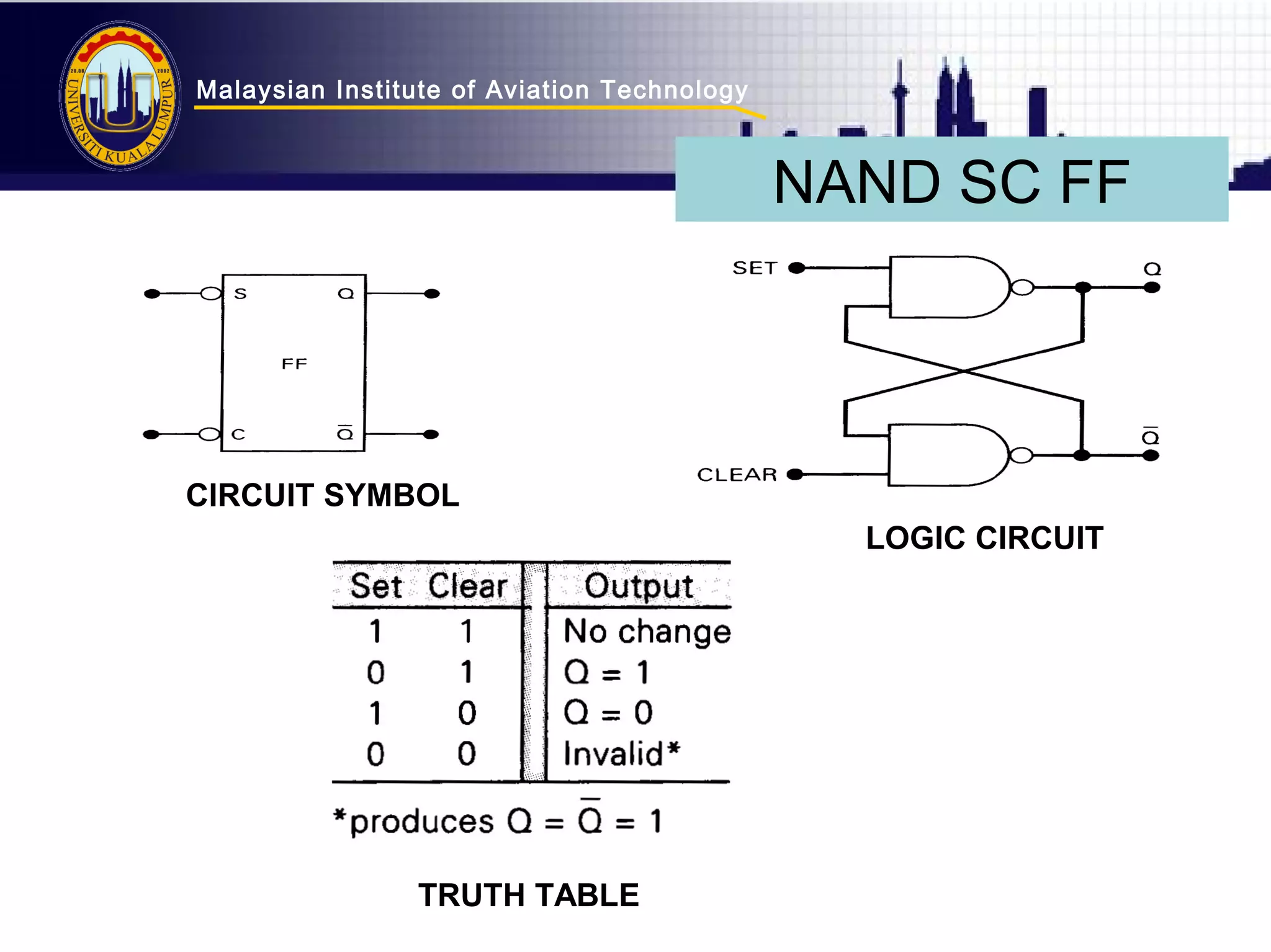

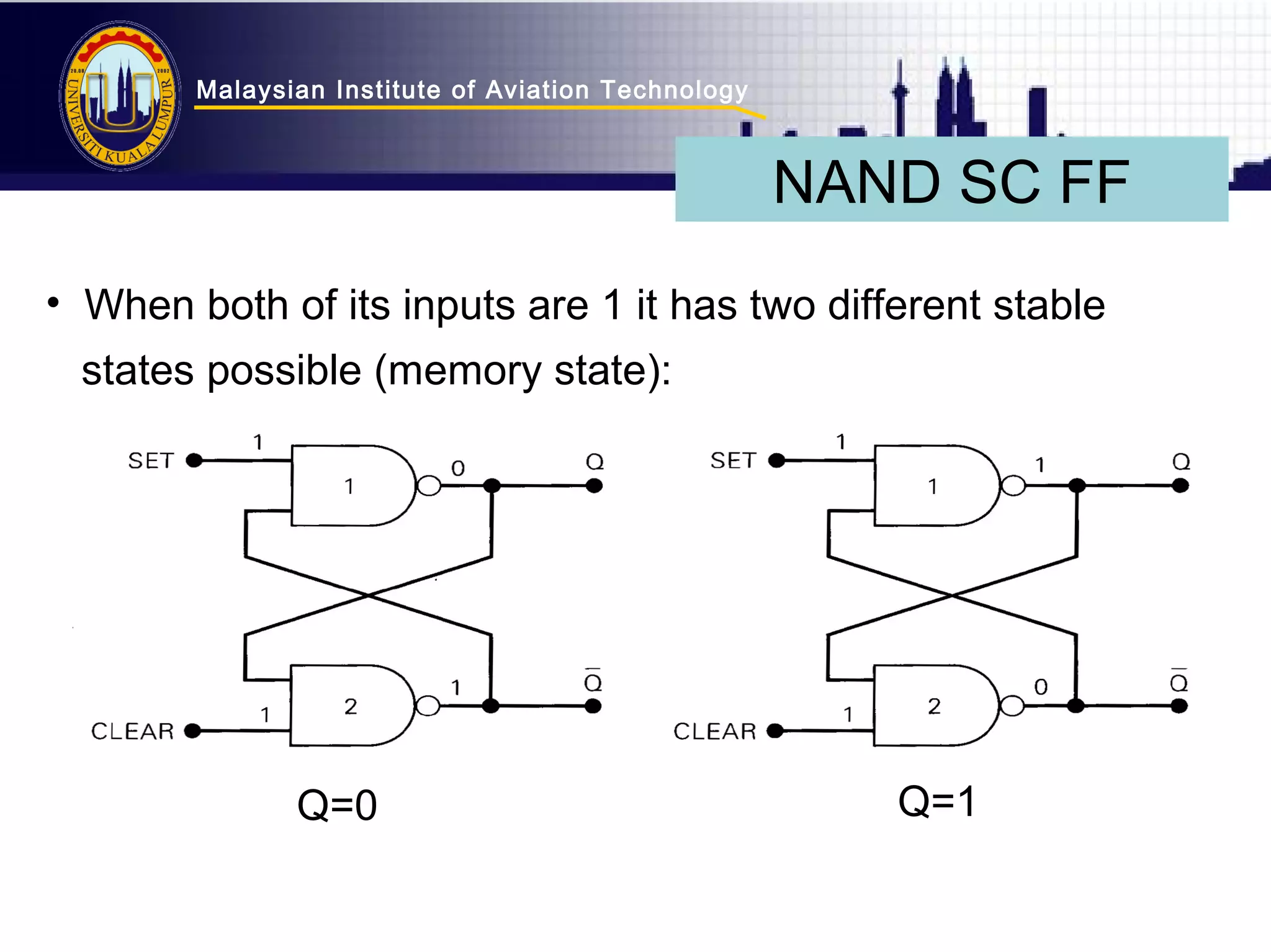

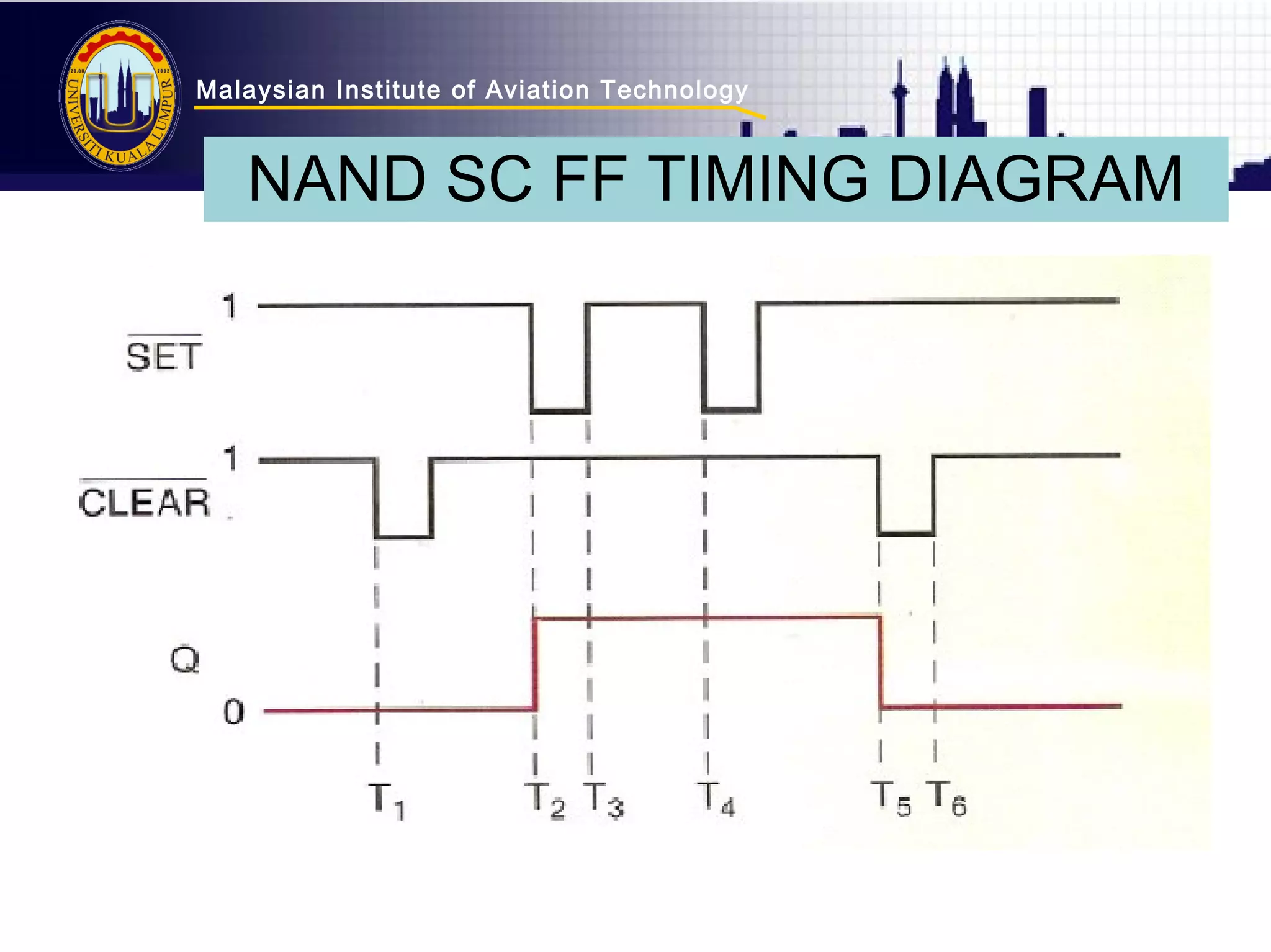

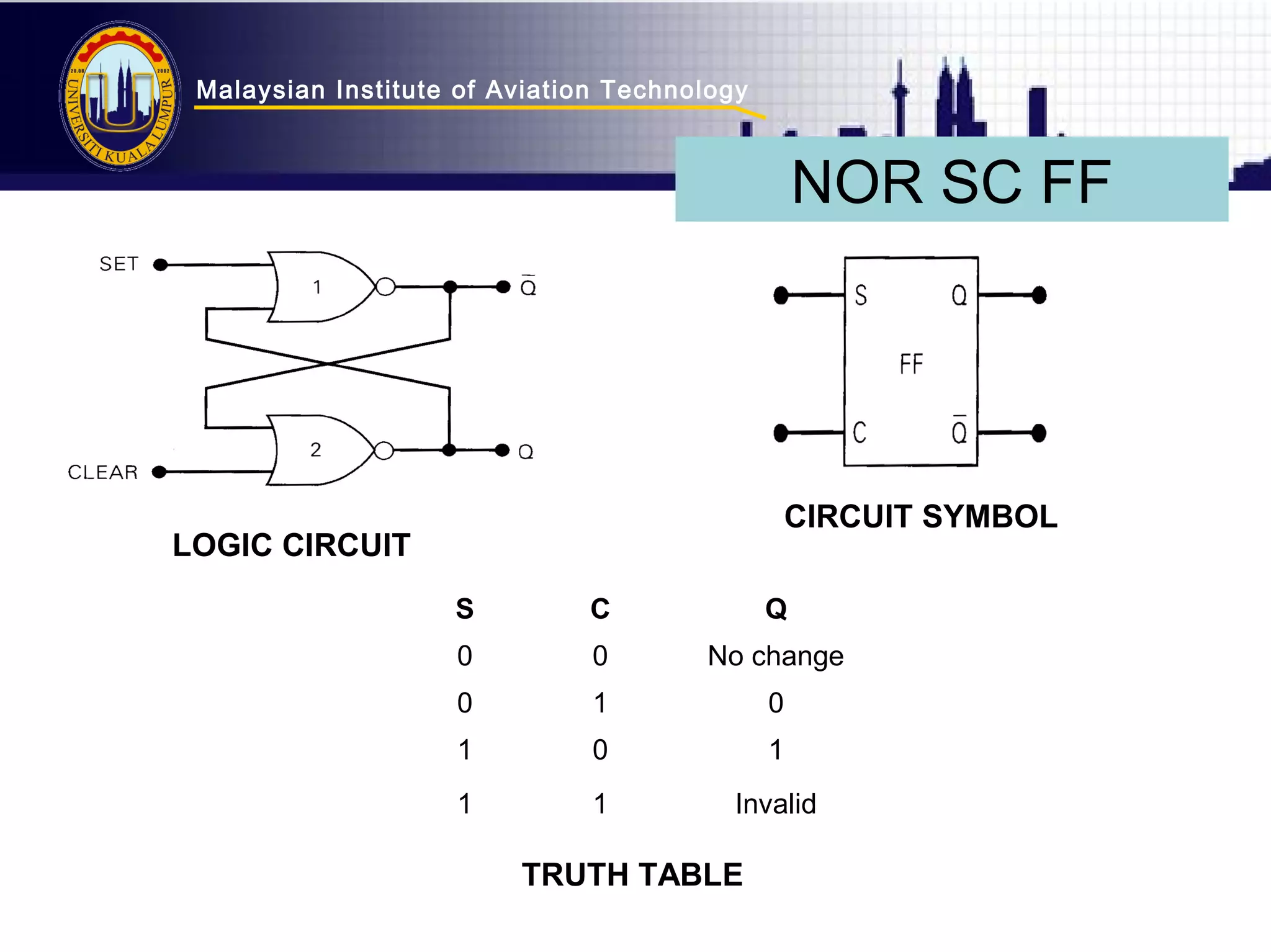

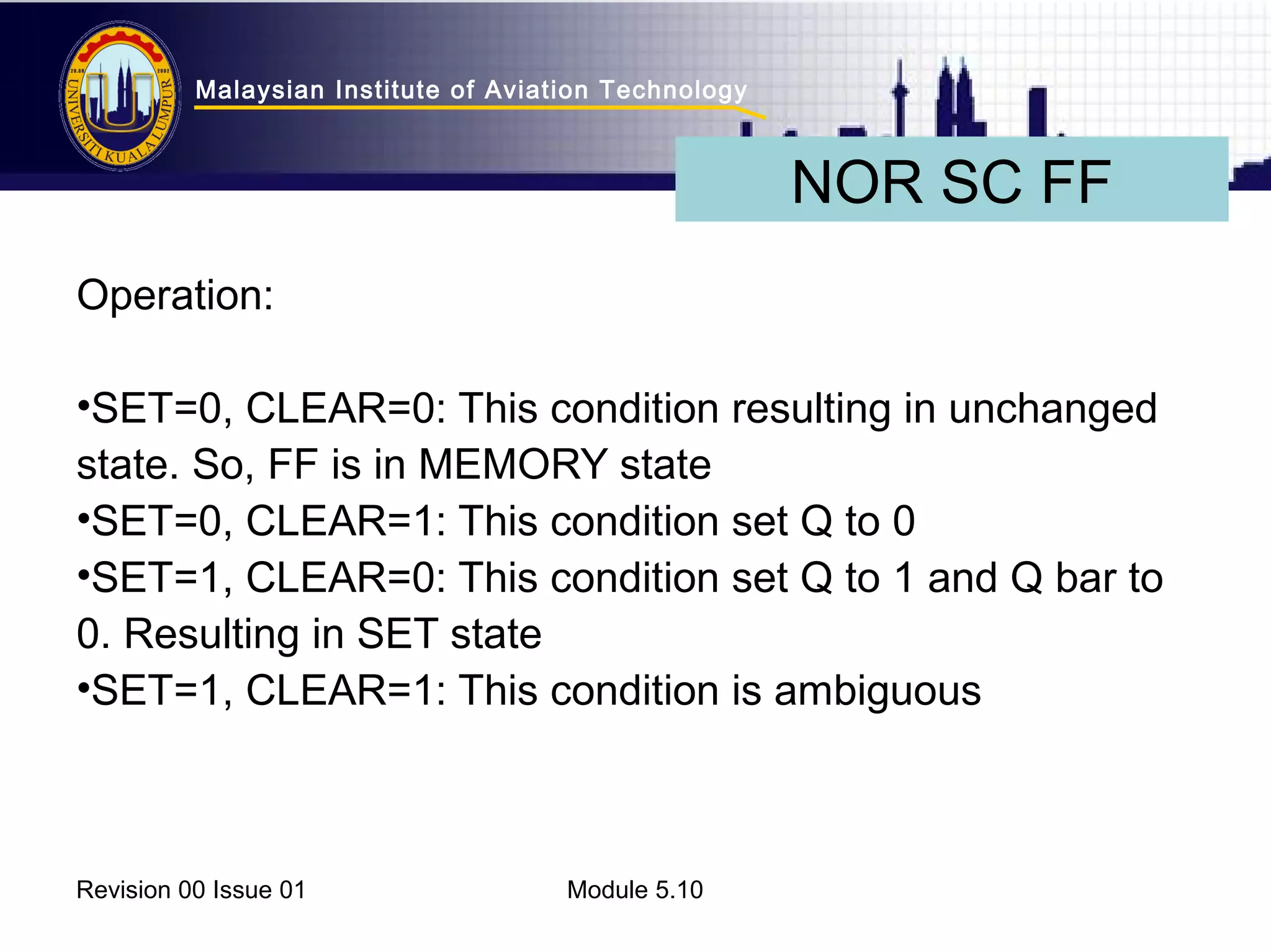

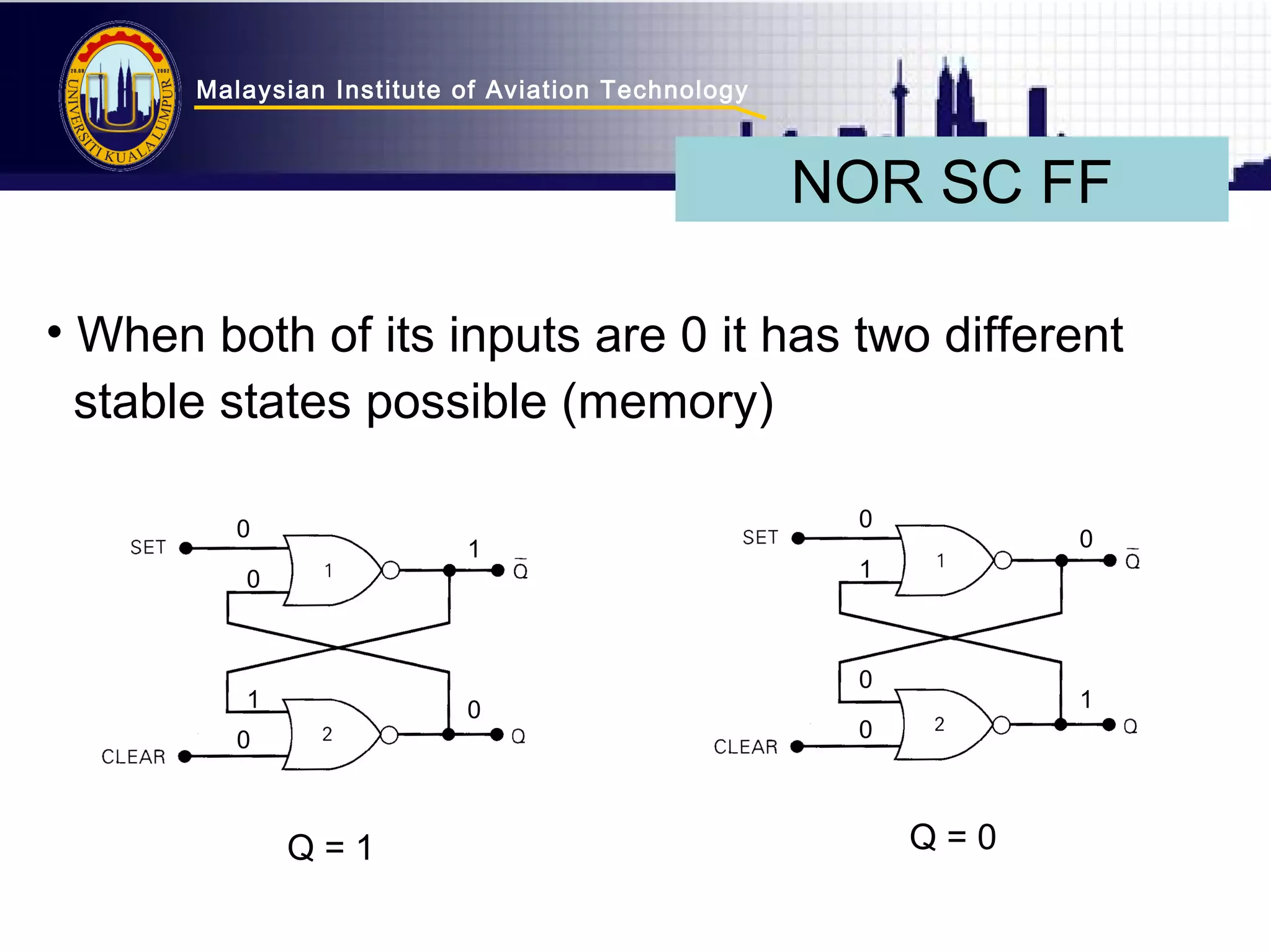

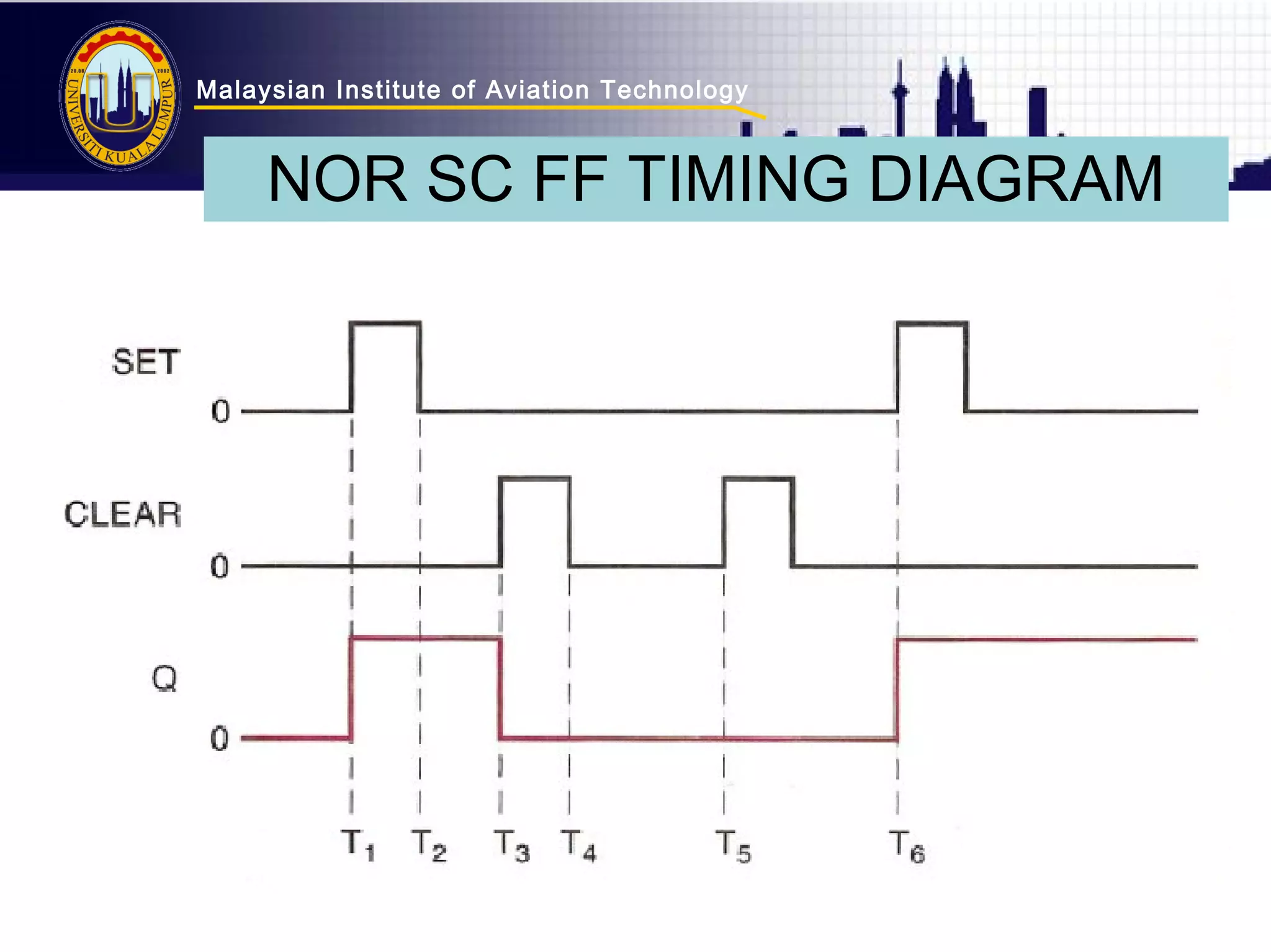

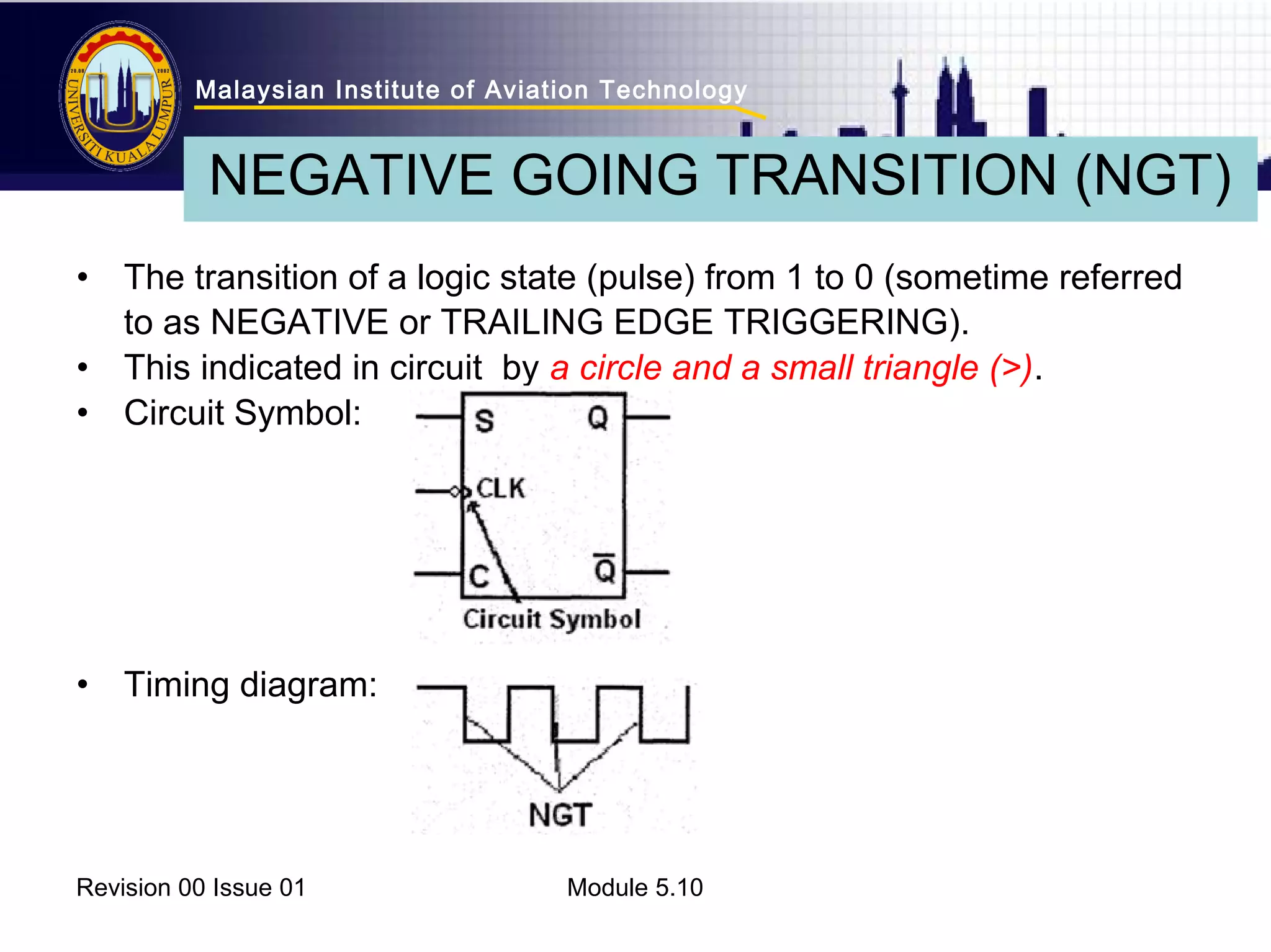

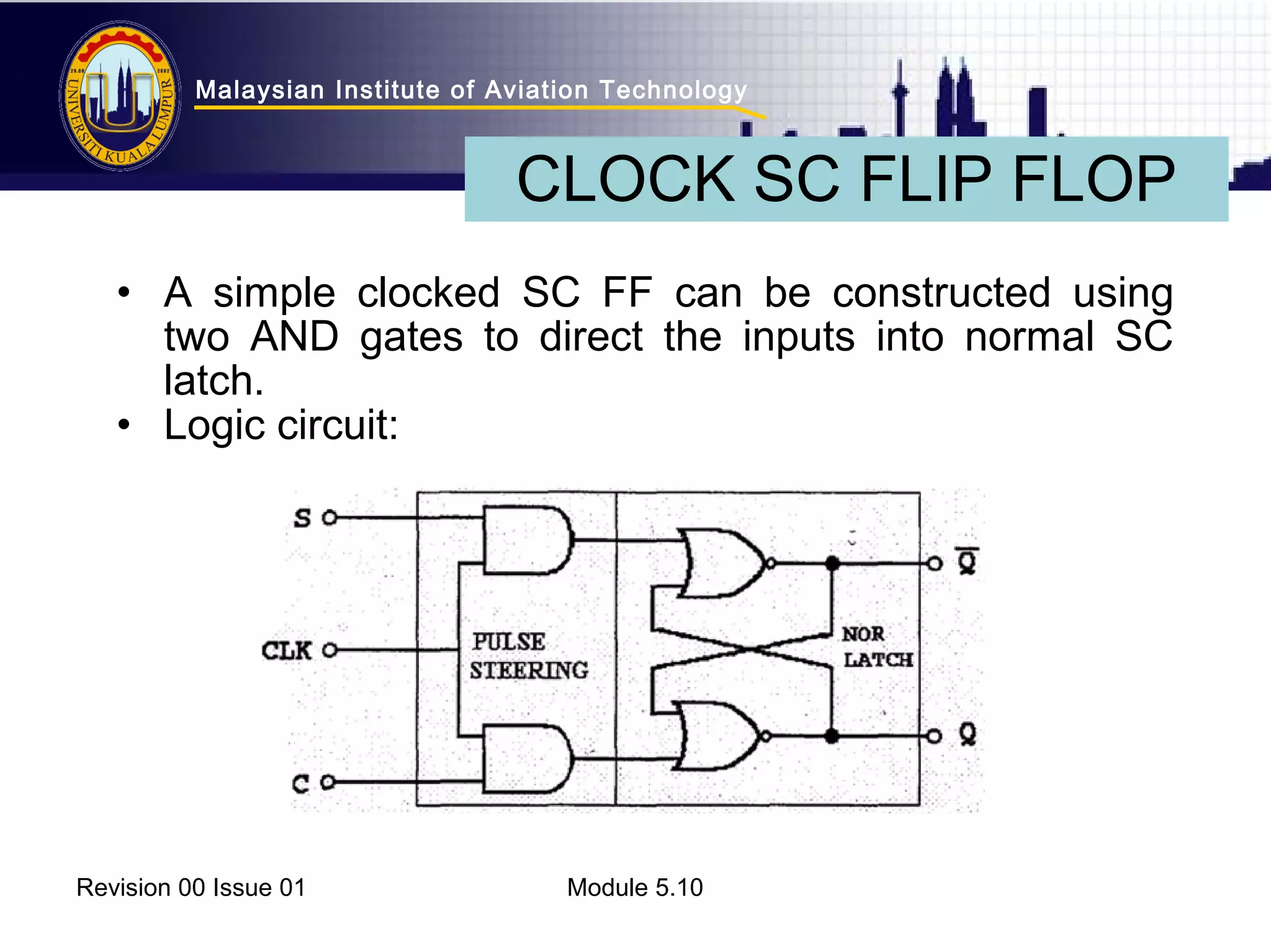

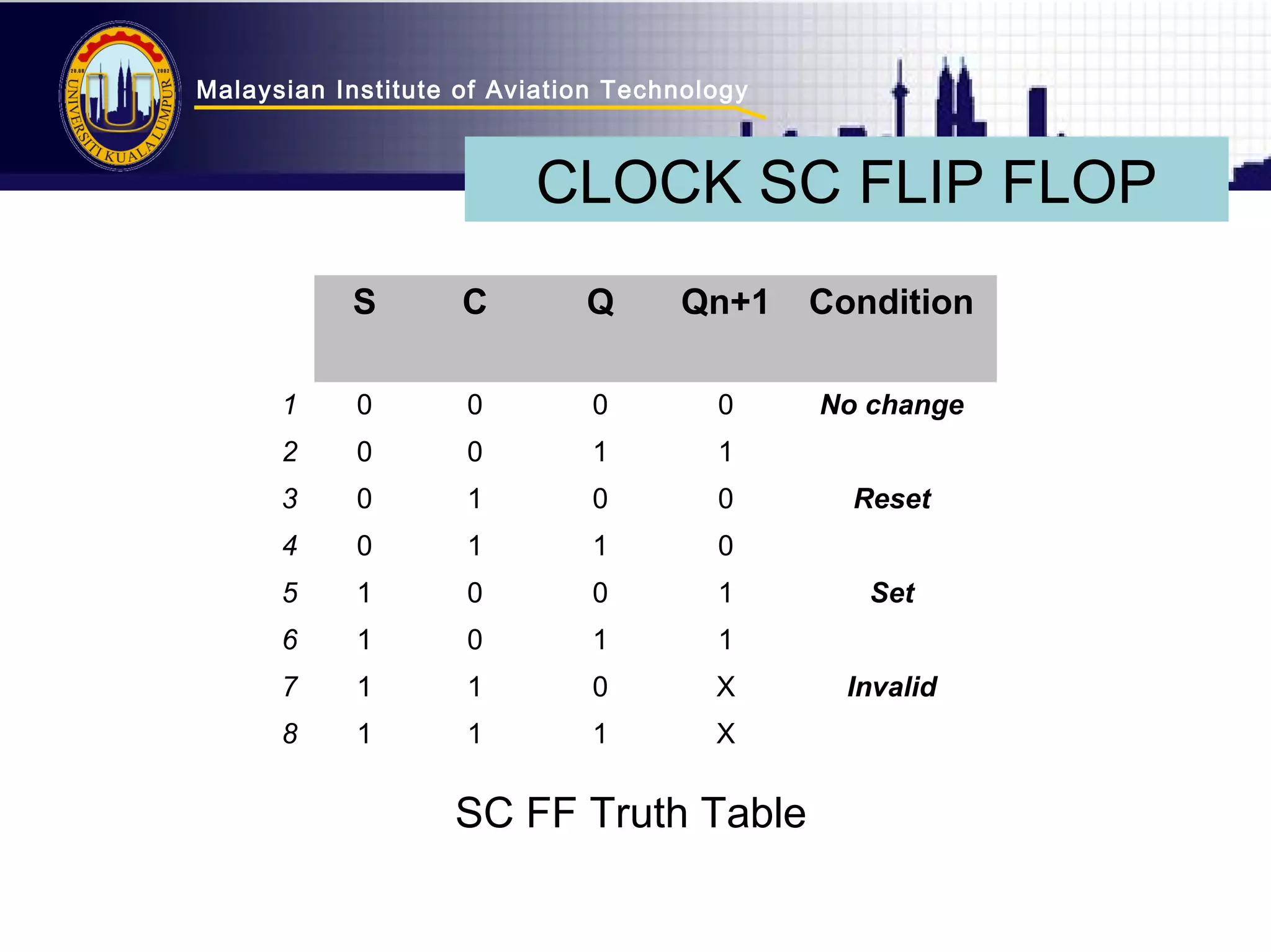

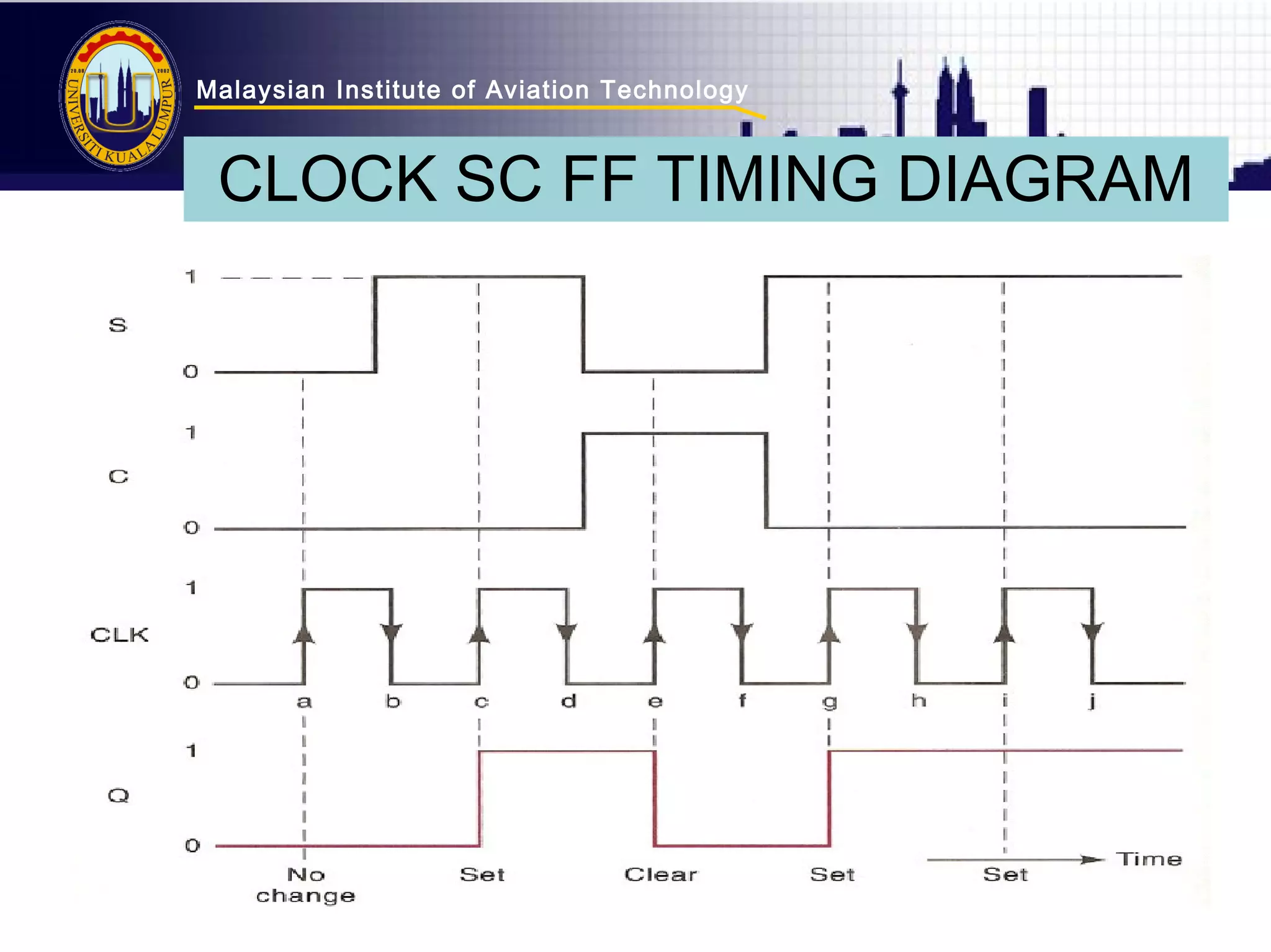

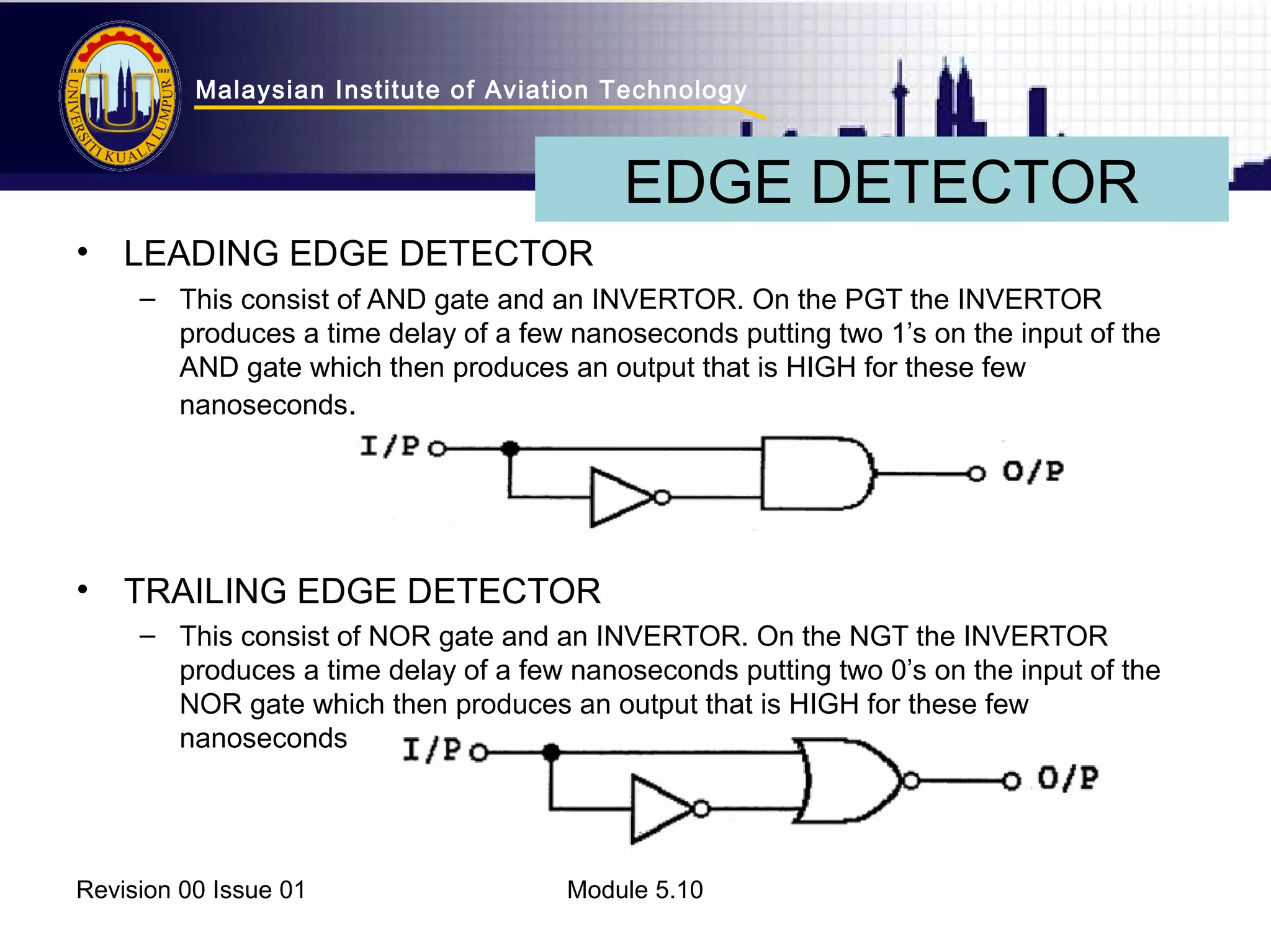

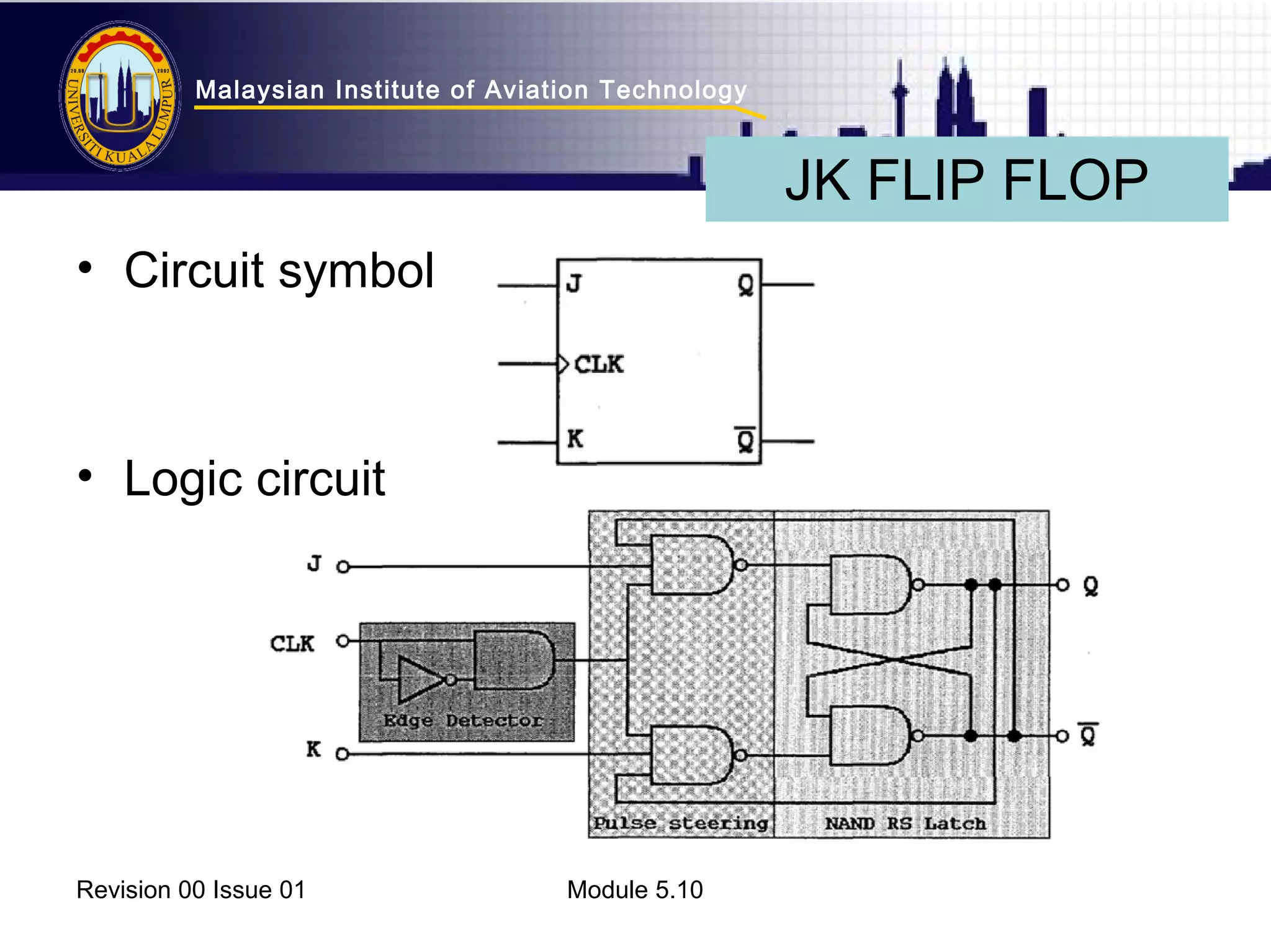

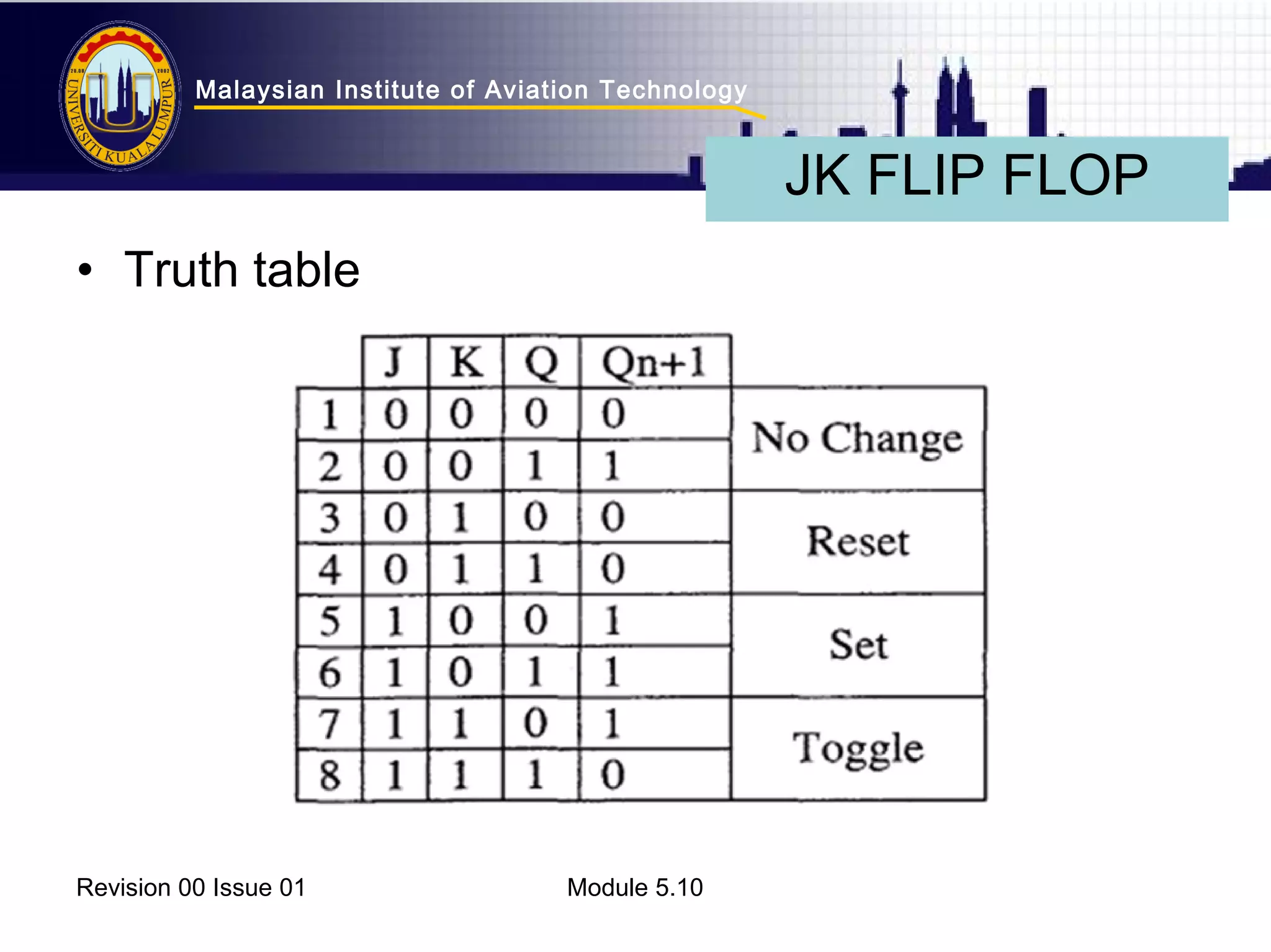

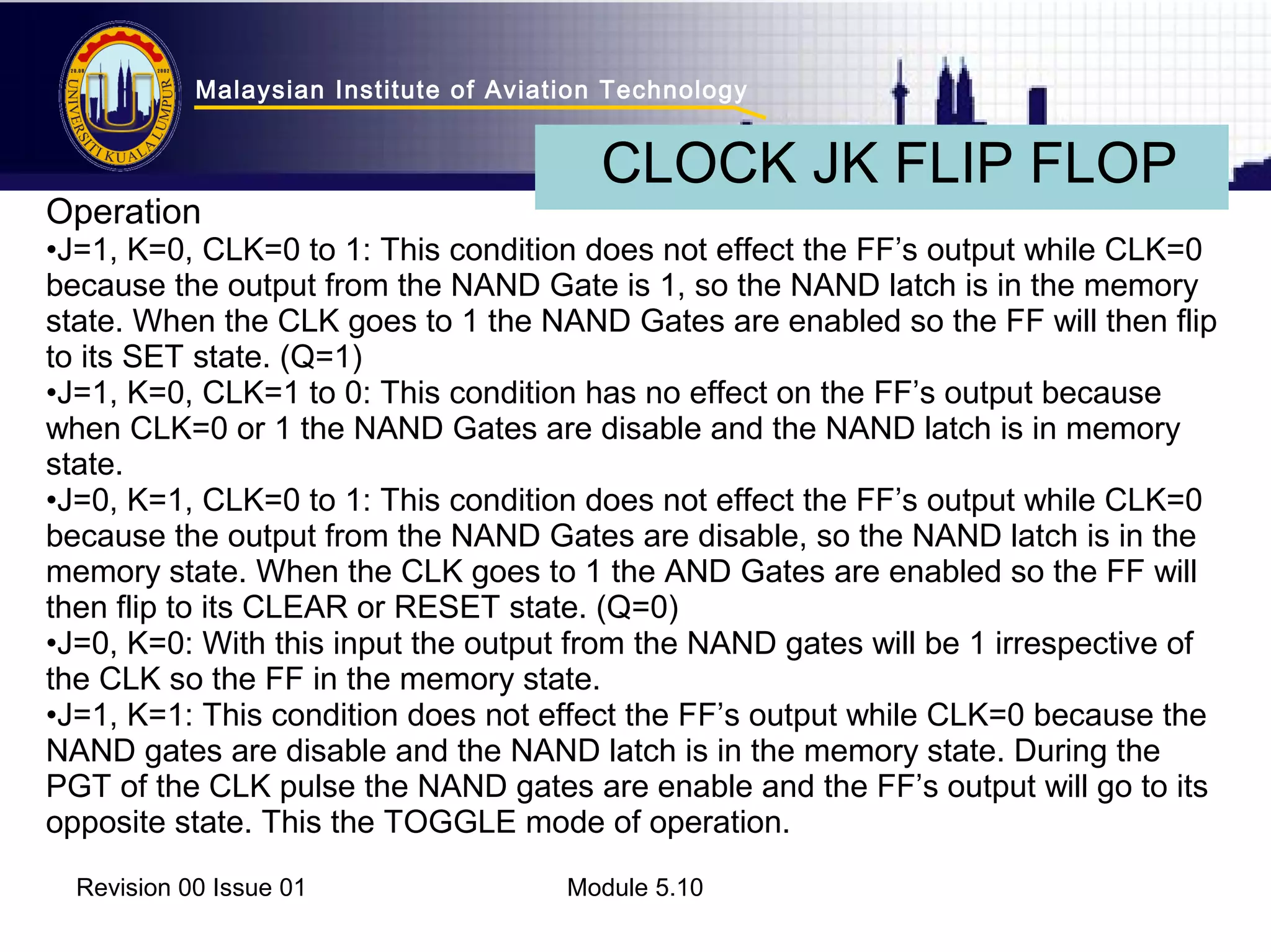

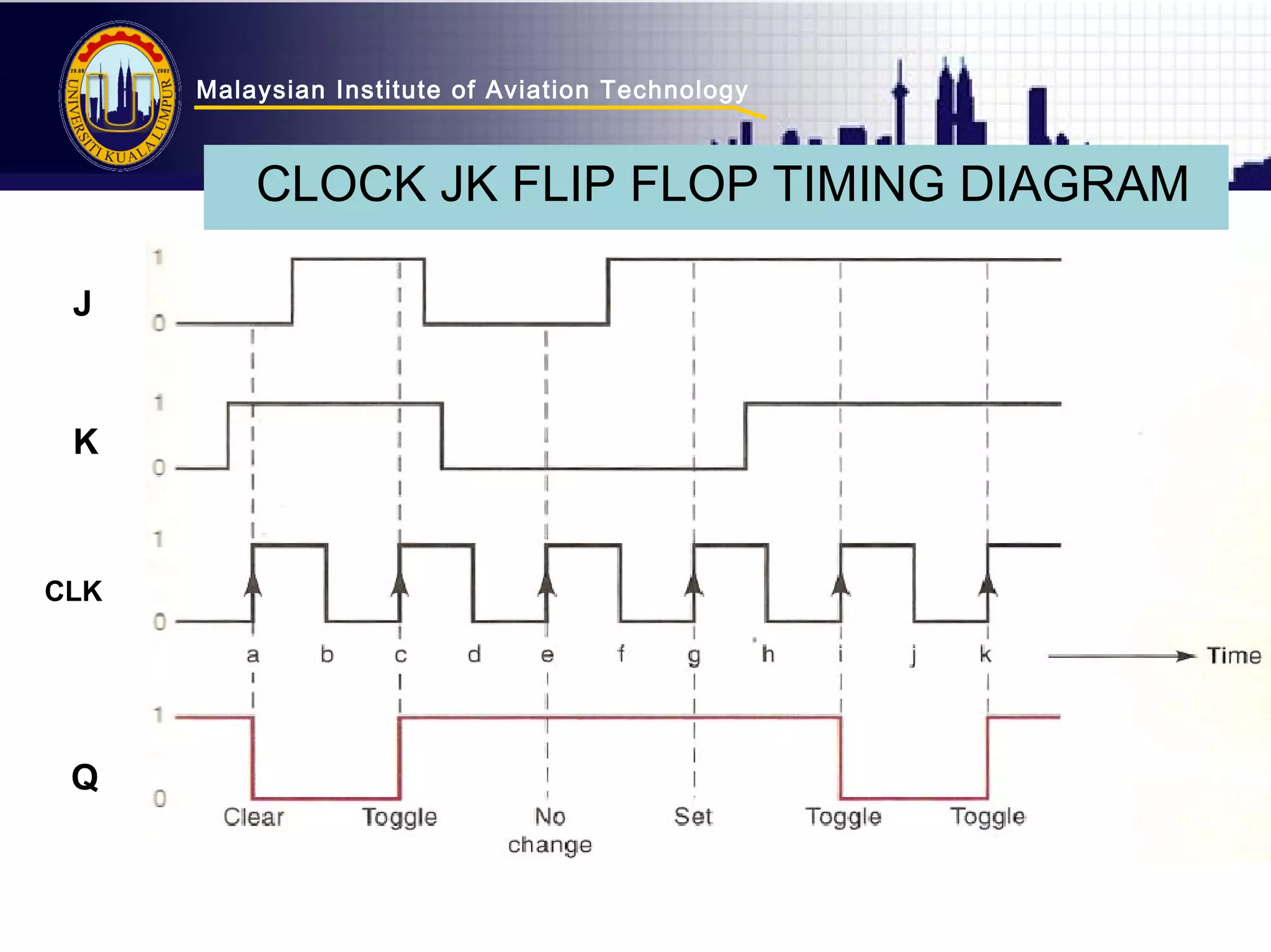

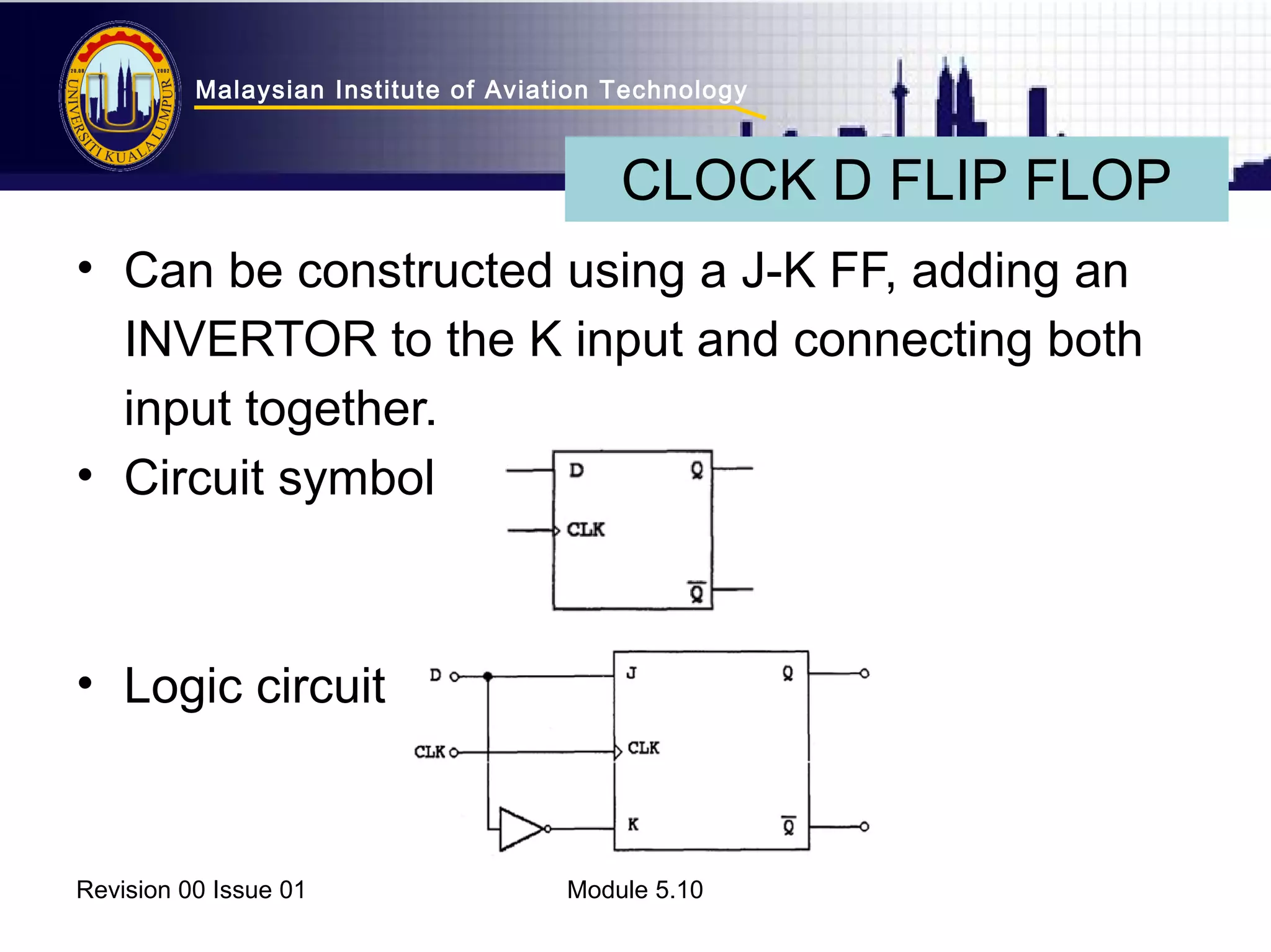

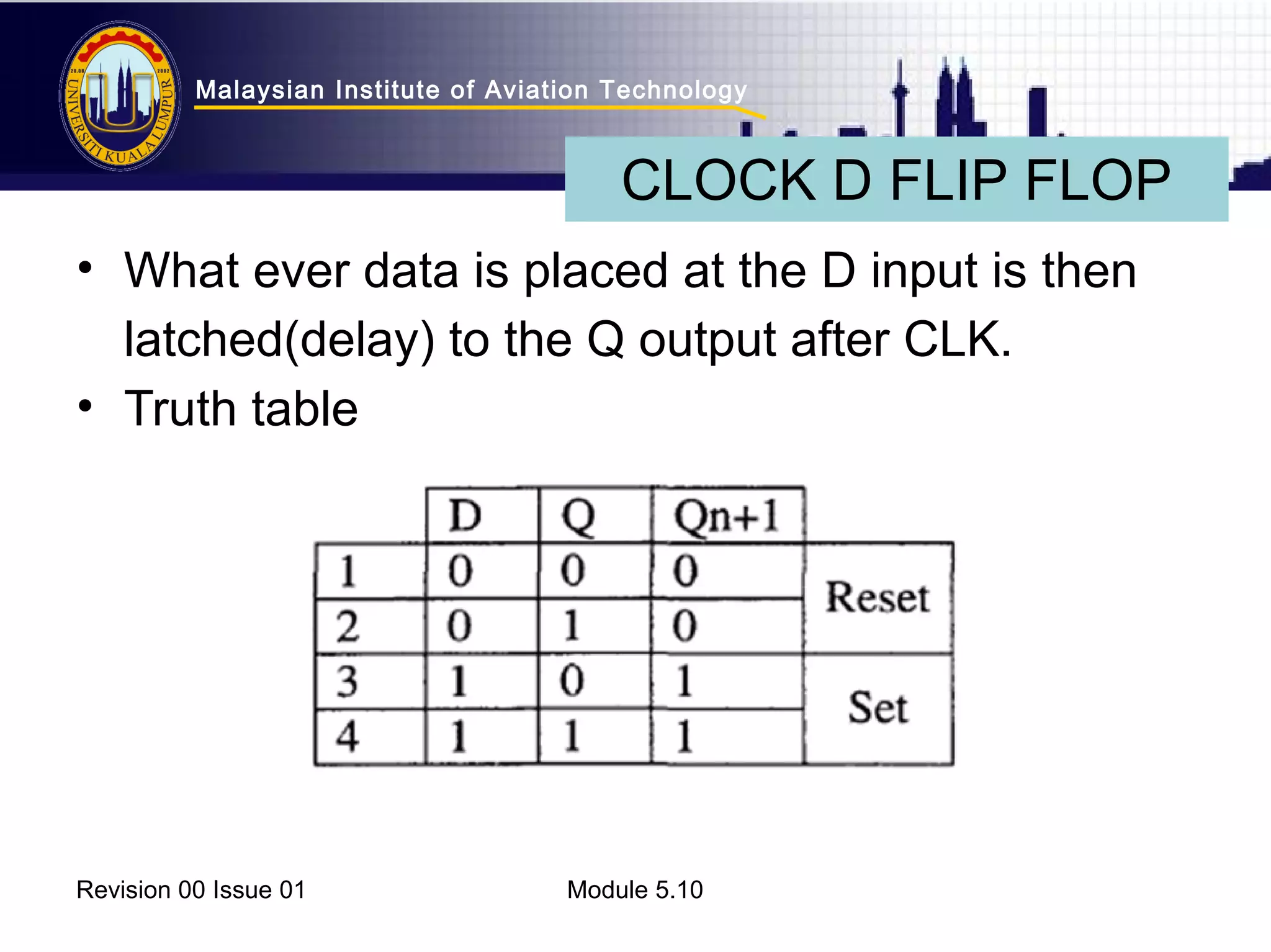

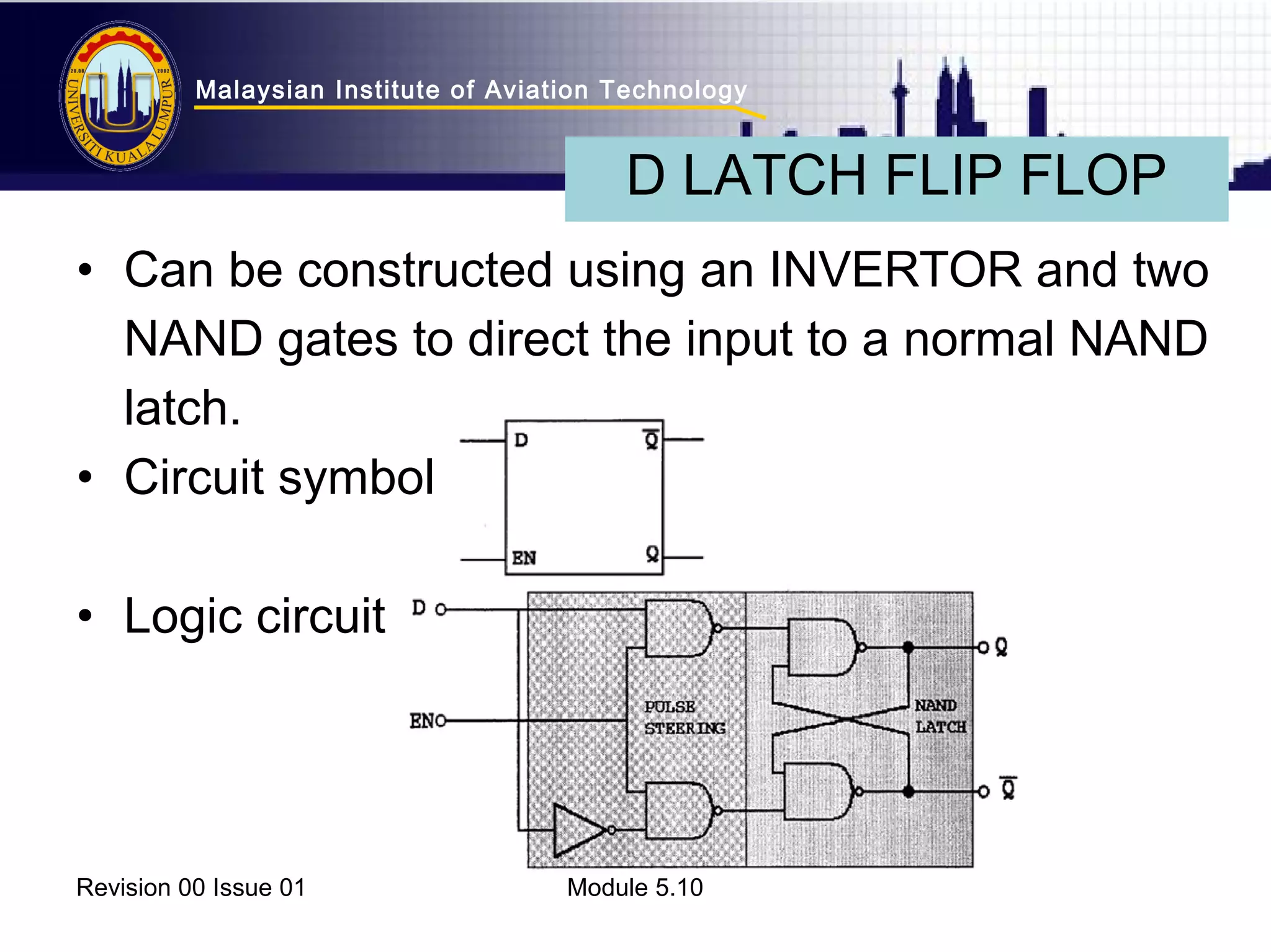

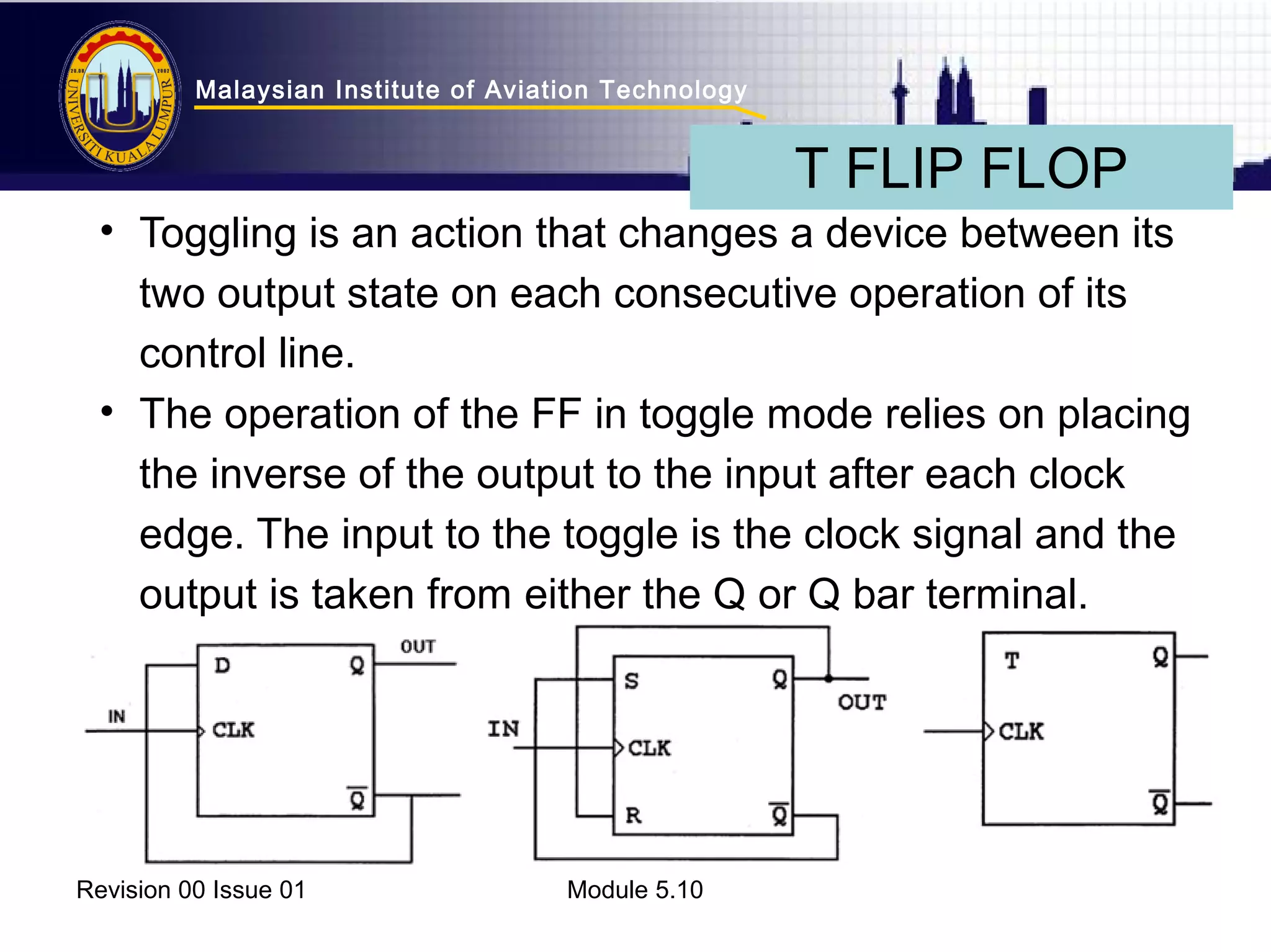

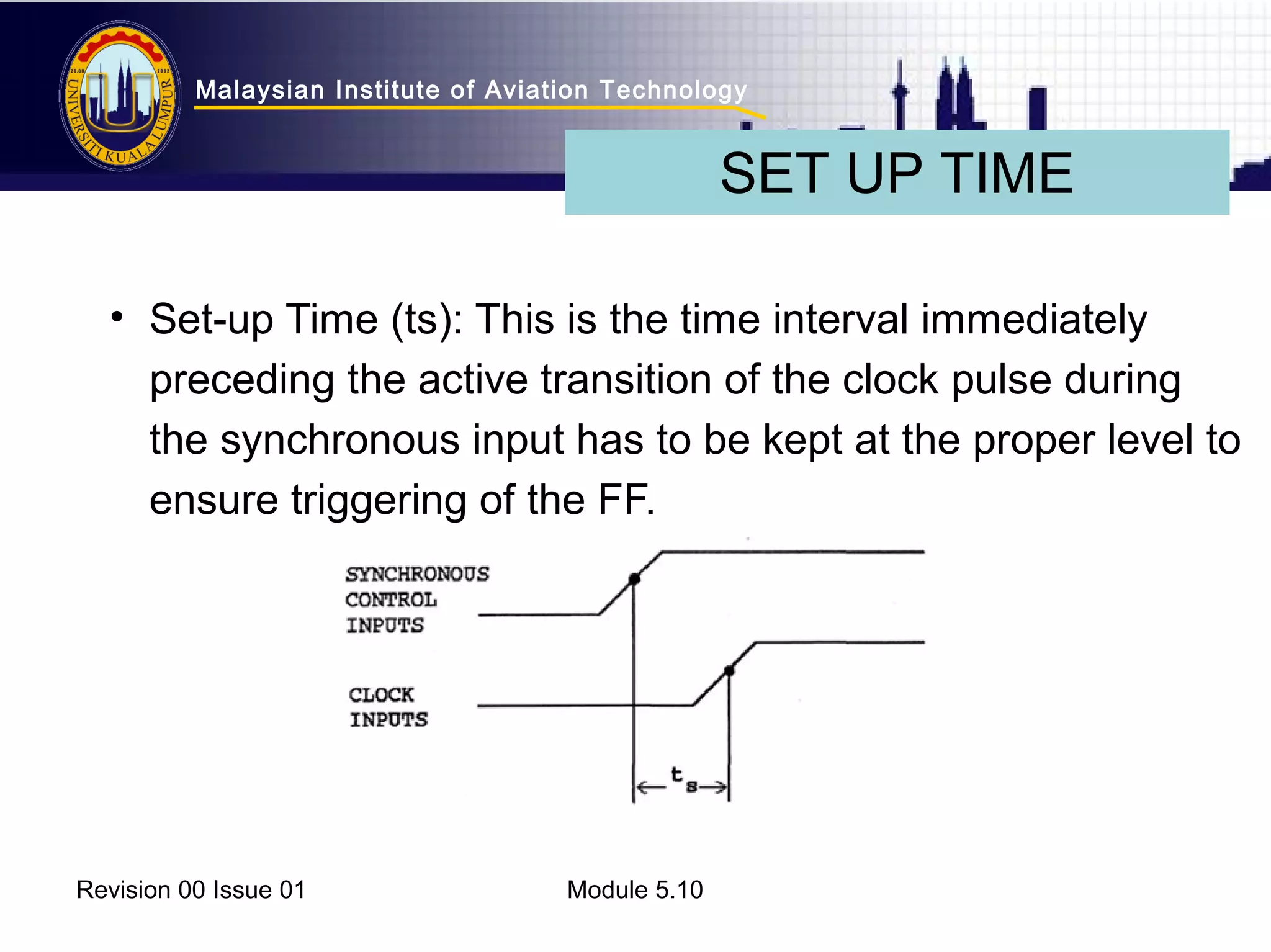

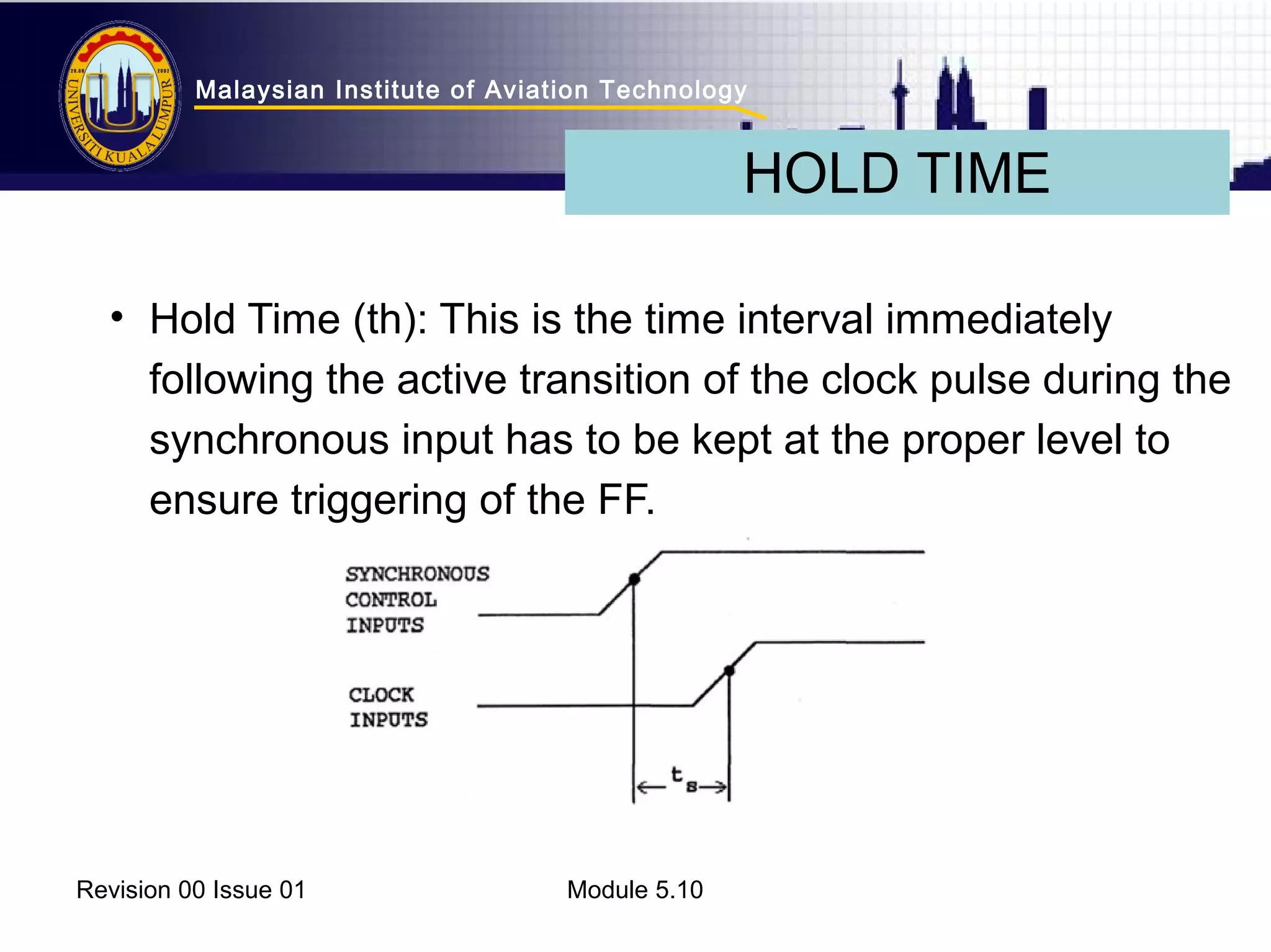

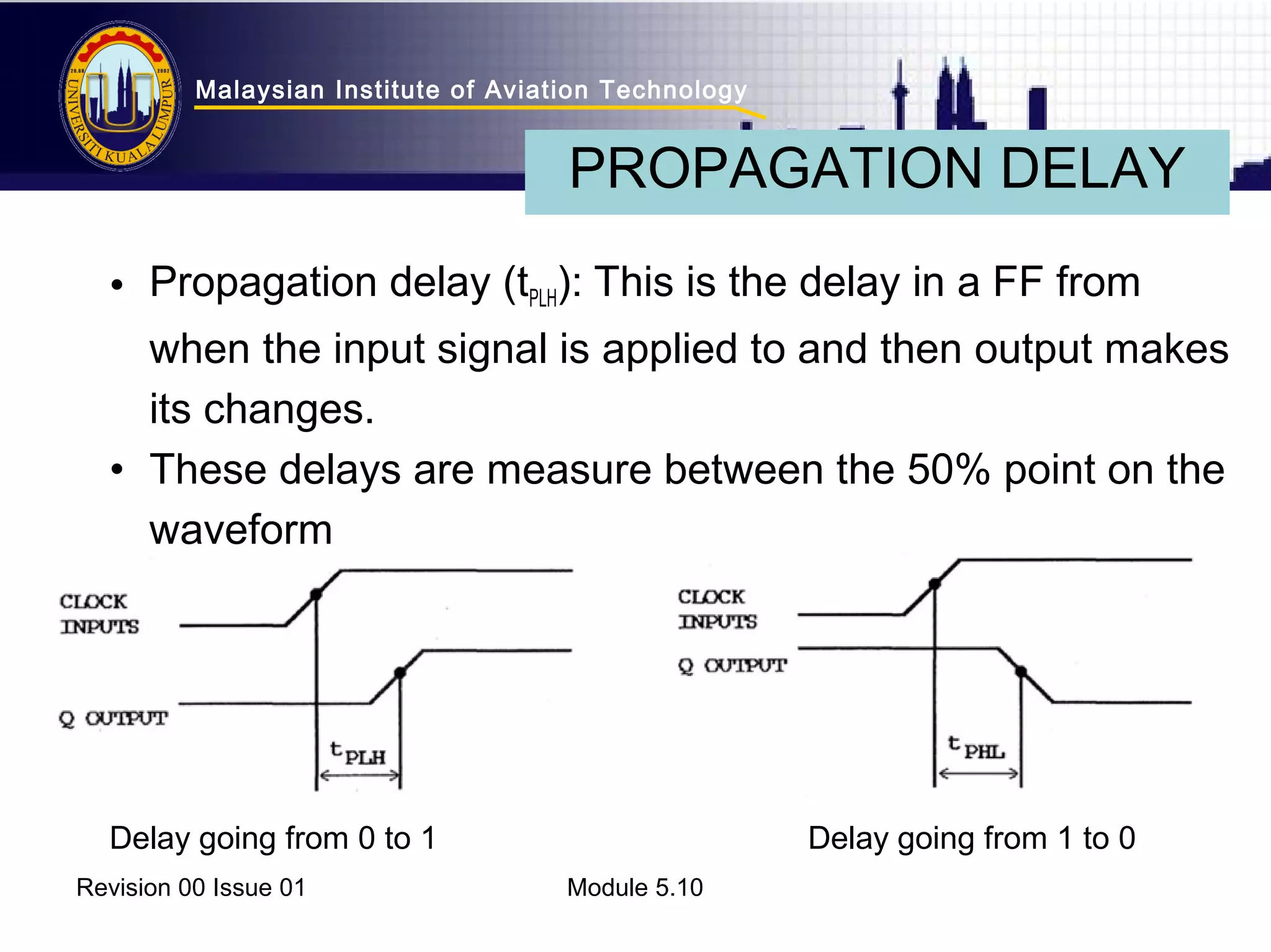

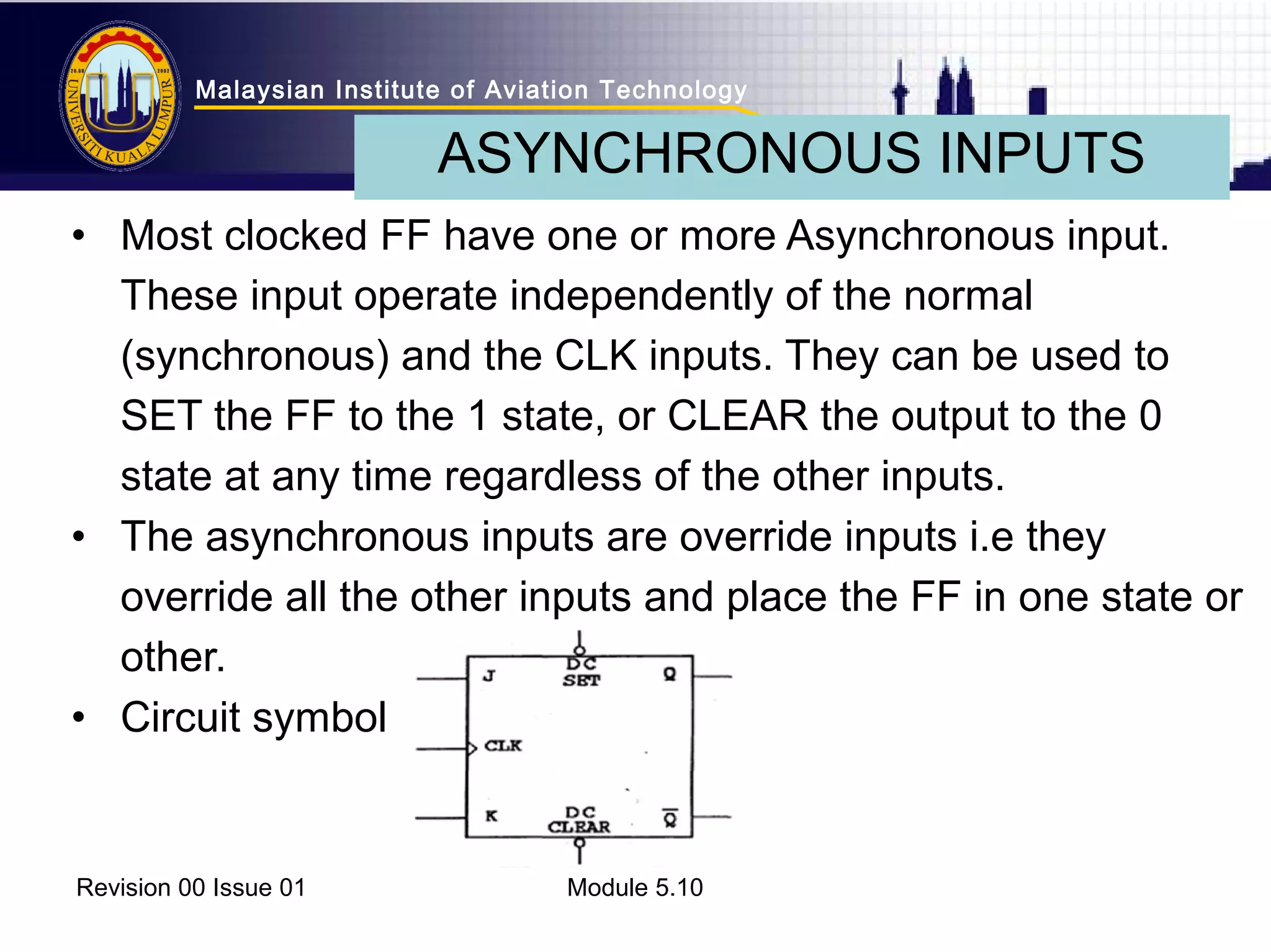

This document provides information on flip-flops, including their terminology, types of flip-flops, and their circuit symbols, truth tables, and operations. It discusses NAND and NOR SR flip-flops, clocked SR flip-flops, JK flip-flops, D flip-flops, D latches, T flip-flops, and factors that affect flip-flop reliability such as setup time, hold time, and propagation delay. Asynchronous inputs are also covered, which can override other inputs to set or clear a flip-flop.