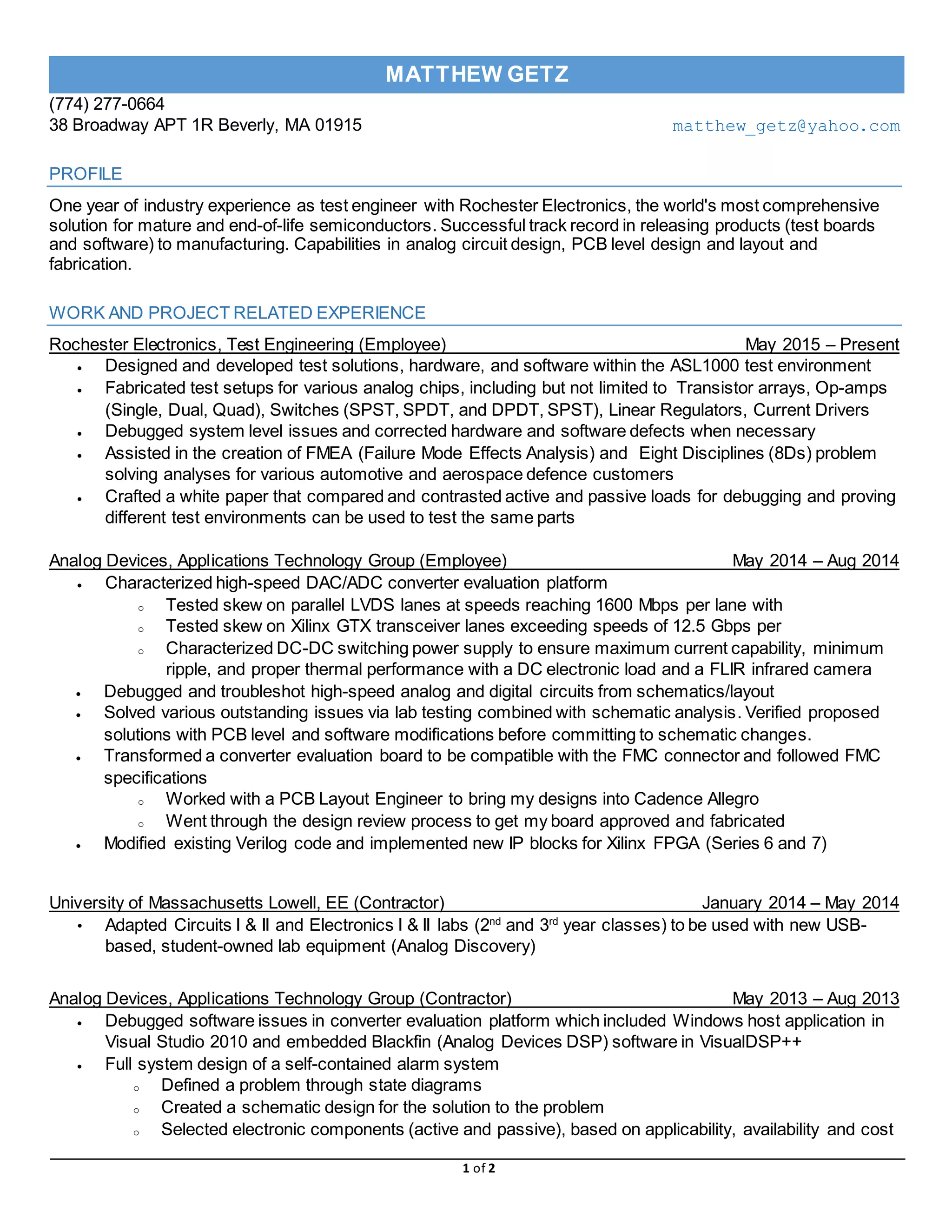

Matthew Getz has over 5 years of experience in engineering roles, including as a test engineer and contractor. He has experience designing test hardware and software, characterizing analog and digital circuits, and modifying FPGA code. He has a Bachelor's degree in Electrical Engineering and skills in programming, PCB design, and using test equipment.