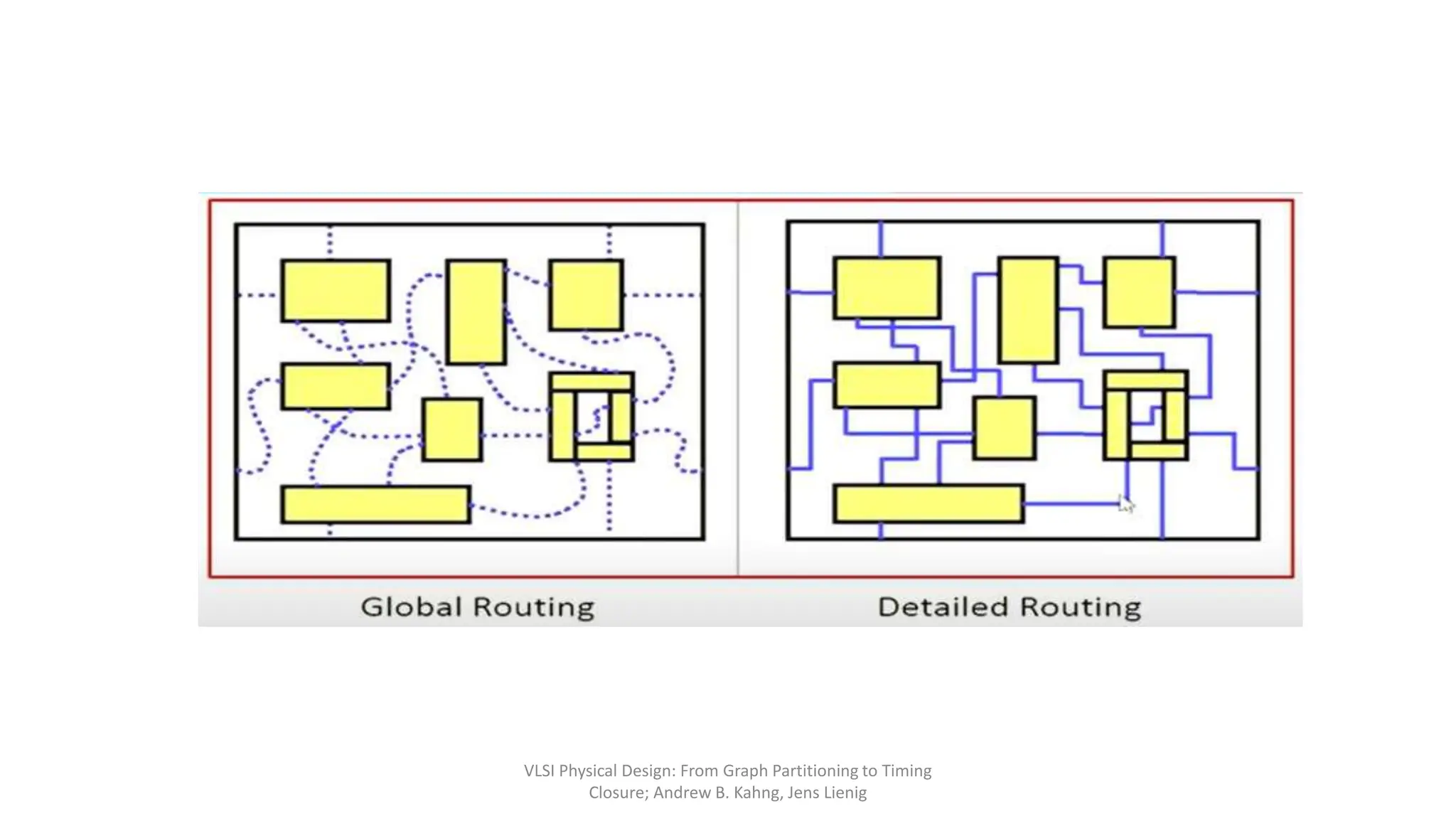

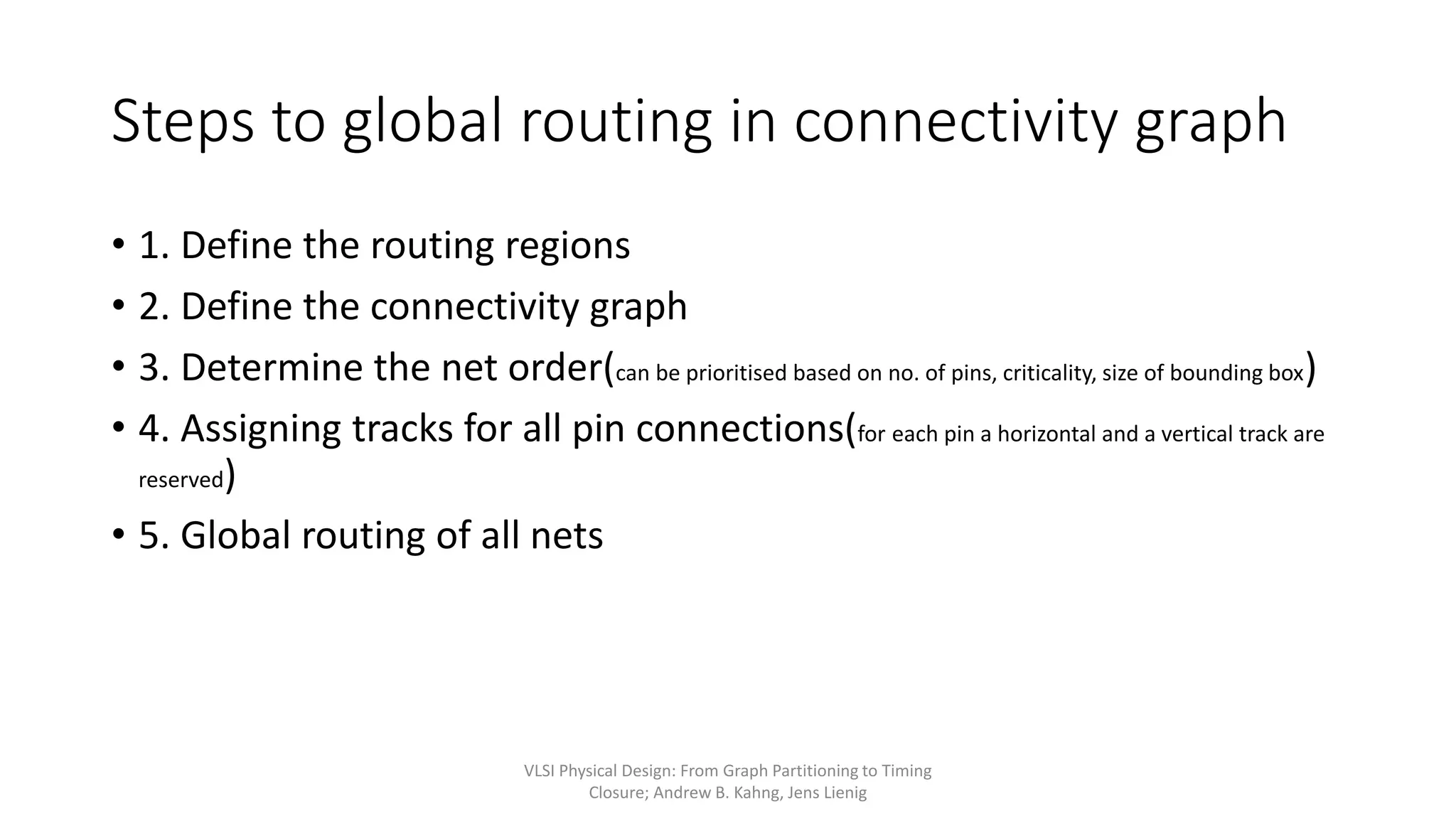

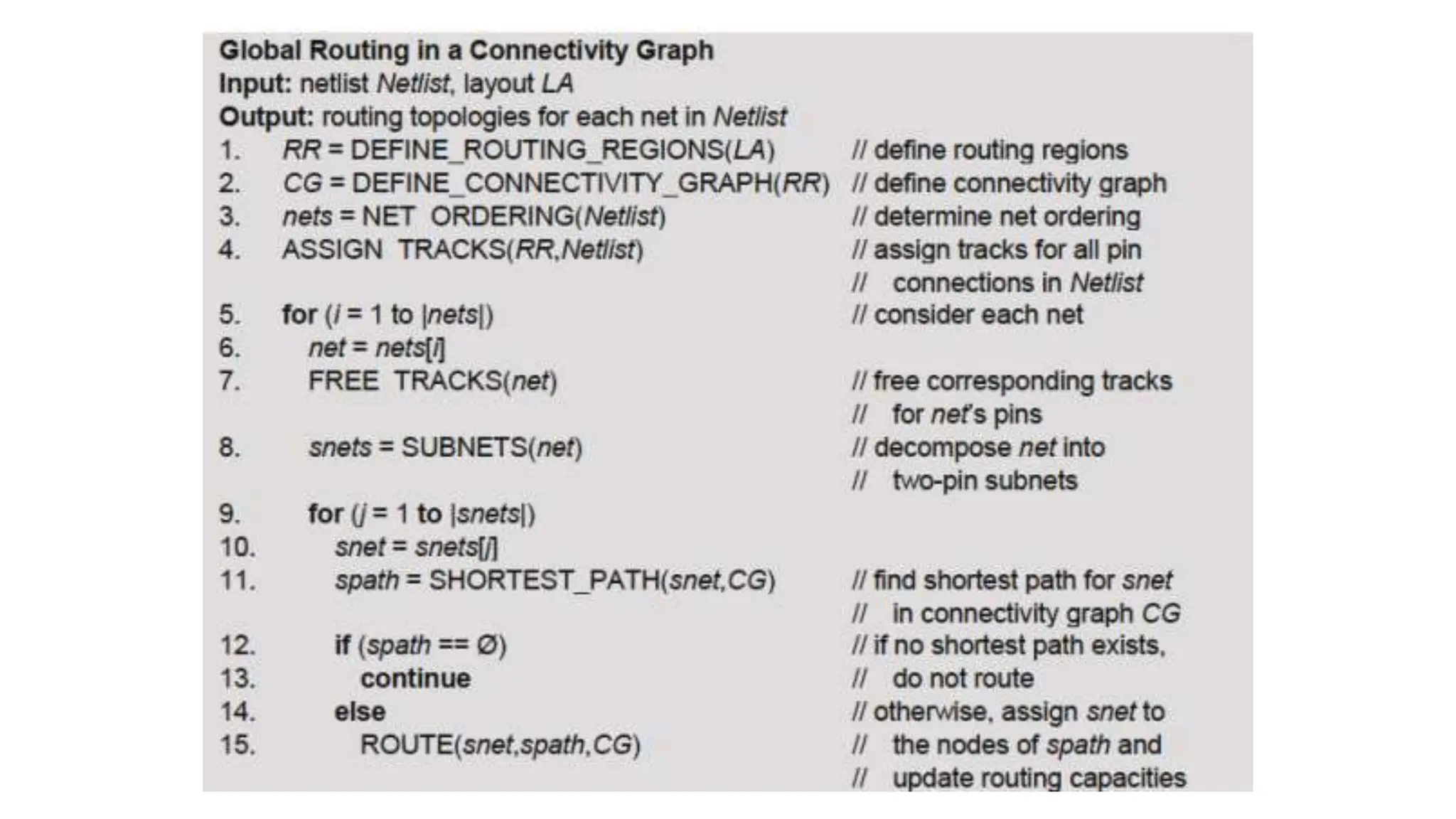

1) Global routing assigns nets to metal layers and routing cells in an approximate manner, while detailed routing decides the physical interconnections by allocating wires and vias.

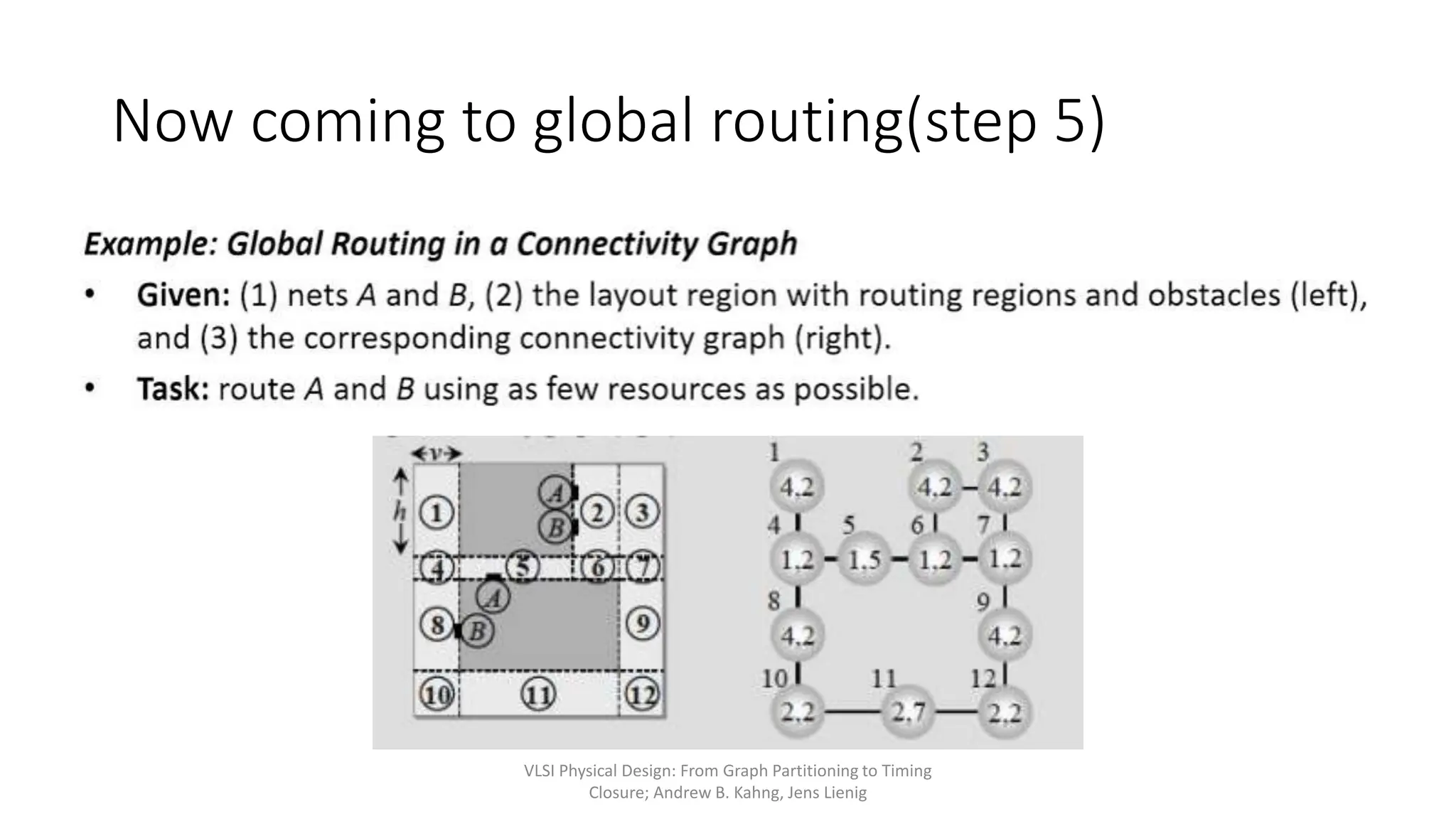

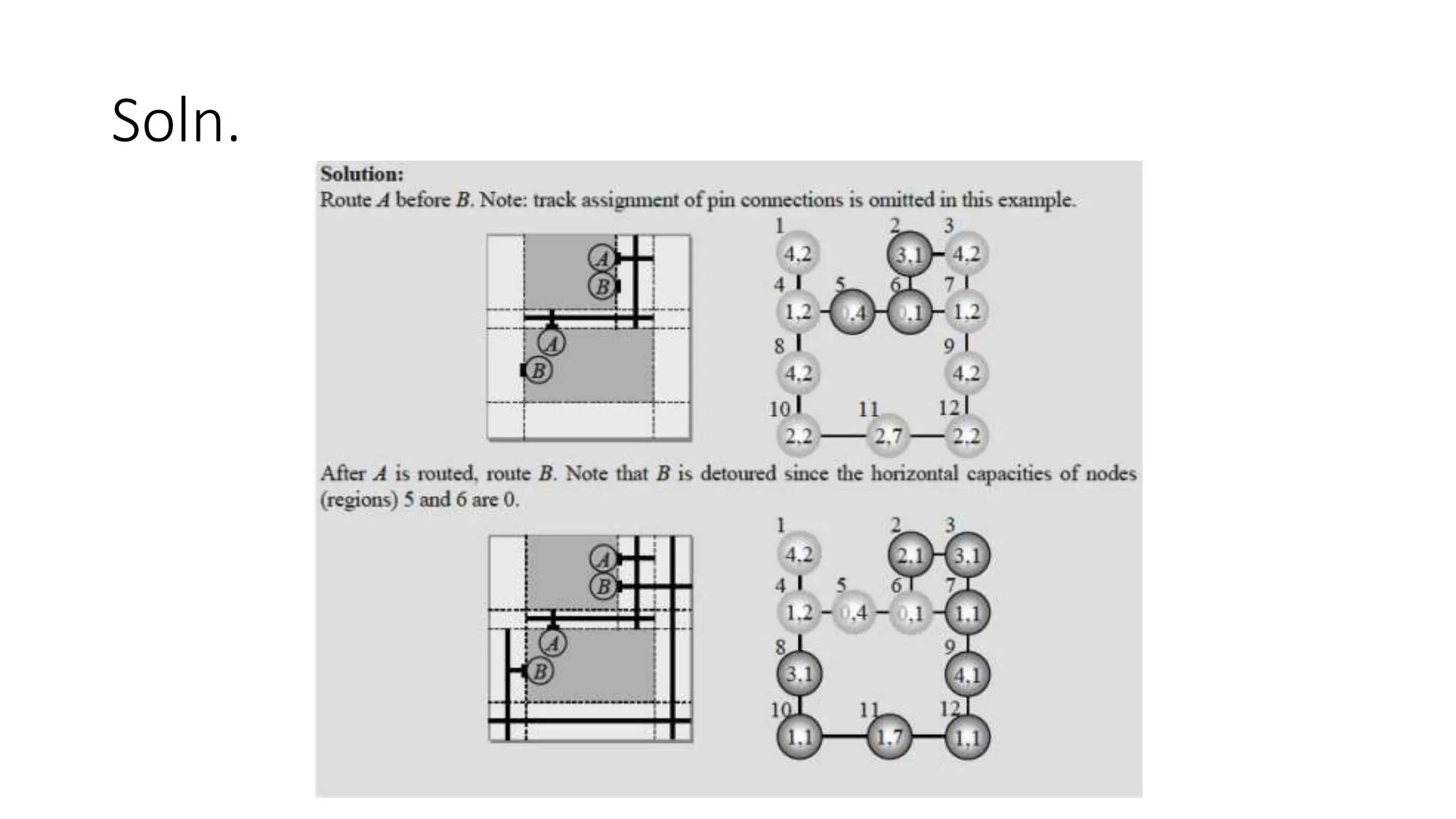

2) Global routing seeks to determine if a placement is routable and finds a coarse routing for all nets within available regions.

3) Integer linear programming formulations model routing as a set of linear constraints and objectives and find optimal integer solutions for variable assignments.