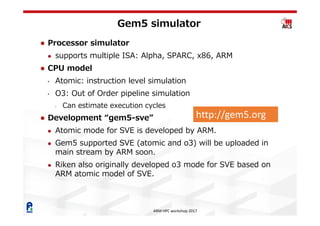

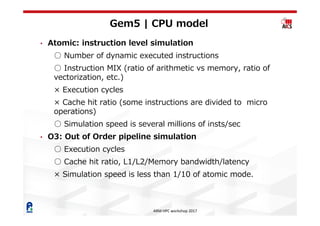

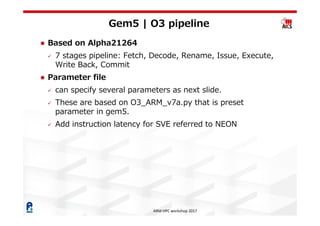

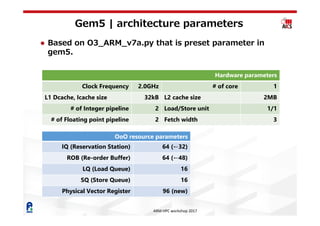

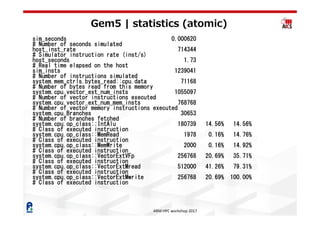

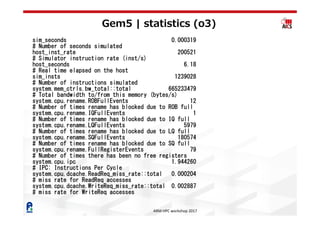

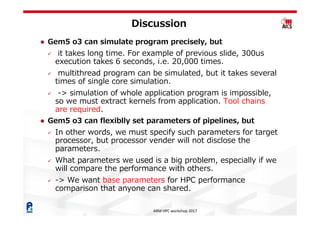

The document discusses the gem5 simulator presented at the ARM HPC Workshop 2017, highlighting its multi-ISA support and various CPU models including atomic and out-of-order simulations. It details the architecture parameters, performance statistics, and the limitations of simulating whole applications due to time constraints. Additionally, it raises concerns about parameter disclosure for fair performance comparisons in HPC contexts.