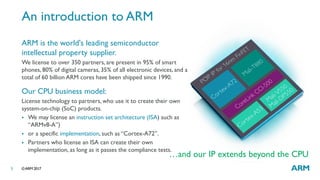

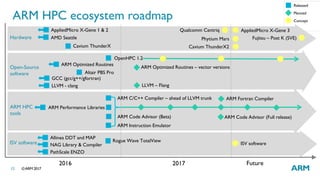

The document discusses ARM's role as a leading semiconductor intellectual property supplier, detailing its licensing model and extensive presence across various electronic devices. It highlights advancements in ARM's support for high-performance computing (HPC), particularly with RDMA support, and outlines a growing ecosystem of open-source software and hardware collaborations. The document also examines lessons learned in software-hardware interactions and optimizations in multithreaded environments.

![©ARM 201723

Testbed

• 2 x Softiron Overdrive 3000 servers with AMD Opteron A1100 / 2GHz

• ConnectX-4 IB/VPI EDR (PCIe g2 x8)

• Ubuntu 16.04

• MOFED 3.3-1.5.0.0

• UCX [0558b41]

• XPMEM [bdfcc52]

• OSHMEM/OPEN-MPI [fed4849]](https://image.slidesharecdn.com/rdmaonarm-170329145435/85/RDMA-on-ARM-23-320.jpg)