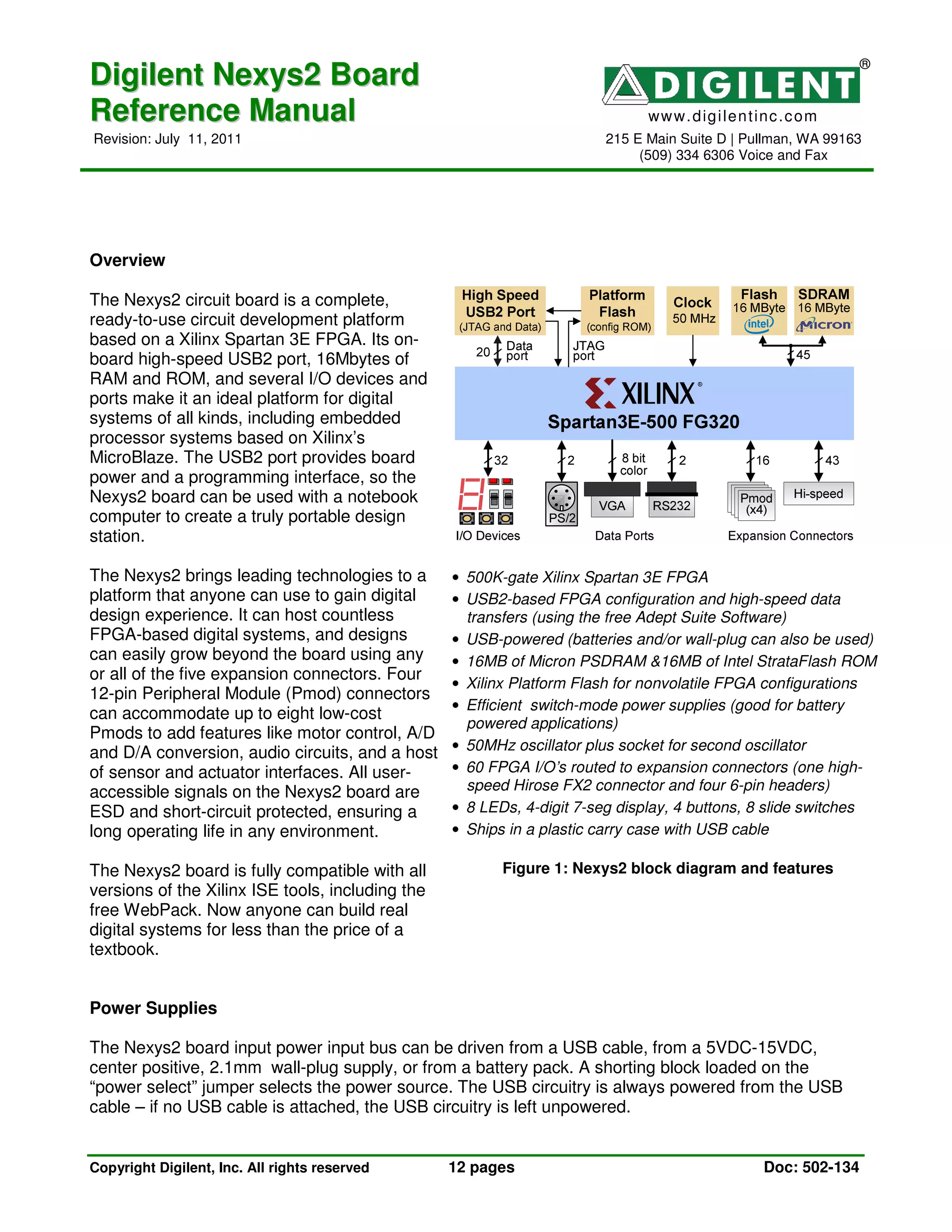

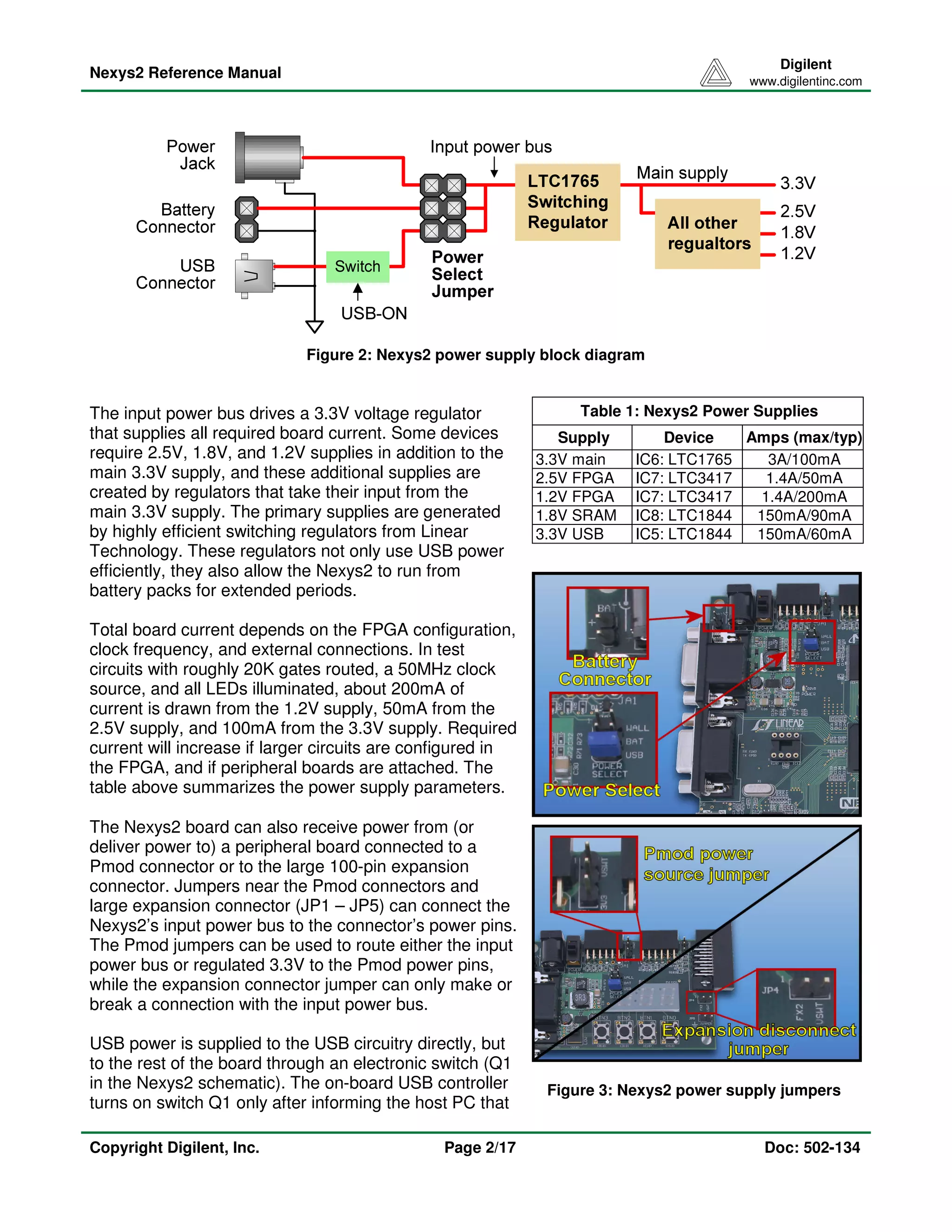

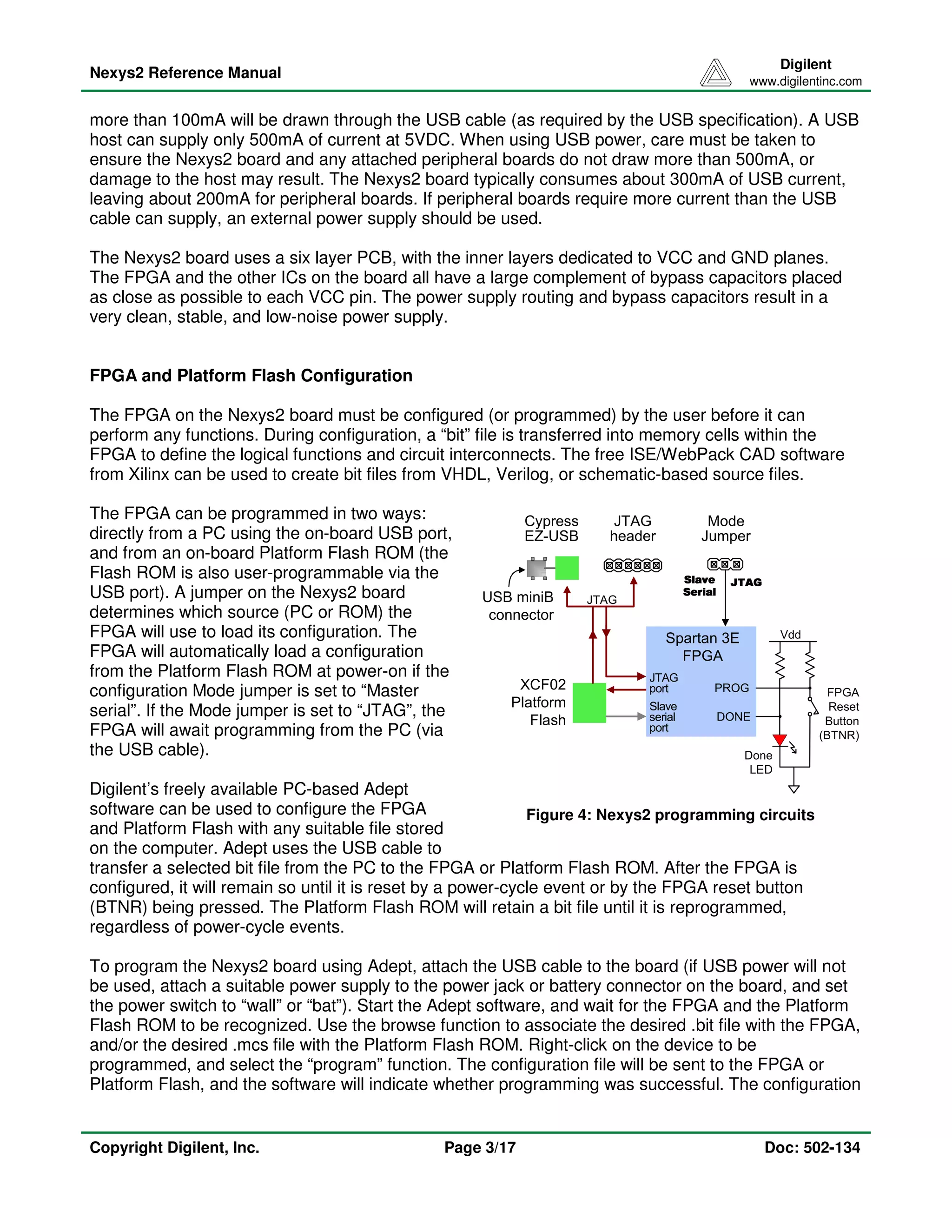

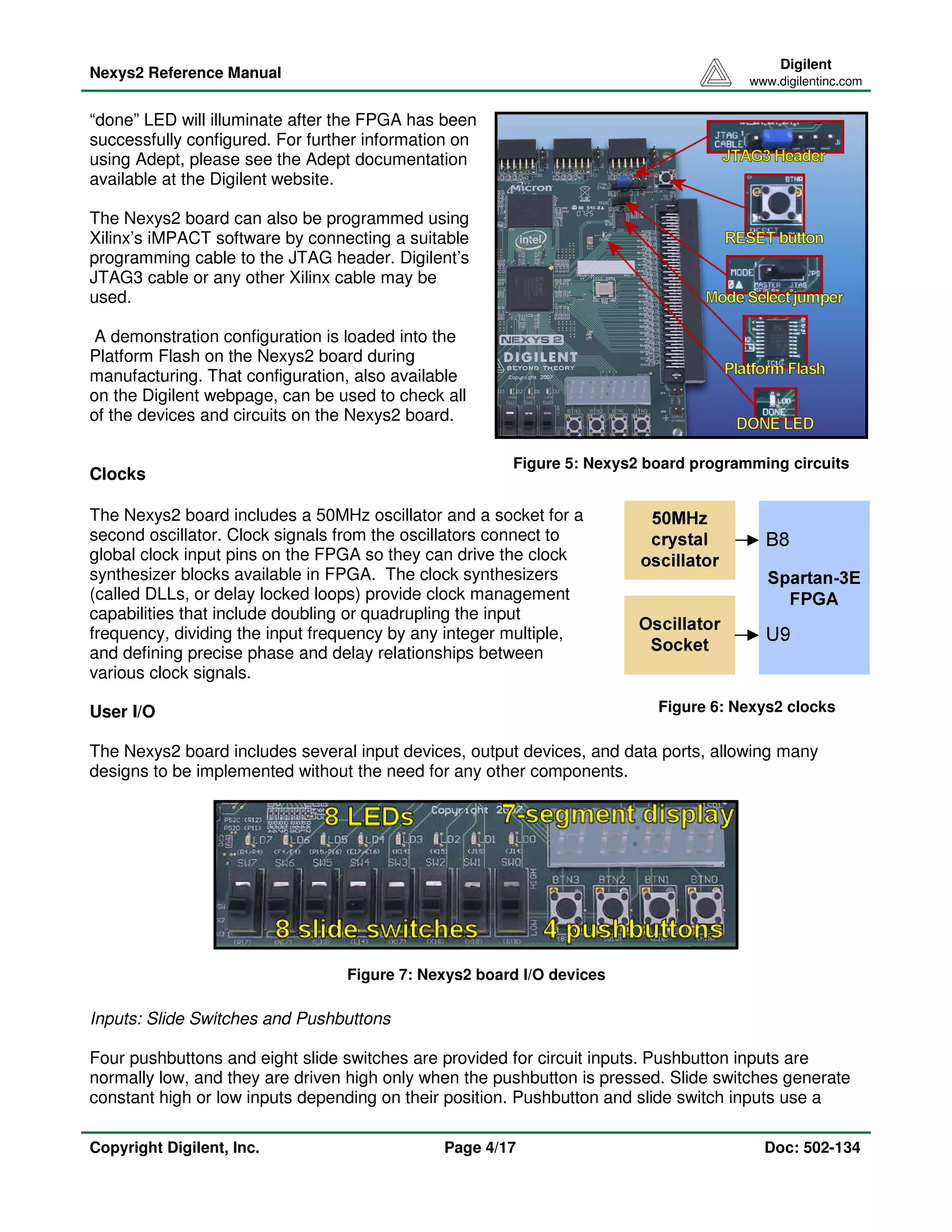

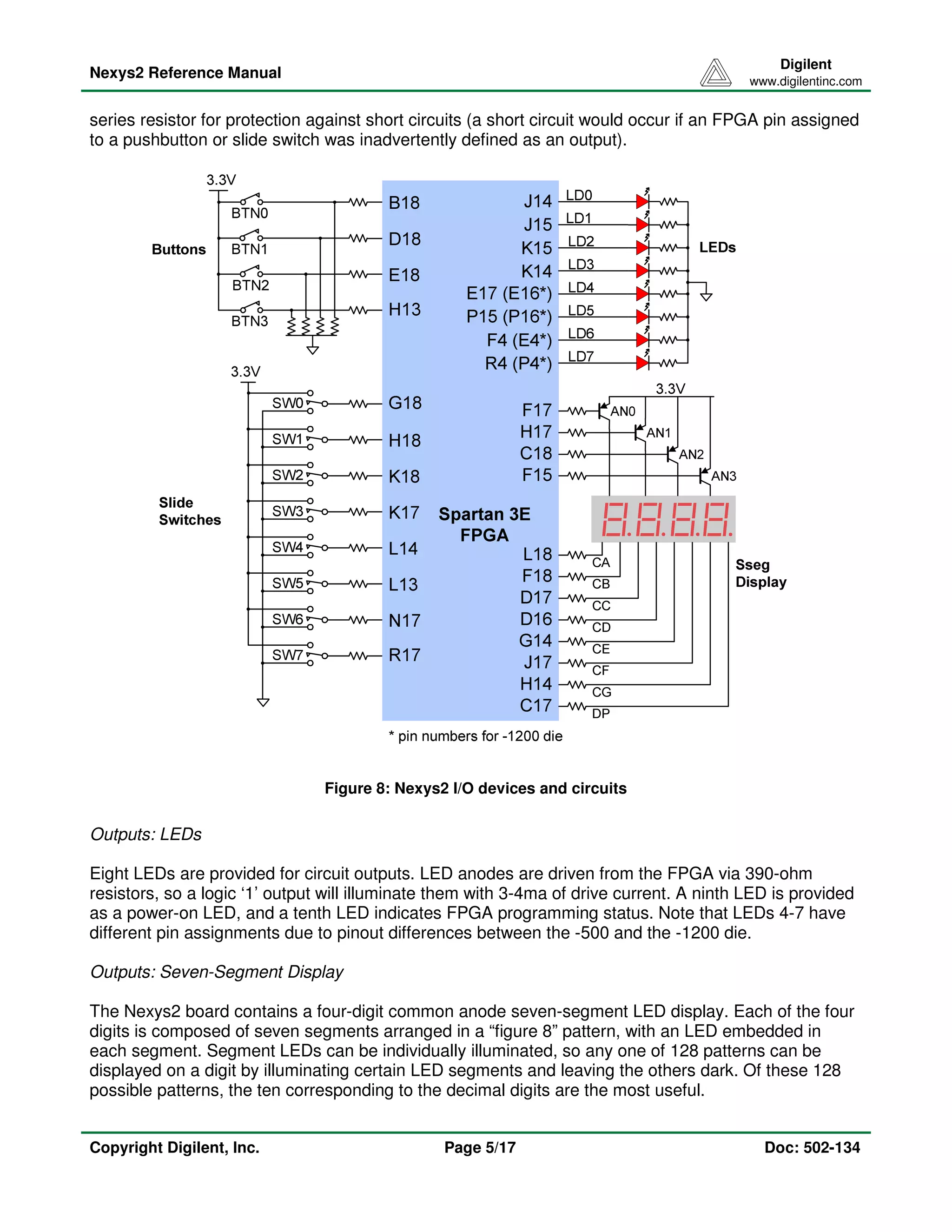

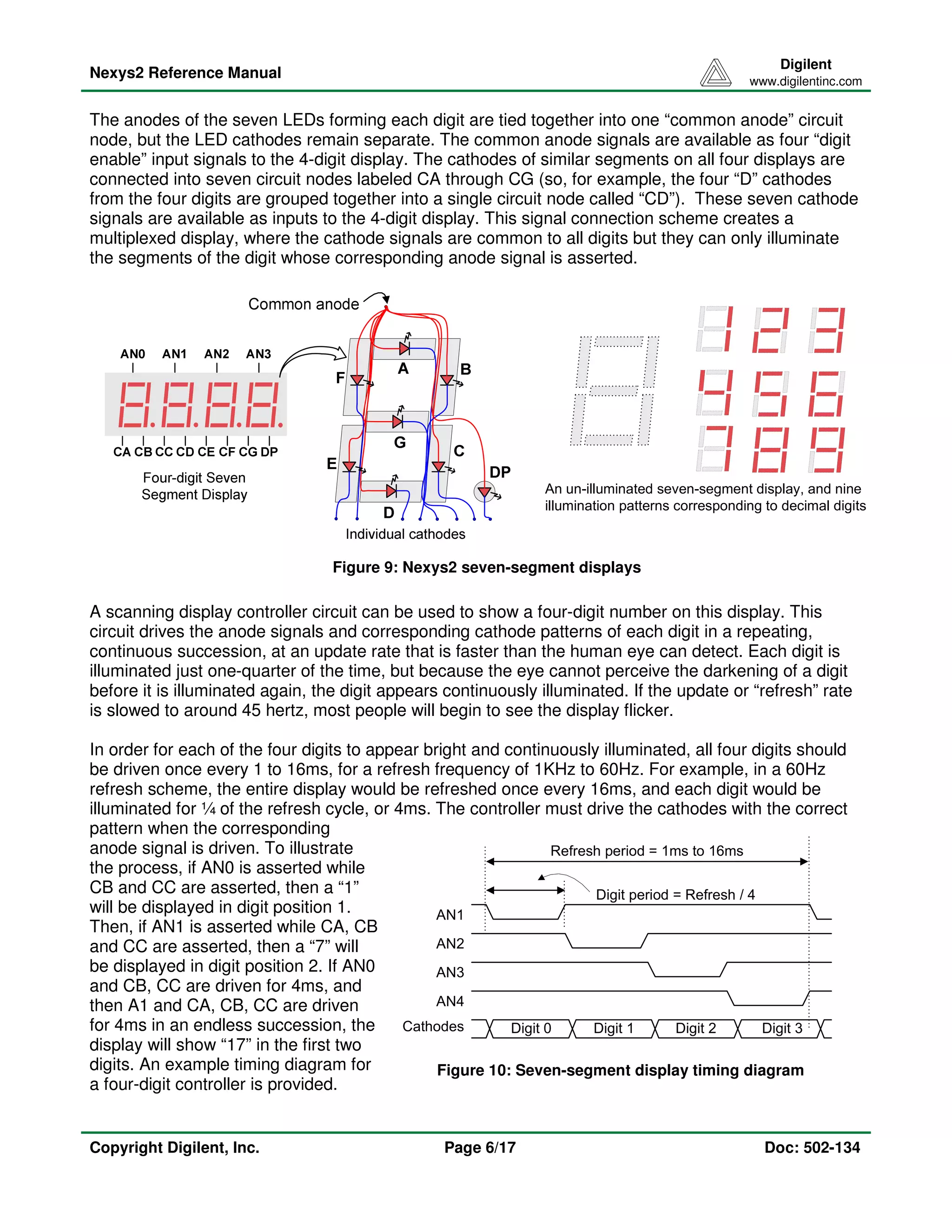

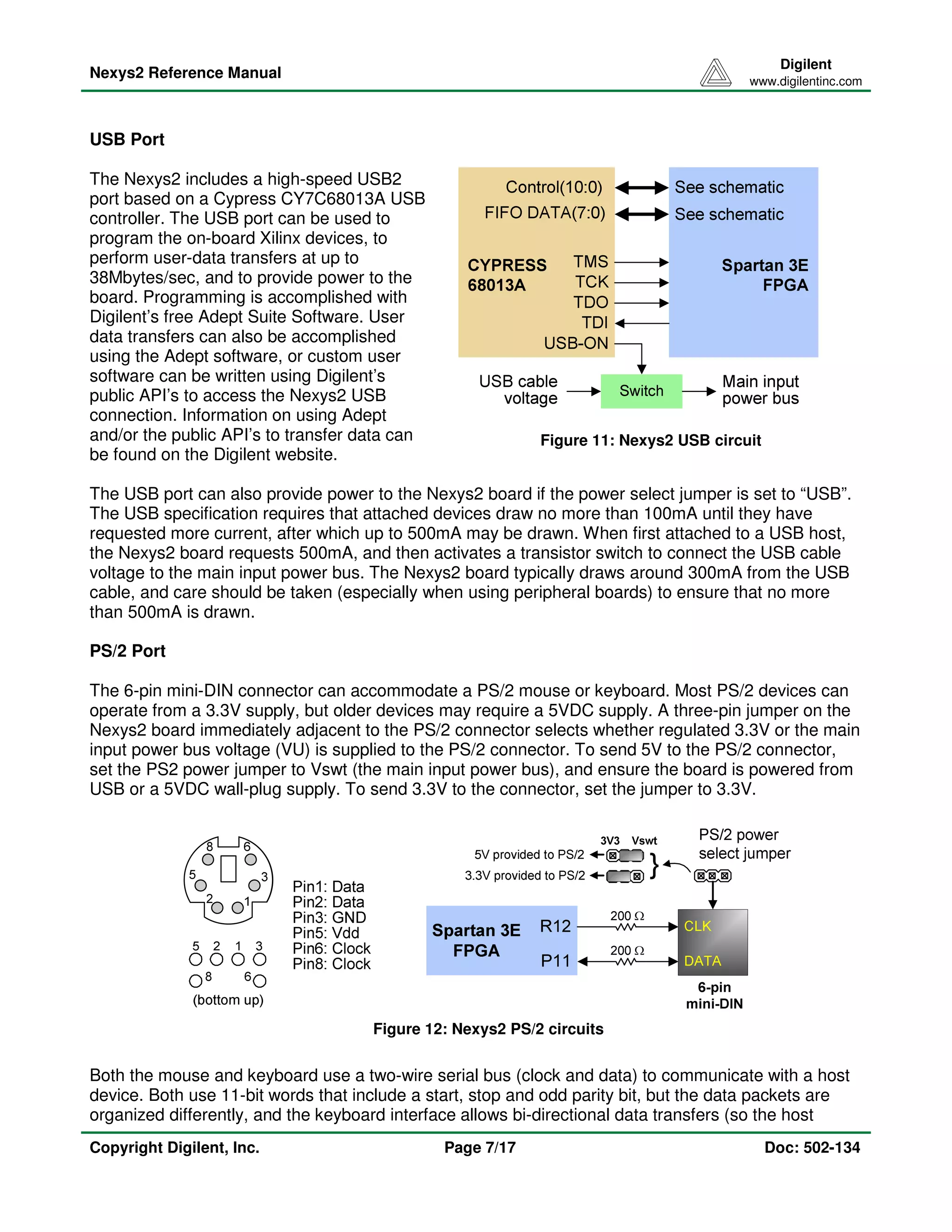

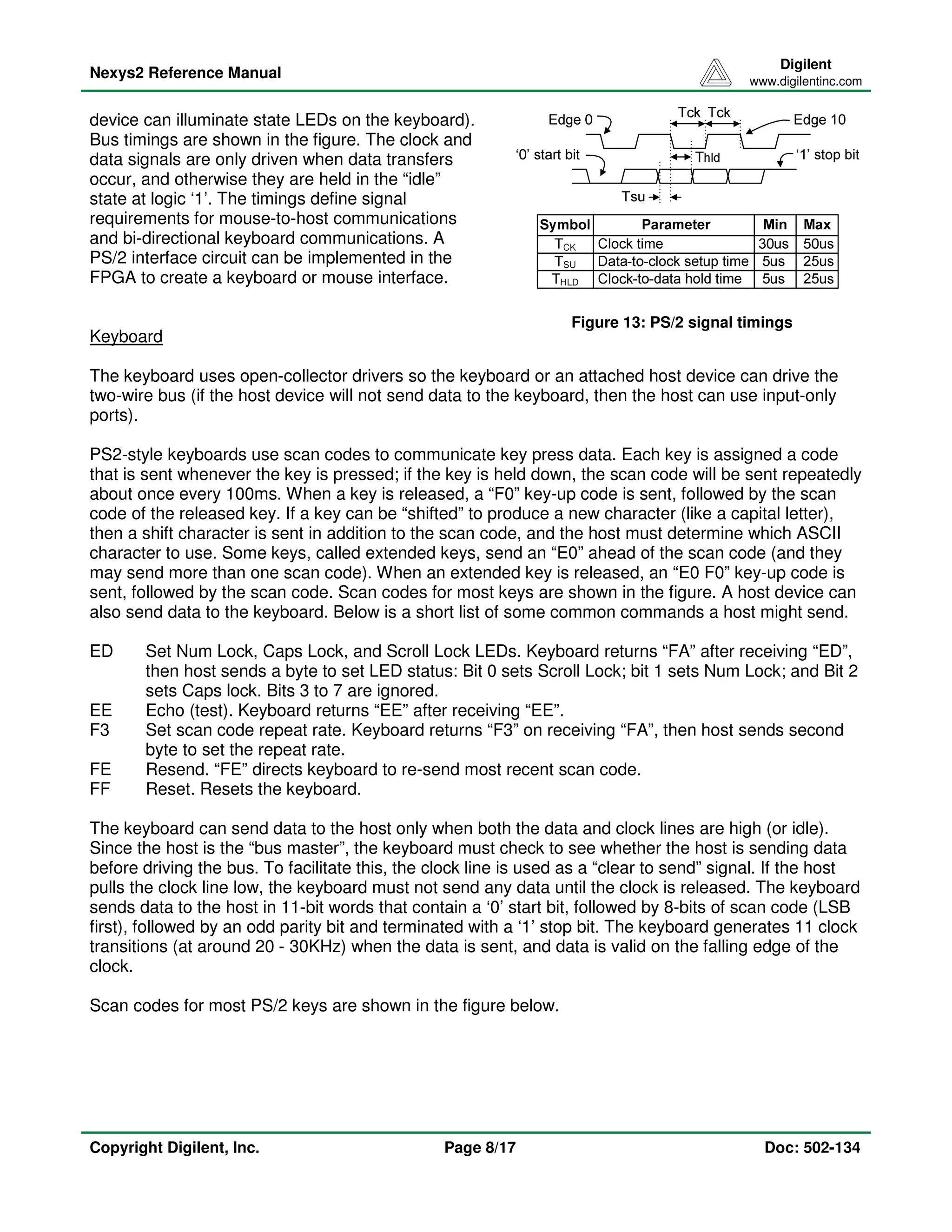

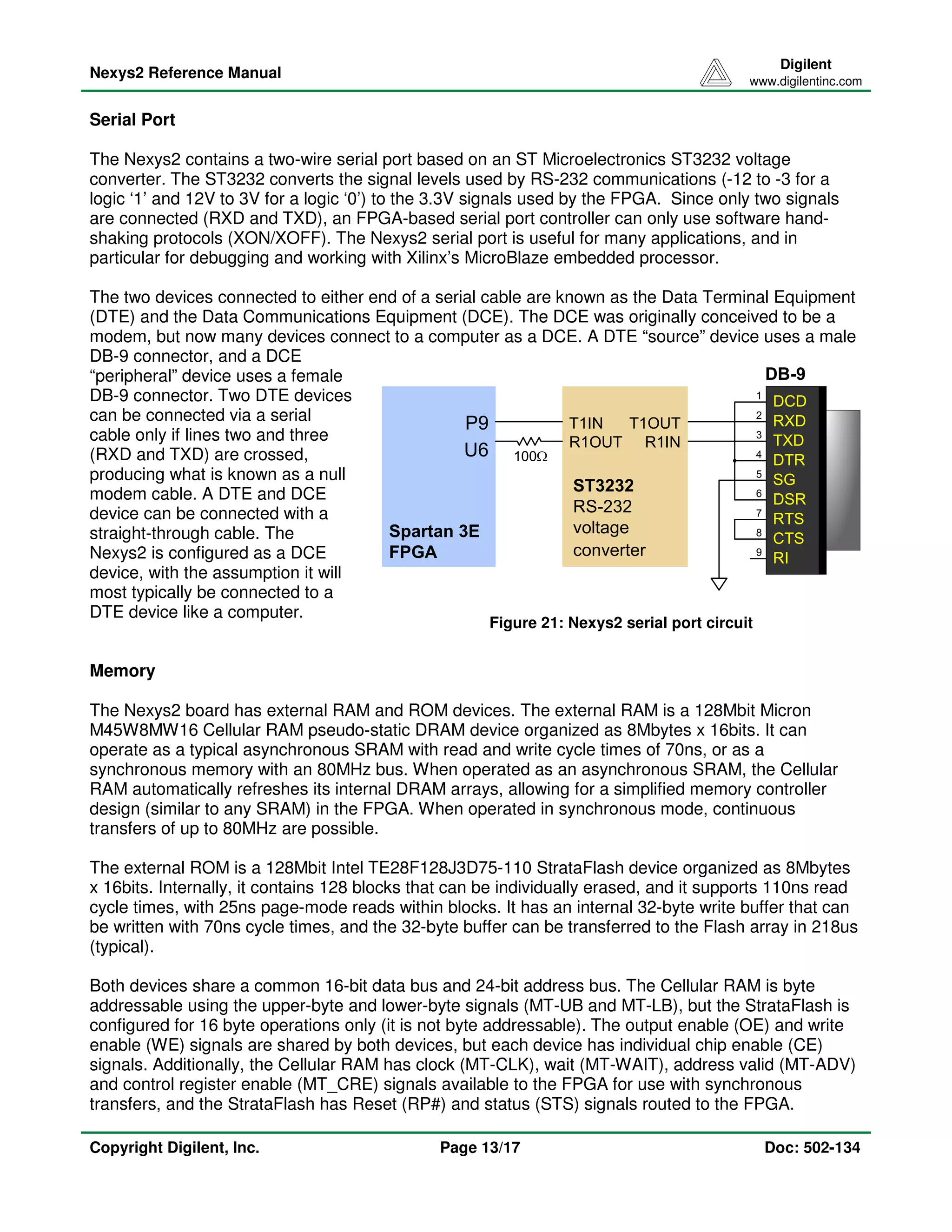

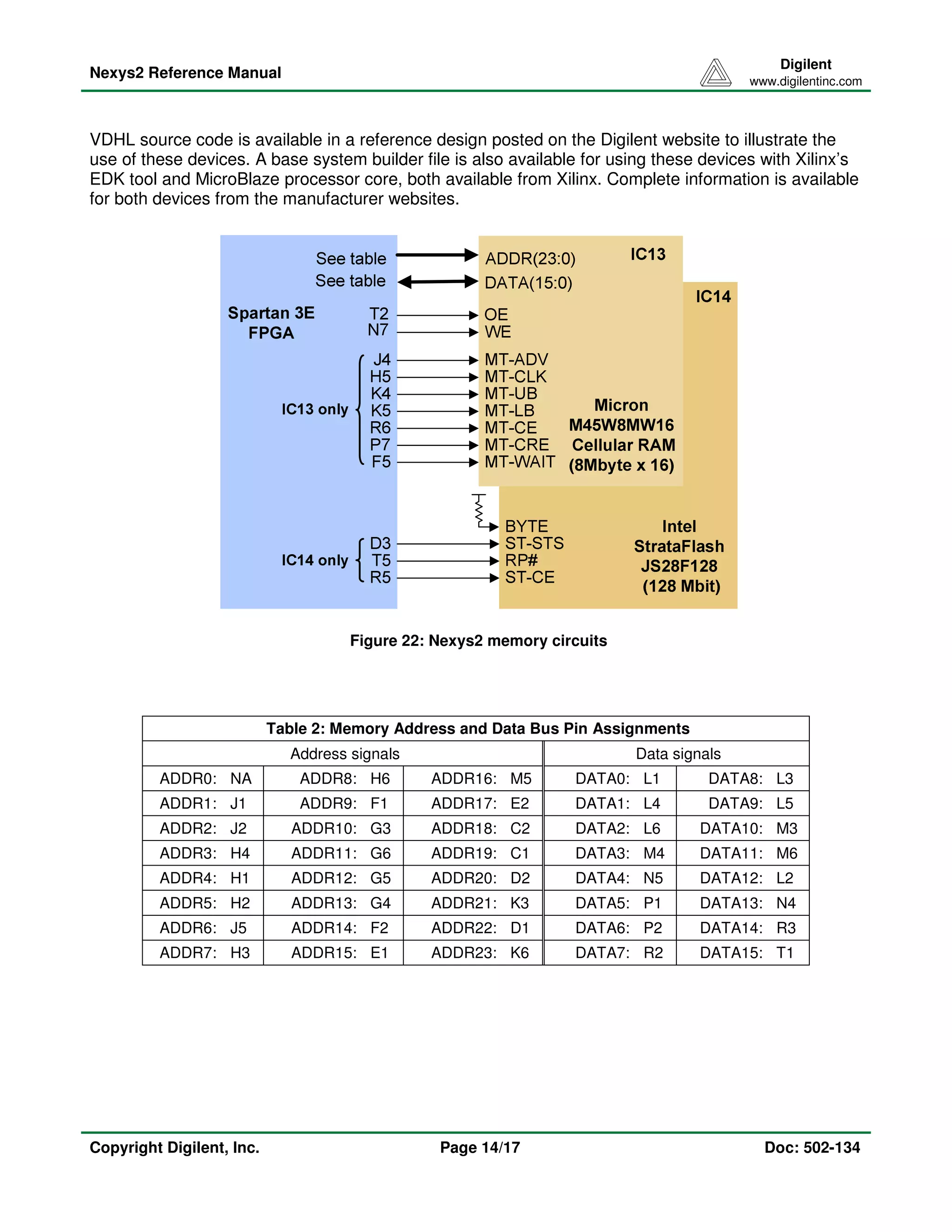

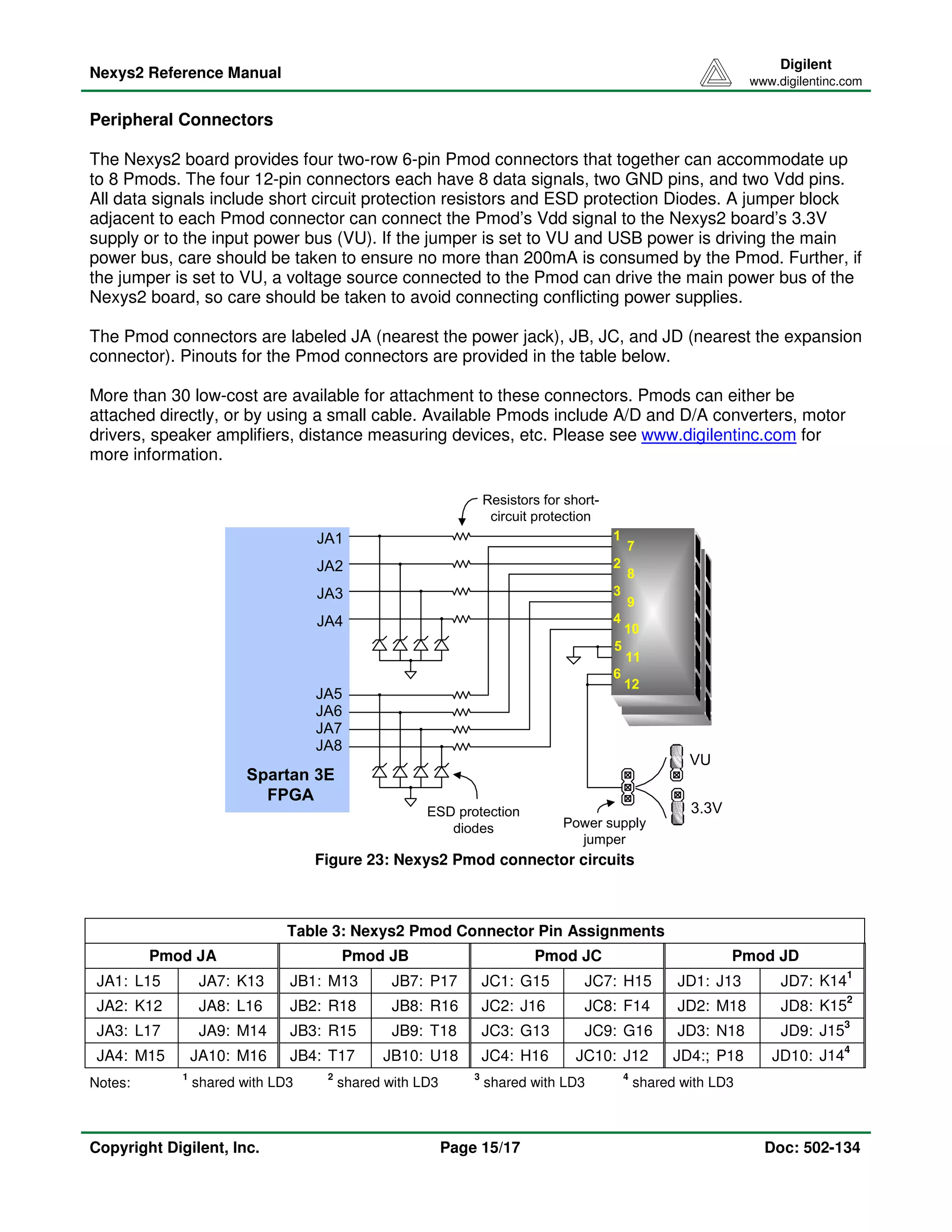

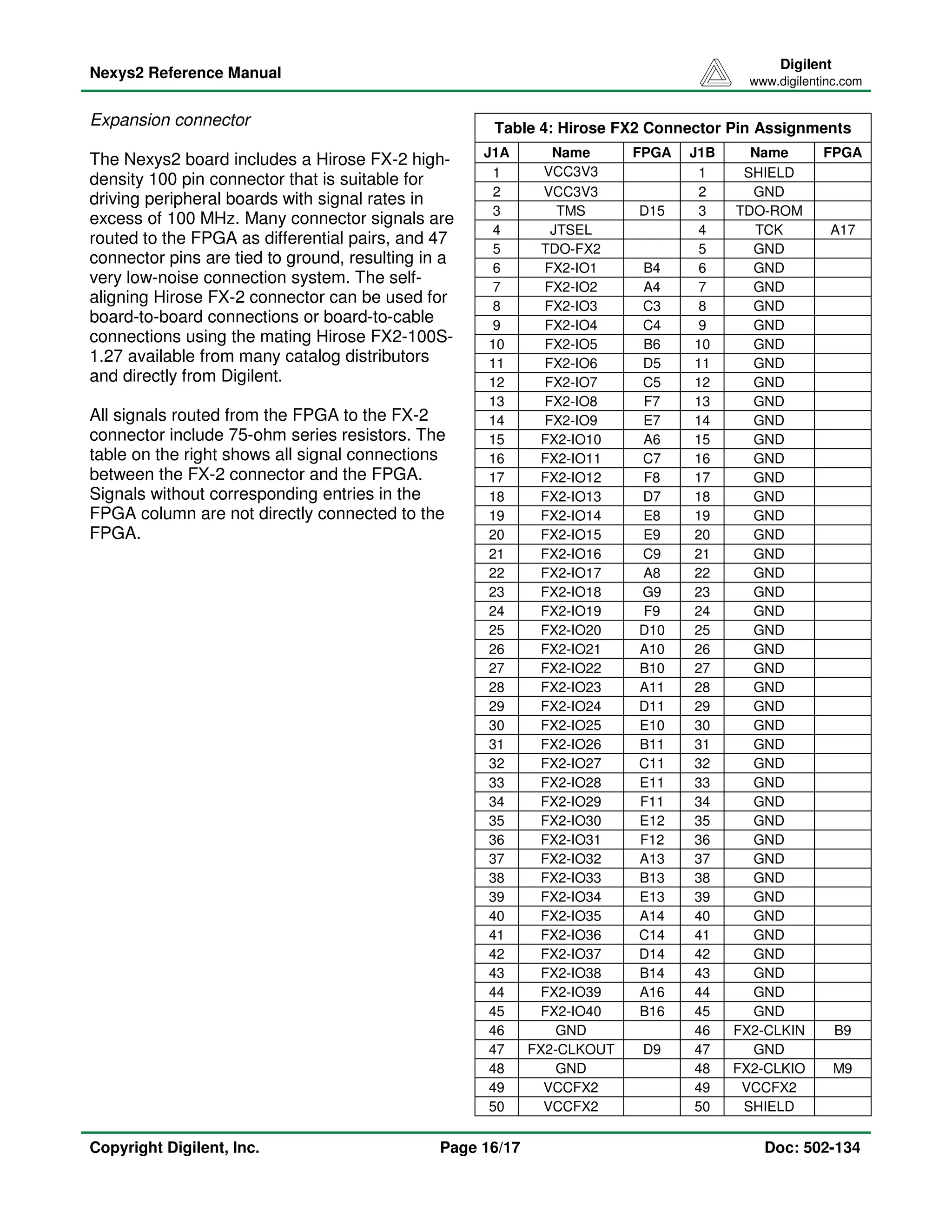

The document provides an overview of the Nexys2 circuit board, which is a complete development platform based on a Xilinx Spartan 3E FPGA. The board includes a USB port for power and programming, 16MB of RAM and ROM, input/output devices, and expansion connectors. It can be programmed via the USB port using free software to load a bitstream into the FPGA or Platform Flash memory. The board also includes power supplies, clocks, and input/output devices to implement digital designs without additional components.