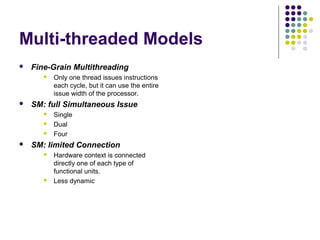

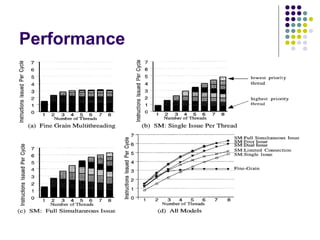

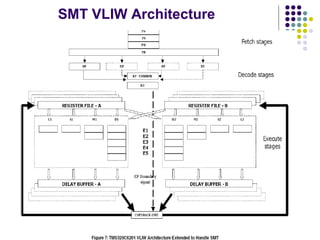

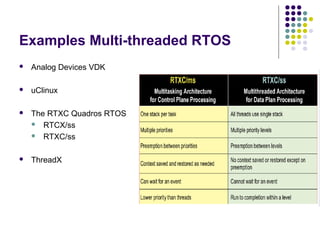

Multi-threaded processor architectures can improve parallelism at both the instruction-level and thread-level. Simultaneous multi-threading (SMT) allows multiple threads to issue and execute instructions simultaneously by dynamically sharing processor resources. SMT reduces underutilization of functional units and improves performance over multiprocessors. Multi-threaded designs are well-suited for digital signal processing applications that can benefit from parallel execution at multiple levels. Examples of multi-threaded real-time operating systems that support parallel DSP applications are discussed.