Here are assembly language programs to perform the operations using indexed addressing mode:

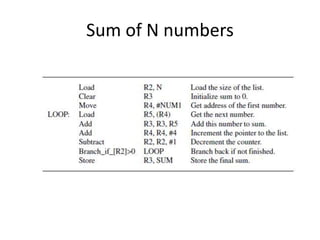

1. Sum N numbers:

Load R1, N

Load R2, 0

Load R3, NUM1

Loop:

Load R4, (R3)

Add R2, R2, R4

Add R3, R3, #4

Subtract R1, R1, #1

Branch_if_R1>0 Loop

Store R2, SUM

2. Add scalar to array:

Load R1, N

Load R2, C

Load R3, A

Loop:

Load R4, (R3)

Add R4, R4, R

![Register Transfer Notation

• Register transfer notation is used to describe

hardware-level data transfers and operations

• Predefined names for processor registers (like

R0,R1) and I/O registers (like DATAIN)

• Arbitrary names for locations in

memory(A,B,LOC,DATA)

• Use […] to denote contents of a location

• Use to denote transfer to a destination

• Example: R2 [LOC]

(transfer from LOC in memory to register R2)](https://image.slidesharecdn.com/lu3-4instructionsandsequencing-221004083655-3f4aa5f4/85/LU3-4-Instructions-and-Sequencing-pptx-3-320.jpg)

![Register Transfer Notation

• RTN can be extended to also show

arithmetic operations involving locations

• Example: R4 [R2] [R3]

(add the contents of registers R2 and R3,

place the sum in register R4)

• Right-hand expression always denotes a value,

left-hand side always names a location](https://image.slidesharecdn.com/lu3-4instructionsandsequencing-221004083655-3f4aa5f4/85/LU3-4-Instructions-and-Sequencing-pptx-4-320.jpg)

![RISC Instruction Sets

• Consider high-level language statement:

C A B

• A, B, and C correspond to memory locations

• RTN specification with these symbolic names:

C [A] [B]

• Steps: fetch contents of locations A and B,

compute sum, and transfer result to location C](https://image.slidesharecdn.com/lu3-4instructionsandsequencing-221004083655-3f4aa5f4/85/LU3-4-Instructions-and-Sequencing-pptx-10-320.jpg)

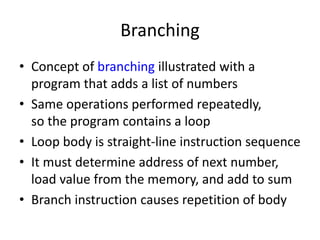

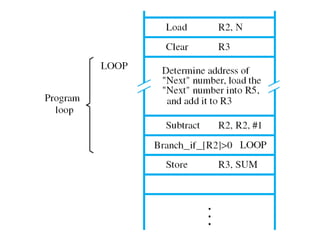

![Branching

• Assume that size of list, n, stored at location N

• Use register R2 as a counter, initialized from N

• Body of loop includes the instruction

Subtract R2, R2, #1

to decrement counter in each loop pass

• Branch_if_[R2]0 goes to branch target LOOP

as long as contents of R2 are greater than zero

• Therefore, this is a conditional branch](https://image.slidesharecdn.com/lu3-4instructionsandsequencing-221004083655-3f4aa5f4/85/LU3-4-Instructions-and-Sequencing-pptx-18-320.jpg)

![Branching

• Branches that test a condition are used in

loops and various other programming tasks

• One way to implement conditional branches

is to compare contents of two registers, e.g.,

Branch_if_[R4][R5] LOOP

• In generic assembly language with mnemonics

the same instruction might actually appear as

BGT R4, R5, LOOP](https://image.slidesharecdn.com/lu3-4instructionsandsequencing-221004083655-3f4aa5f4/85/LU3-4-Instructions-and-Sequencing-pptx-19-320.jpg)

![Try Yourself

• Write a assembly language program to sum N

numbers using indexed addressing mode.

sum = sum + a[i]

• Write a assembly language program to add a

scalar(constant) to an array of N numbers.

a[i] = a[i] + c

• Write a assembly language program to add

two arrays of size N.

c[i] = a[i] + b[i]](https://image.slidesharecdn.com/lu3-4instructionsandsequencing-221004083655-3f4aa5f4/85/LU3-4-Instructions-and-Sequencing-pptx-28-320.jpg)