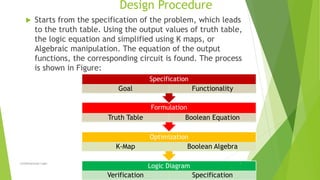

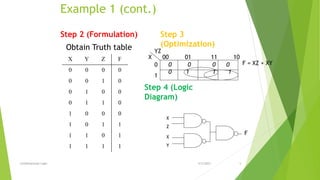

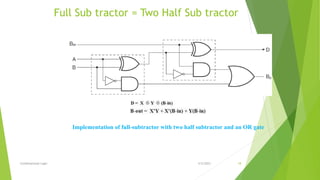

The document discusses combinational logic circuits including adders, subtractors, and their design process. It begins with an overview of combinational vs sequential circuits. The design procedure is then outlined as starting with a specification, formulating a truth table, optimizing with K-maps or algebra, and developing the logic diagram. Examples are provided to design a 3-input/1-output circuit, BCD to excess-3 converter, half and full adders/subtractors. Exercise problems are also listed at the end involving designing incrementers, decrementers, and equality comparators.