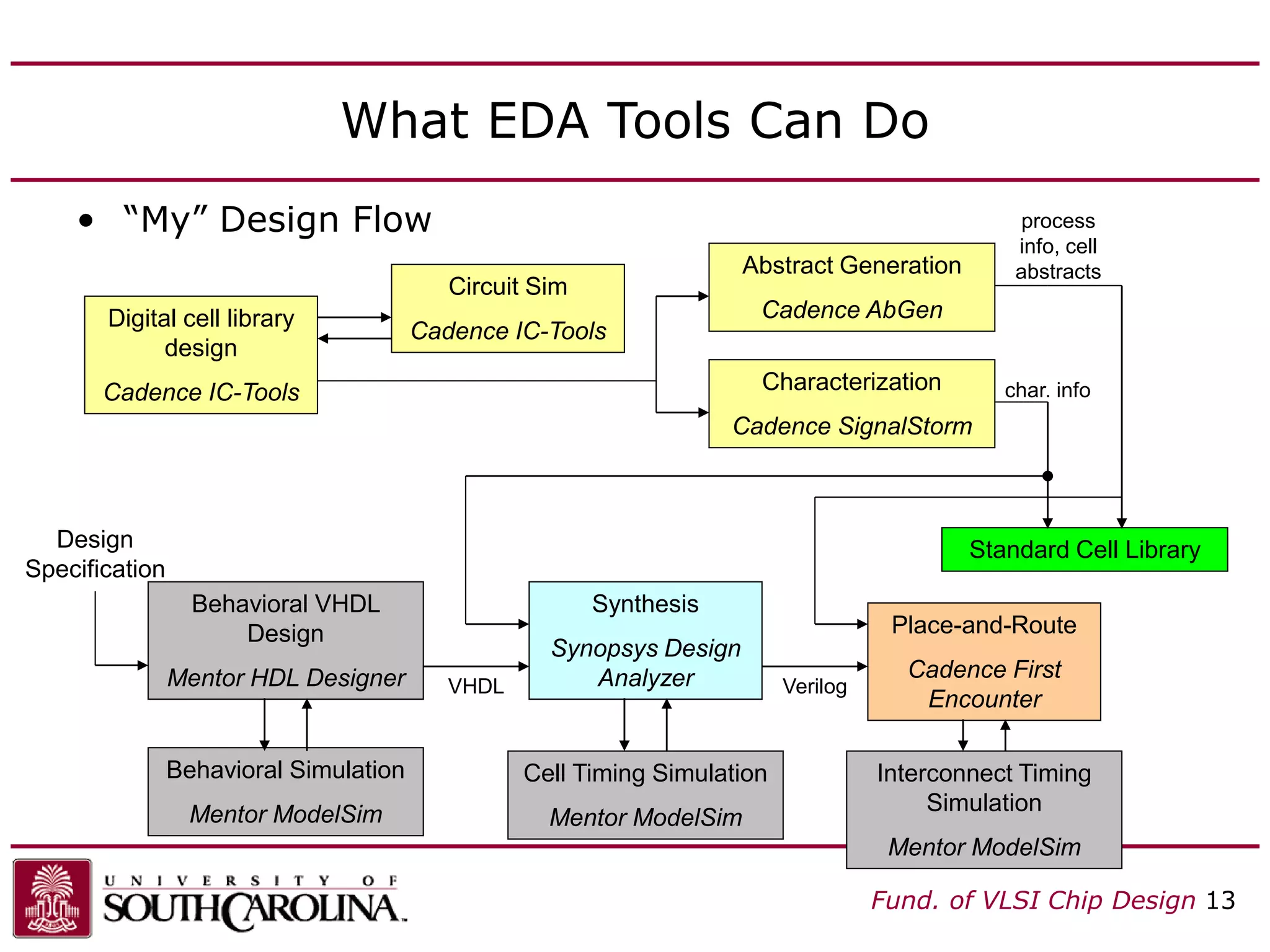

This document provides an overview of the CSCE 613: Fundamentals of VLSI Chip Design course. The course focuses on using electronic design automation (EDA) tools to manage the complexity of designing very large scale integrated (VLSI) circuits. It will cover topics like CMOS circuit design, standard cell library development, VHDL design, logic synthesis, and place-and-route. Students will learn industry-standard EDA tools from Cadence and Synopsys through tutorials and hands-on projects. The goal is for students to gain experience applying EDA methodologies to large-scale digital integrated circuit design.