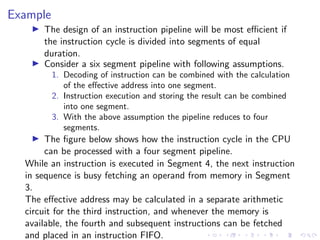

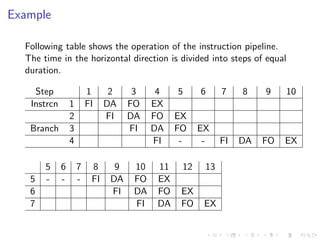

The document explains instruction pipelines in computing, focusing on how they allow overlapping execution of instructions to enhance efficiency. It describes the structure of a four-segment pipeline and the challenges it faces, including structural, data, and control hazards. The text also outlines methods for handling branch instructions, including branch prediction and delayed branches to maintain pipeline flow.