This document presents the design of a low voltage differential CMOS transconductance amplifier operating in the sub-threshold region of 0.5V to 1.5V. A 180nm CMOS technology is used in the design on Cadence. Simulation results show the amplifier achieves a maximum differential output at a bias current of 500nA, with a common mode rejection ratio of 88dB and static power consumption of 241nW under normal input conditions. The layout is presented and verified using DRC and LVS tools in Cadence.

![Int. Journal of Electrical & Electronics Engg. Vol. 2, Spl. Issue 1 (2015) e-ISSN: 1694-2310 | p-ISSN: 1694-2426

NITTTR, Chandigarh EDIT -2015 14

Efficient Design of Differential Trans-

Conductance Amplifier with Sub-Threshold

Biasing Stabilization in Low Power

CMOS Technologies

Jasmeen Kaur1

, Vishal Mehta2

1

School of Electronics and Electrical Engineering, Chitkara University, Rajpura, India

2

Chitkara University Research and Innovation Network, Chitkara University, Rajpura, India

1

jasmeen.kaur@chitkara.edu.in, 2

vishal.mehta@chitkara.edu.in

Abstract: In this paper, a low voltage differential CMOS

trans-conductance amplifier using 180nm on cadence is

presented. This design operates in sub threshold region of

±0.5V-1.5V and biasing stabilization has been checked by

observing relationship between differential voltage and

biasing variations on Nano-scale. Simulation results shows

maximum differential output is obtained when biasing

current reaches 500nA with CMRR 88db and static power

consumption on normal input conditions is 241nW. In this

paper, layout of OTA has been presented after verifying DRC

and LVS by using assura tool of cadence suite.

Keywords- OTA; virtuoso; assura; spectre; bias

I. INTRODUCTION

Due to the advancement in technology and rapid growth of

the microelectronics circuits, the low voltage, low power

and high performance circuits are generally preferred in

VLSI industry [1]-[3]. The transconductance Amplifier is

one of the basic building blocks of any analog application

[4]. The Transconductance Amplifier is widely used in

integrated amplifier, filter and discrete applications. The

transconductance amplifier has differential voltage input

i.e. it takes the difference of the input voltages V1 and V2

which produces the current as output. Hence

transconductance amplifier is basically voltage controlled

current source. The output current will vary according to

the differential input voltage applied while keeping the

accuracy and linearity maintained [5]. In recent years,

various transconductance amplifier circuits has been

purposed having low operating voltage and low power

dissipation .The transconductance amplifier differs from

conventional operational amplifier in output as output of

conventional operational amplifier is voltage whereas in

Transconductance Amplifier, output is current [6-9].

II. BASIC CIRCUIT CONFIGURATION

An ideal differential input Transconductance Amplifier has

infinite input and output impedance [10]. The ideal transfer

characteristics of operational transconductance amplifier is

given as

Iout1 = Gm1 (V1 − V2) (1)

Iout2 = Gm2 (V1 − V2) (2)

where Gm1 and Gm2 is positive transconductance and

negative transconductance respectively. Fig 1 shows the

Transconductance Amplifier where Vin+ is the non-

inverting input voltage and Vin- in inverting input. Fig 2

shows the basic concept used in transconductance

amplifier with differential inputs V1 and V2. Voltage Vb is

used to generate the biasing current Ib in the circuit.

Transistor Qb will act as current source. Differential input

is used in the circuit which provide better common mode

rejection ratio (CMRR), reduce harmonic distortions in the

circuit and produce increased output voltage as compared

to the single ended Amplifier [11-12].

Fig 1- Transconductance Amplifier

Fig 2- Differential Pair input of Trans-conductance Amplifier

III. PROPOSED CIRCUIT

In this paper, a transconductance amplifier with biasing

stabilization is designed. Fig 3 shows the schematic

diagram of this transconductance amplifier designed using

Cadence Virtuoso tool using 180nm technology. In this

schematic, transistor M4, M5, M6 and M7 will act as

differential transistor. Input voltage V1 and V2 is applied](https://image.slidesharecdn.com/id36-150525182630-lva1-app6892/75/Efficient-Design-of-Differential-Trans-Conductance-Amplifier-with-Sub-Threshold-Biasing-Stabilization-in-Low-Power-CMOS-Technologies-1-2048.jpg)

![Int. Journal of Electrical & Electronics Engg. Vol. 2, Spl. Issue 1 (2015) e-ISSN: 1694-2310 | p-ISSN: 1694-2426

NITTTR, Chandigarh EDIT -2015 16

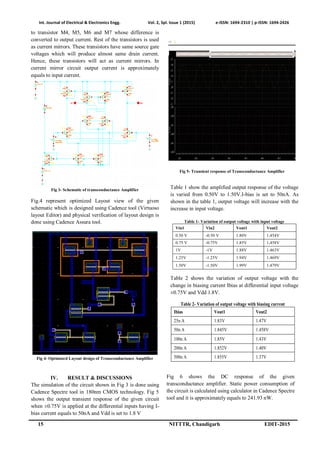

Fig 6- DC characteristics of Transconductance Amplifier

Fig 7 shows the AC response of the circuit which

represents the gain and phase change with frequency.

Common mode rejection ratio (CMRR) of the circuit is

calculated and is equals to 88db.

Table 3 shows the Simulated Characteristics of

Transconductance Amplifier. The simulated result shows

that the power consumption and CMRR with given

characteristics is 241.93nW and 88db respectively.

Table 3- Design specifications

Specifications Simulated

CMOS technology 180nm

Vdd 1.8V

Supply voltage ±0.5V-±1.5V

Bias Current 50n A

CMRR 88db

Static Power Consumption 241.93nW

Fig 7- AC characteristics of Transconductance Amplifier

V. CONCLUSION

In this paper we represent differential trans-conductance

amplifier for low power applications. This amplifier can be

used for low voltage transducers, filter designs and ADC

circuits. Low power consumption also increases its

significance in delta sigma modulator circuits where gain

stabilization is required at different varying conditions.

REFERENCES

[1] Chandrakasan, Anantha P., Samuel Sheng, and Robert W. Brodersen.

"Low-power CMOS digital design." IEICE Transactions on Electronics

75.4 (1992): 371-382.

[2] Raikos, George, and Spyridon Vlassis. "0.8 V bulk-driven operational

amplifier." Analog integrated circuits and signal processing 63.3 (2010):

425-432.

[3] SILVEIRA, F., FLANDRE, D. Low power analog CMOS for cardiac

pacemakers. Design and Optimization in Bulk and SOI Technologies.

Kluwer Academic Publishers, 2004

[4] Nguyen, Trung-Kien, and Sang-Gug Lee. "Low-voltage, low-power

CMOS operation transconductance amplifier with rail-to-rail differential

input range." Circuits and Systems, 2006. ISCAS 2006. Proceedings.

2006 IEEE International Symposium on. IEEE, 2006.

[5] T.Y. Lo and C.C. Hung, “A 1 GHz OTA-based low-pass filter with a

high speed automation tuning scheme,” IEEE Asia solid-stage conference,

pp. 408-411, 2007.

[6] Yavari, Mohammad, and Omid Shoaei. "Low-voltage low-power fast-

settling CMOS operational transconductance amplifiers for switched-

capacitor applications." IEE Proceedings-Circuits, Devices and Systems

151.6 (2004): 573-578.

[7] Zao, Liu, et al. "The design and optimization of gain-boosted OTA for

high speed and high accuracy sample and hold amplifier." ASIC, 2007.

ASICON'07. 7th International Conference on. IEEE, 2007.

[8] P. Corbishley and E.R. Villegas, “A Low Power Low Voltage

Rectifier Circuit,” MWSCAS '06, vol. 2, pp. 512–515, 2006.

[9] de Carvalho Ferreira, L. H., and T. C. Pimenta. "An ultra low-voltage

ultra low power rail-to-rail CMOS OTA Miller." Circuits and Systems,

2004. Proceedings. The 2004 IEEE Asia-Pacific Conference on. Vol. 2.

IEEE, 2004.

[10] Chanapromma, Chaiyan, and Kanchana Daoden. "A CMOS fully

differential operational transconductance amplifier operating in sub-

threshold region and its application." Signal Processing Systems (ICSPS),

2010 2nd International Conference on. Vol. 2. IEEE, 2010.

[11] Mohieldin, Ahmed Nader, Edgar Sánchez-Sinencio, and José Silva-

Martínez. "Nonlinear effects in pseudo differential OTAs with CMFB."

Circuits and Systems II: Analog and Digital Signal Processing, IEEE

Transactions on 50.10 (2003): 762-770.

[12] Mohieldin, Ahmed N., Edgar Sánchez-Sinencio, and José Silva-

Martínez. "A fully balanced pseudo-differential OTA with common-mode

feedforward and inherent common-mode feedback detector." Solid-State

Circuits, IEEE Journal of 38.4 (2003): 663-668.](https://image.slidesharecdn.com/id36-150525182630-lva1-app6892/85/Efficient-Design-of-Differential-Trans-Conductance-Amplifier-with-Sub-Threshold-Biasing-Stabilization-in-Low-Power-CMOS-Technologies-3-320.jpg)