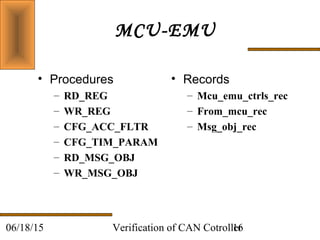

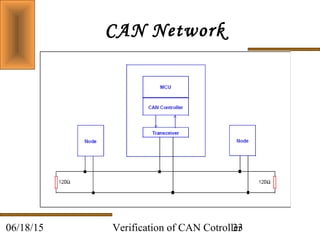

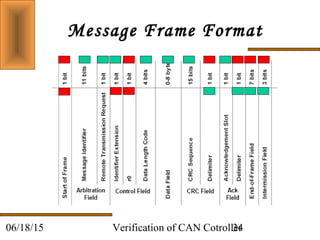

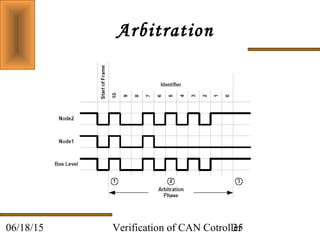

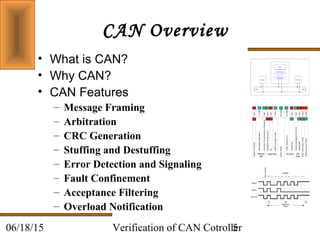

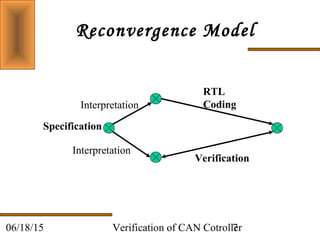

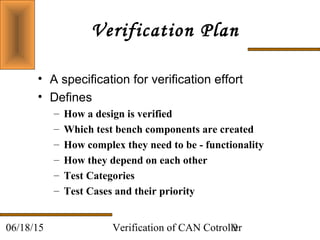

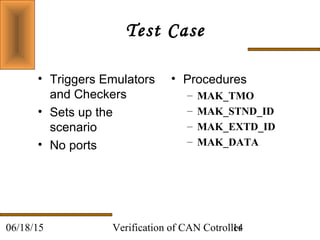

The document describes the functional verification of a CAN controller design. It discusses verifying that the design meets the CAN specification through the creation of a flexible verification environment using a combination of black box, white box and grey box verification approaches. The environment contains test cases, emulators to simulate the microcontroller and CAN nodes, and a response checker. A variety of test categories and procedures are used to verify behaviors like message framing, arbitration, error detection and signaling.

![Verification of CAN Cotroller1206/18/15

Verification Environment

CAN Bus

Functional

Model

(BUS-EMU)

CAN Node

Emulator 1

(CAN-EMU)

DUV Tx

DUV Rx

CAN Tx

BFM_MD

CS#

INT#

WRL#

CLK

WRH#

Addr[7:0]

Data[15:0]

CAN

Controller

Device (DUV)

Micro

controller

Emulator

(MCU-EMU)

RD#

RST#

Test Cases

Response

Checker

CAN Rx](https://image.slidesharecdn.com/4efbd6c4-ad87-4510-9255-c9f3bc324e74-150618175150-lva1-app6891/85/Final_Viva_Voce_Presentation_latest-12-320.jpg)

![Verification of CAN Cotroller1506/18/15

MCU-EMU Interface

CS#

INT#

WRL#

CLK

WRH#

Addr[7:0]

Data[15:0]

CAN

Controller

Device (DUV)

Micro

controller

Emulator

(MCU-EMU)

RD#

RST#

• Configures the

DUV

• Controls the DUV

• Runs at a

programmable

frequency

• Checks RMOs

(Receive

Message Objects)](https://image.slidesharecdn.com/4efbd6c4-ad87-4510-9255-c9f3bc324e74-150618175150-lva1-app6891/85/Final_Viva_Voce_Presentation_latest-15-320.jpg)