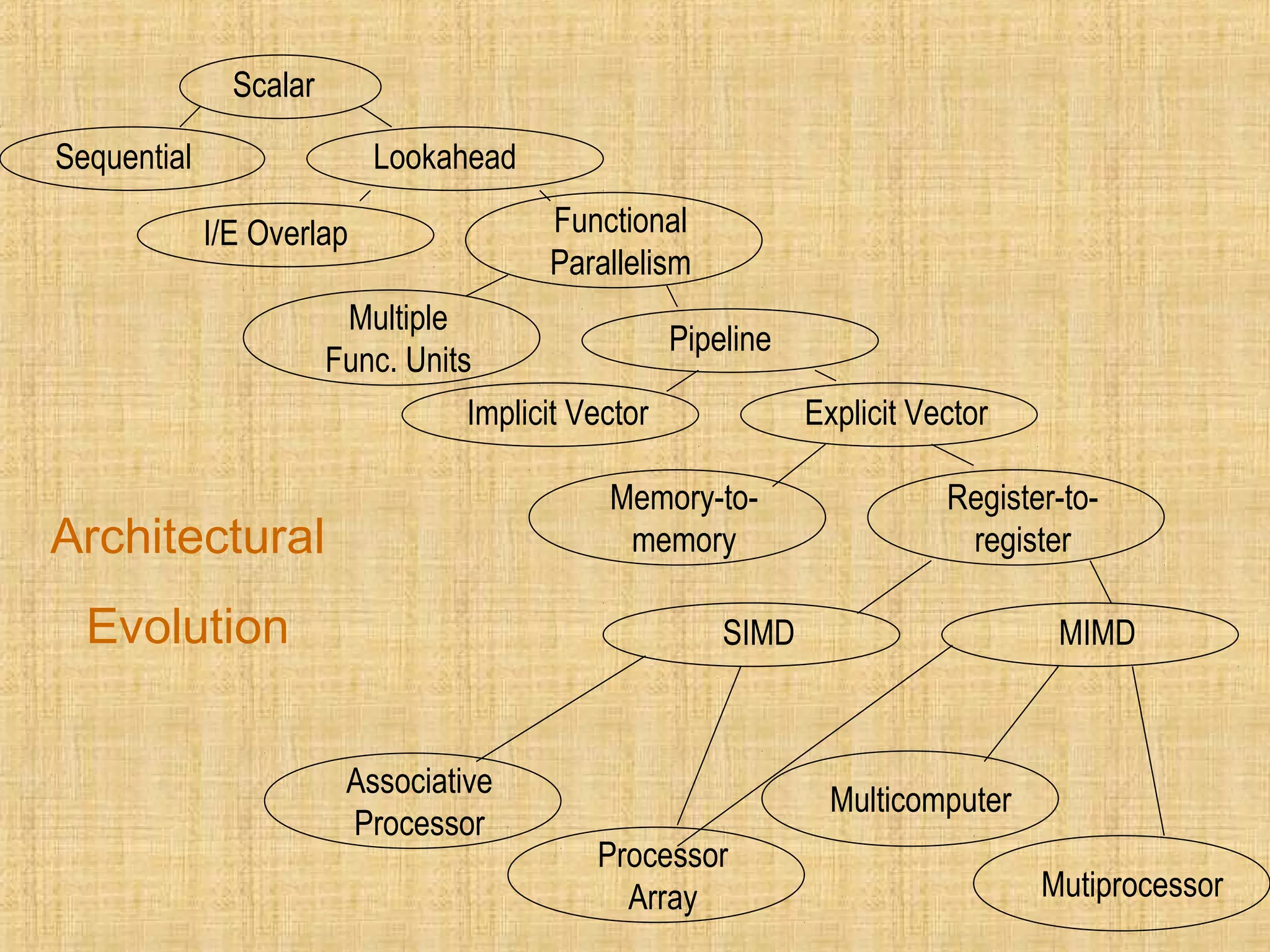

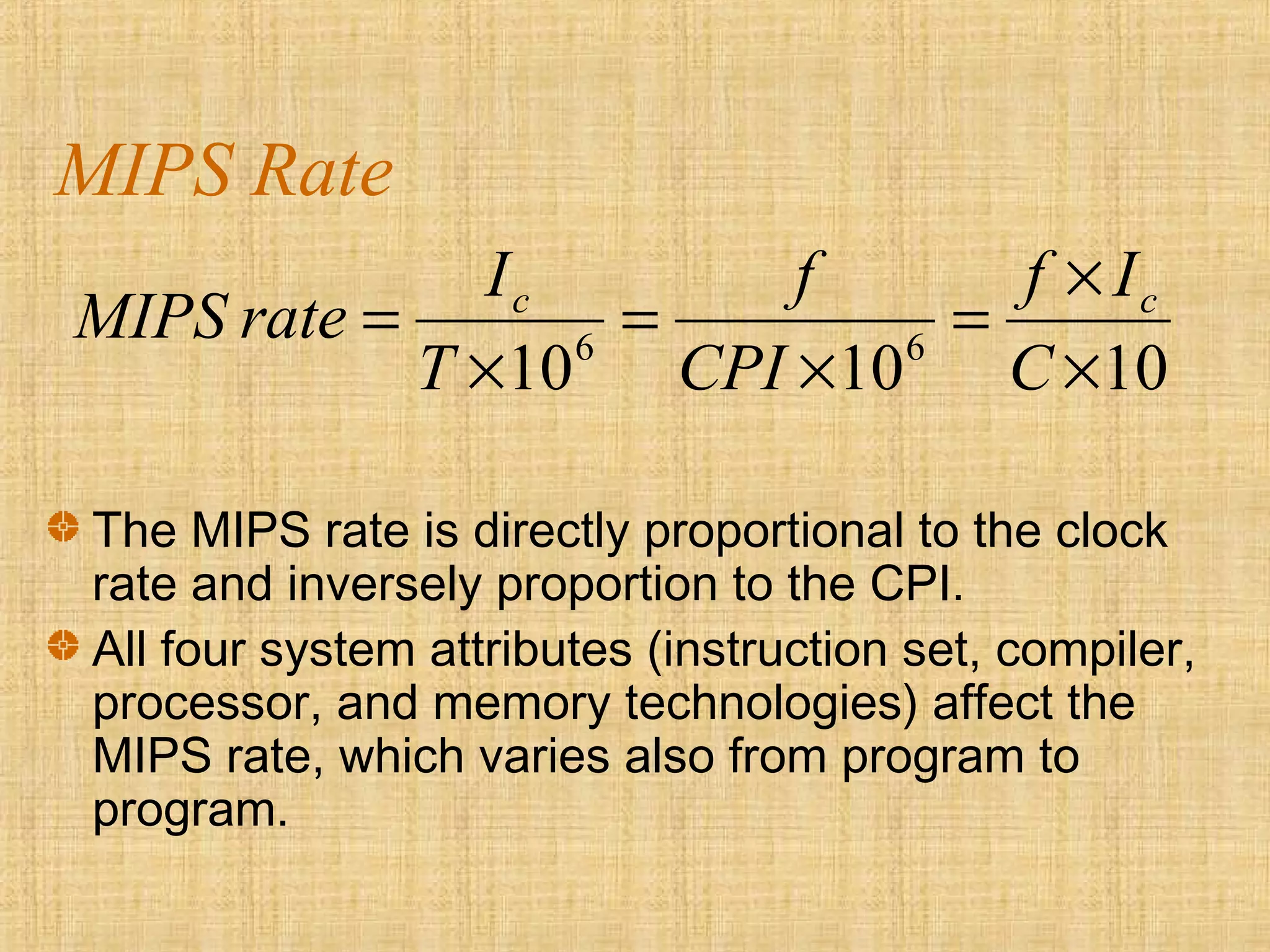

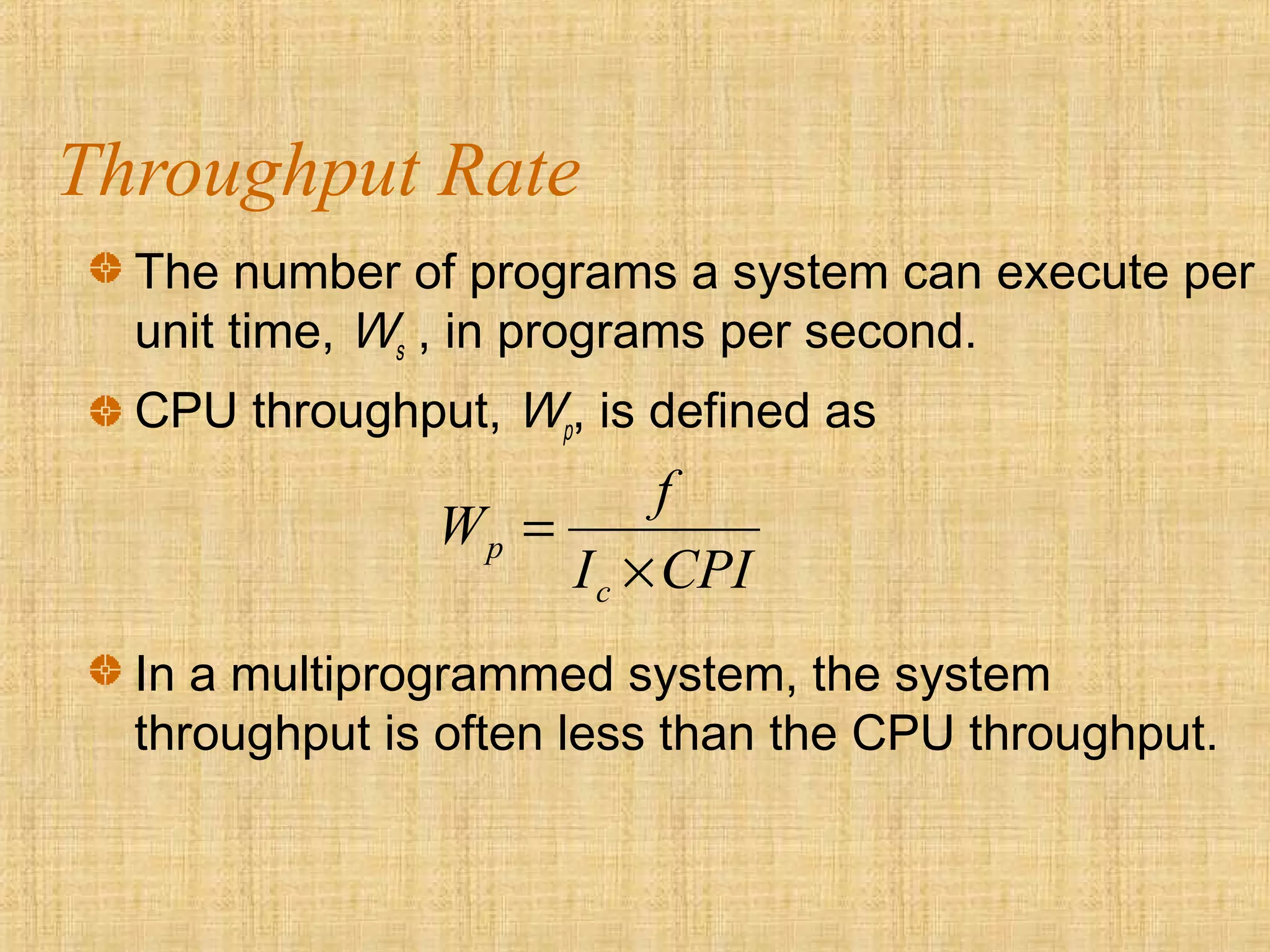

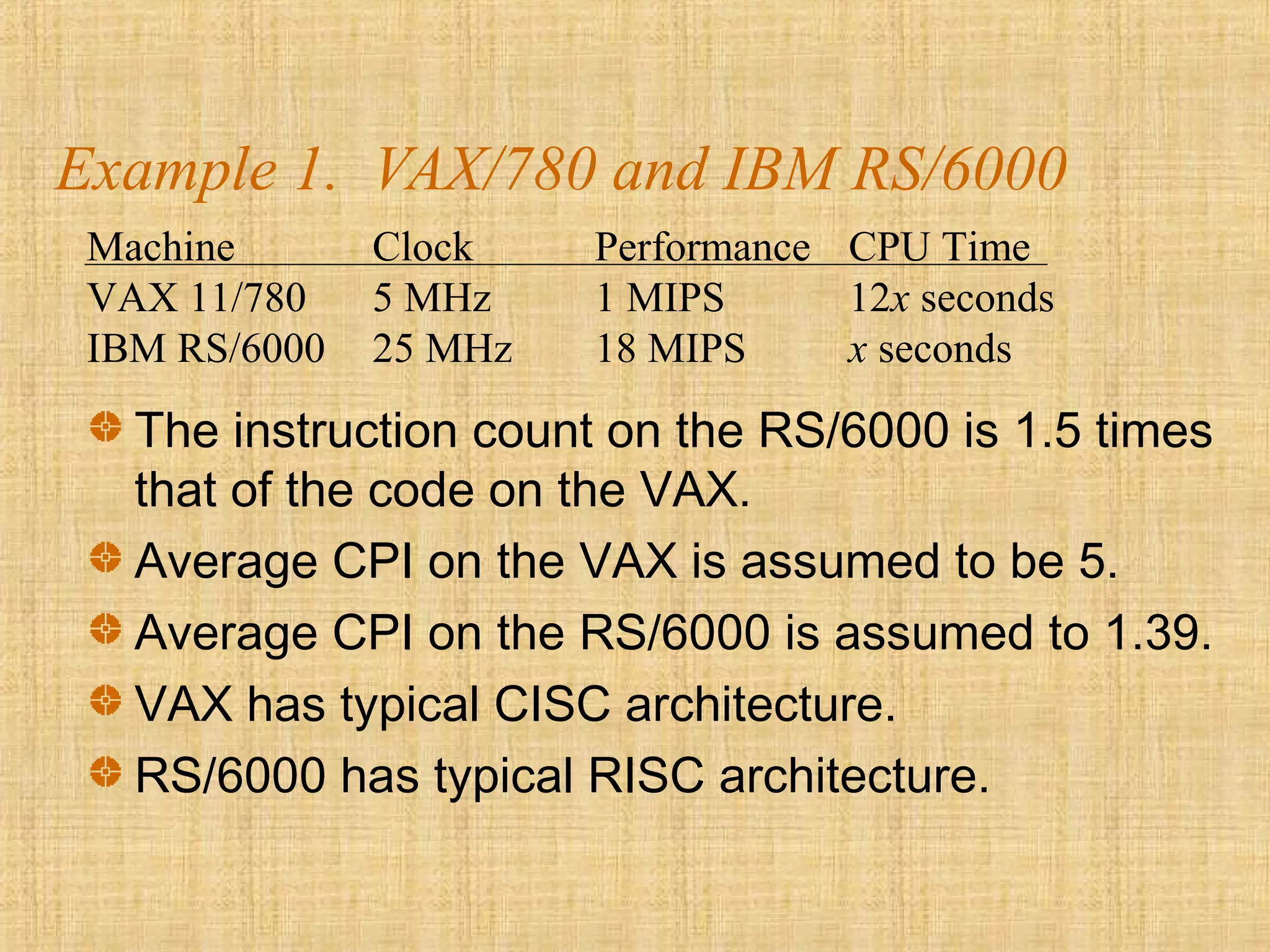

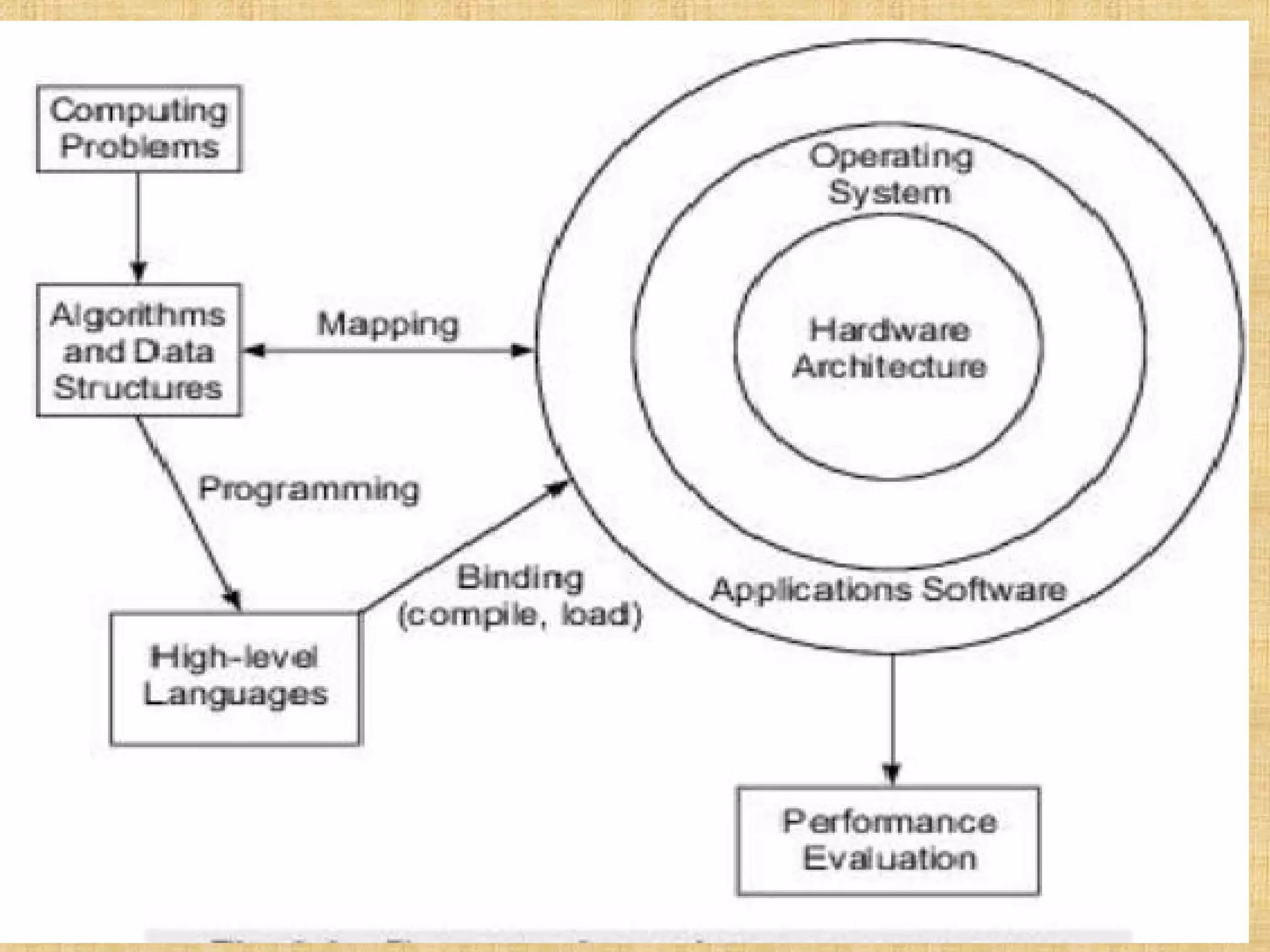

The document discusses advanced computer architecture, focusing on the integration of hardware, software, and programming in modern computers, which are driven by complex problem-solving needs in various fields. It highlights the evolution of computer architecture from sequential to parallel processing and the influence of performance factors such as instruction count, cycles per instruction, and clock rates on overall efficiency. Additionally, it addresses the importance of compilers and software tools for effective parallel programming and the challenges faced in optimizing system performance.

![Computing Problems

A modern computer is an integrated system

consisting of machine hardware, an instruction set,

system software, application programs, and user

interfaces.

The use of a computer is driven by real-life problems

demanding cost effective solutions.

For numerical problems in science and technology,

the solutions demand complex mathematical

formulations and intensive integer or floating-point

computations.

For artificial intelligence [Al] problems, the solutions

demand logic inferences and symbolic

manipulations.](https://image.slidesharecdn.com/evaluationofmordencomputersystemattributes-190323080443/75/Evaluation-of-morden-computer-system-attributes-in-ACA-5-2048.jpg)