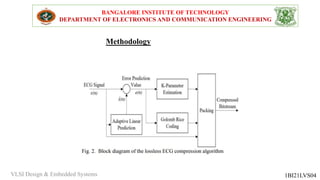

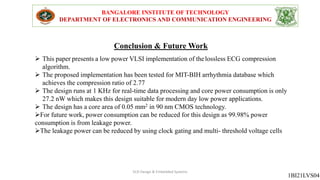

This technical seminar discusses the VLSI implementation of an ECG data compression algorithm for low power devices. The presented algorithm uses adaptive linear prediction and Golomb-Rice coding for lossless ECG compression. A hardware architecture was designed that achieves a compression rate of 2.77x on ECG data from the MITBIH database. The VLSI implementation contains 3.1K gates, consumes 27.2nW of power at 1KHz, and has a core area of 0.05mm2 in a 90nm CMOS process. This makes it suitable for use in low power health monitoring devices.

![Lossless Data Compression Technique:

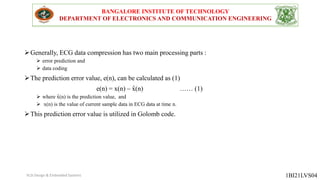

Entropy coding is the part of coding technique in data compression, in which frequently occurring patterns or

values are presented with few binary bits and rarely occurring ones are presented with many binary bits.

Content-Adaptive Golomb-Rice code:

Golomb coding is a data compression scheme based upon entropy encoding and is optimal for alphabets with

a geometric distribution. The Golomb-Rice code comprises two parts:

Quotient and

Remainder,

which are represented by :

where k represents the number of bits for the remainder, and M[n] is a positive integer. M[n] is achieved

by transformation of a prediction error, which may be a negative value, into a positive number. This

function can be described by:

where e is the prediction error value.

BANGALORE INSTITUTE OF TECHNOLOGY

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

1BI21LVS04

VLSI Design & Embedded Systems](https://image.slidesharecdn.com/mohans04-230119141355-a2c83b1f/85/ECG-compression-in-vlsi-12-320.jpg)

![BANGALORE INSTITUTE OF TECHNOLOGY

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

1BI21LVS04

C.-I. Ieong, M. Li, M.-K. Law, P.-I. Mak, M. I. Vai, and R. P. Martins, “A 0.45 V 147–375 nW

ECG Compression Processor With Wavelet Shrinkage and Adaptive Temporal Decimation

Architectures,” IEEE TVLSI Syst., vol. 25, no. 4, Apr. 2017.

S.-L. Chen and J.-G. Wang, “VLSI implementation of low-power cost-efficient lossless ECG

encoder design for wireless healthcare monitoring application,” Electron. Lett., vol. 49, no. 2, pp.

91–93, 2013.

“ECG/ EKG.” [Online]. Available: https://glneurotech.com/FAQ/ecg

_ekg.html. [Accessed: 03-Jun-2019].

C.-I. Ieong, M. Li, M.-K. Law, P.-I. Mak, M. I. Vai, and R. P. Martins, “A 0.45 V 147–375 nW

ECG Compression Processor With Wavelet Shrinkage and Adaptive Temporal Decimation

Architectures,” IEEE Trans. Very Large Scale Integr. Syst., vol. 25, no. 4, pp. 1307–1319, Apr.

2017.

C. J. Deepu, X. Zhang, C. H. Heng, and Y. Lian, “A 3-Lead ECG-on-chip with QRS detection and

lossless compression for wireless sensors,” IEEE Trans. Circuits Syst. II Express Briefs, vol. 63,

no. 12, pp. 1151–1155, Dec. 2016.

VLSI Design & Embedded Systems](https://image.slidesharecdn.com/mohans04-230119141355-a2c83b1f/85/ECG-compression-in-vlsi-28-320.jpg)