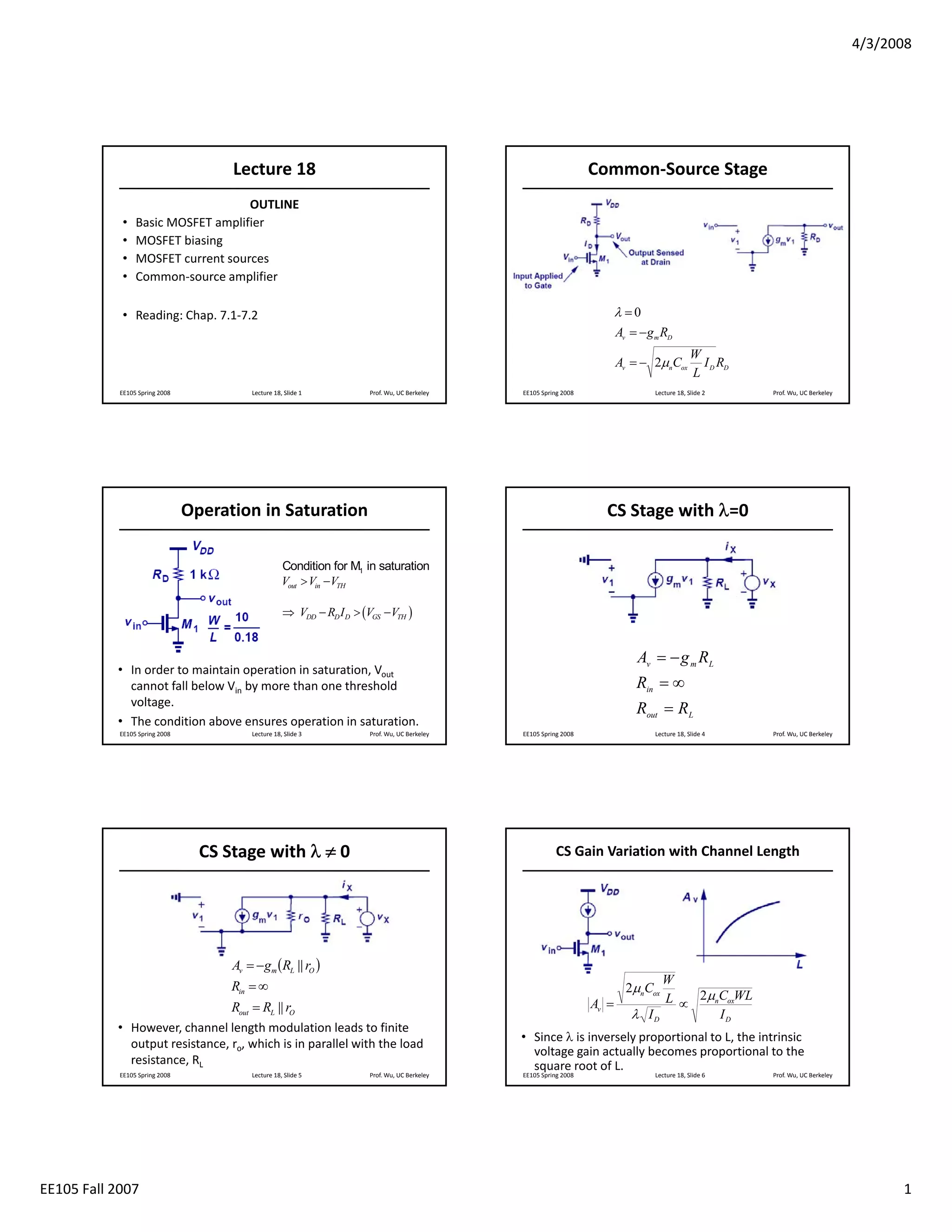

This document summarizes a lecture about common-source (CS) MOSFET amplifier stages. It discusses the basic CS amplifier configuration and how its voltage gain is determined by the transistor's transconductance and load resistance. It also covers MOSFET biasing techniques including self-biasing, and using current sources or diode-connected loads to alleviate headroom issues in the amplifier. The document provides circuit diagrams and equations for analyzing the various CS stage variations.