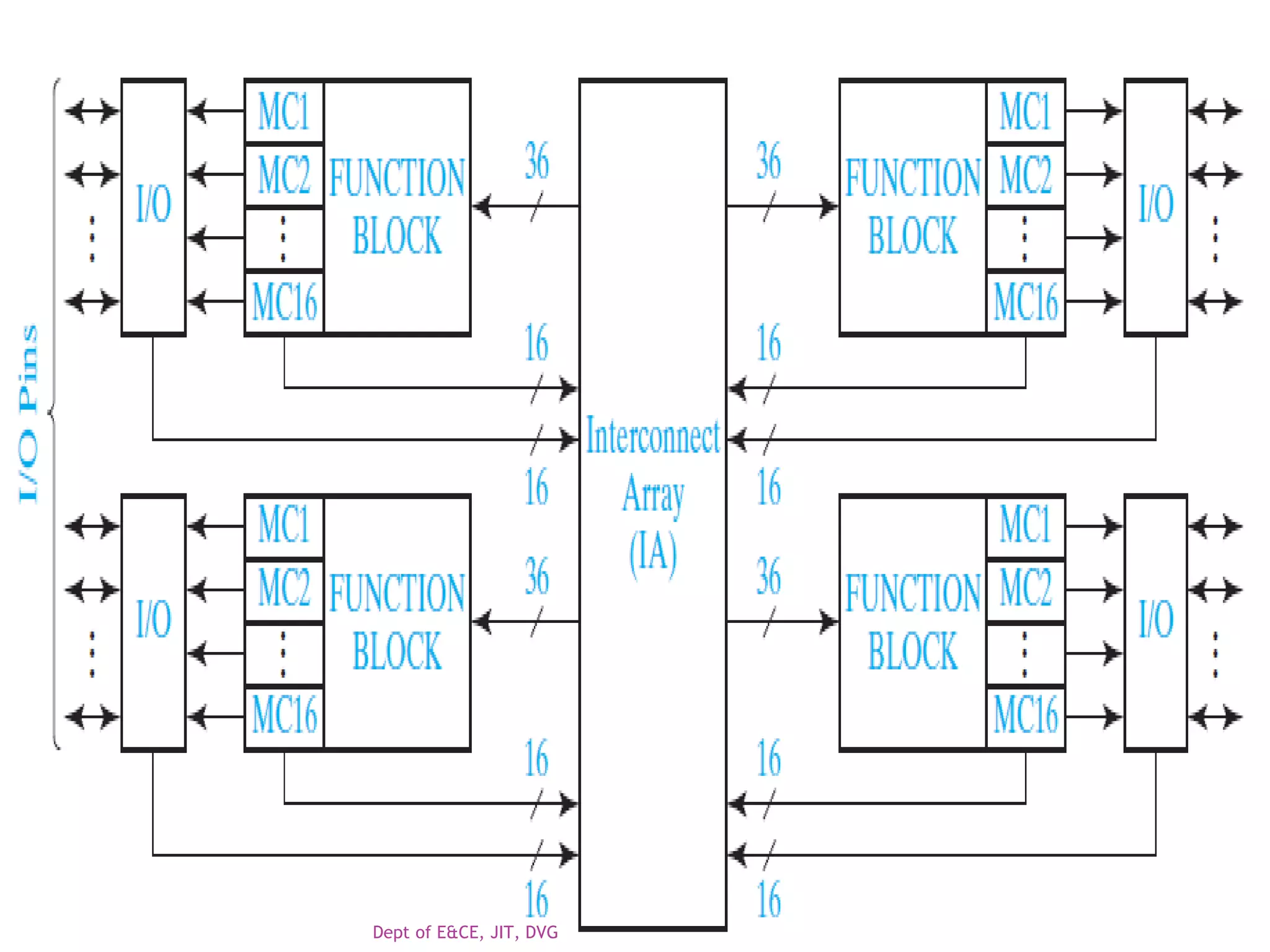

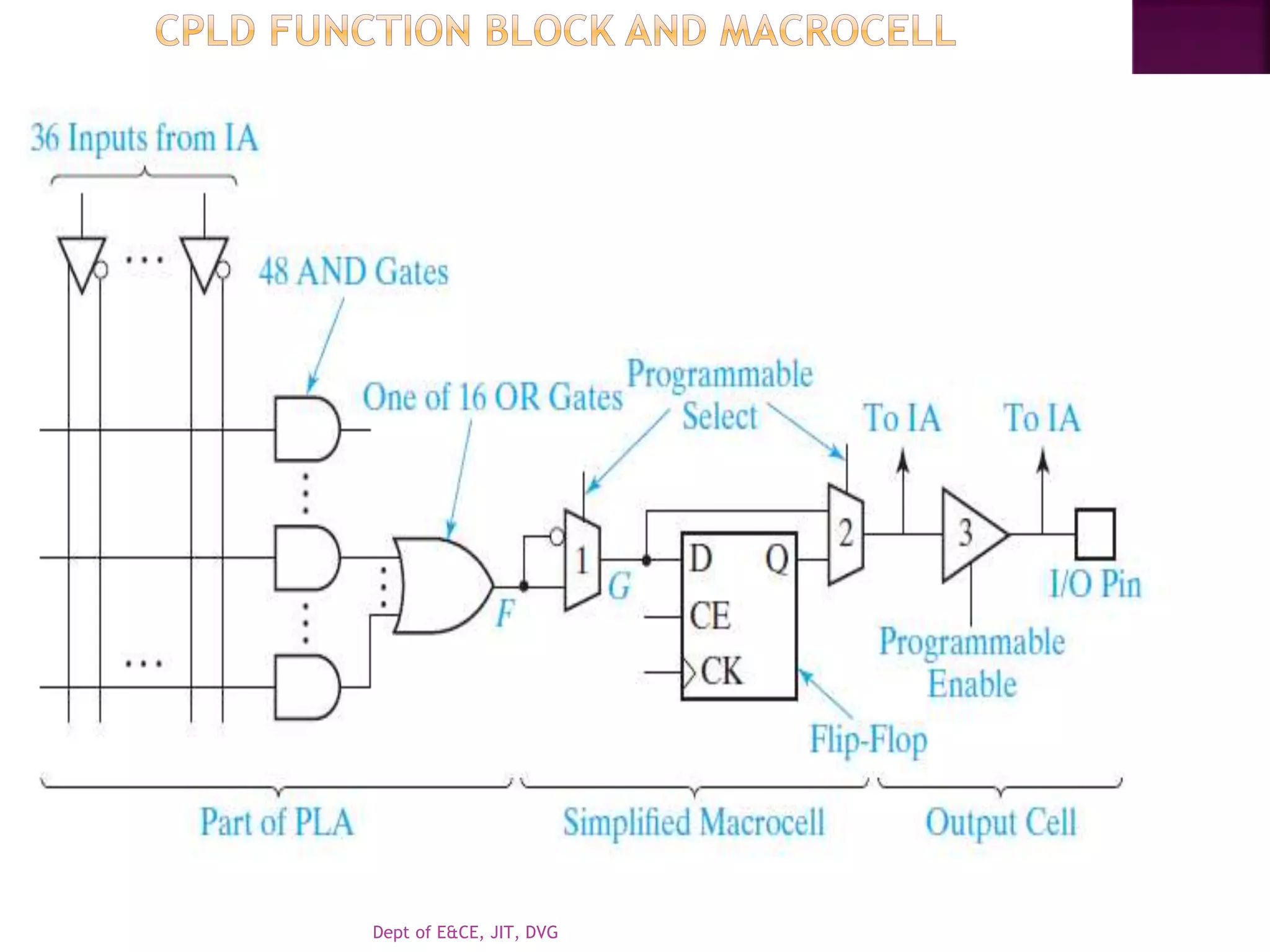

The document discusses the architecture and functionality of complex programmable logic devices (CPLDs) and field programmable gate arrays (FPGAs). It describes how CPLDs contain multiple programmable logic arrays (PLAs) that can be interconnected on a single chip. FPGAs contain an array of identical logic blocks with programmable interconnections that allow any function to be implemented. The architecture of a basic Xilinx CPLD and the logic blocks in a typical FPGA are illustrated, including configurable logic blocks (CLBs) containing lookup tables to implement functions.