The document discusses the architecture and functionality of complex programmable logic devices (CPLDs) and field programmable gate arrays (FPGAs). It provides details on:

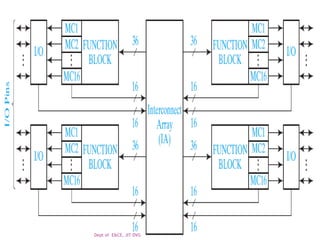

1) The basic architecture of the Xilinx XCR3064XL CPLD, which contains four programmable function blocks with associated macrocells and interconnect architecture.

2) The internal structure of a configurable logic block (CLB) in a typical FPGA, including lookup tables, multiplexers, and flip-flops.

3) How Boolean functions with more variables than the number supported by a CLB can be decomposed using Shannon expansion into subfunctions that fit within the CLB resources.