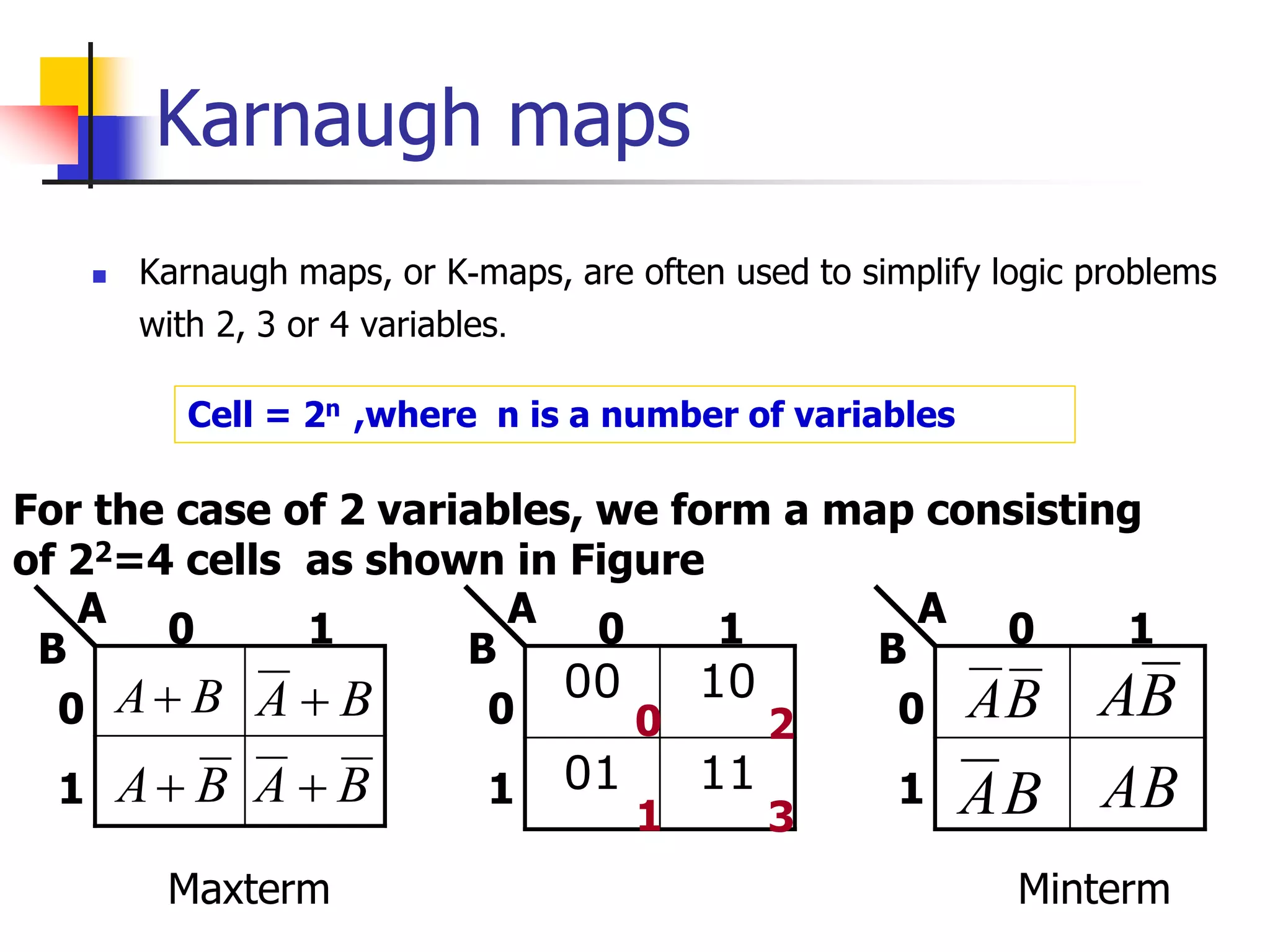

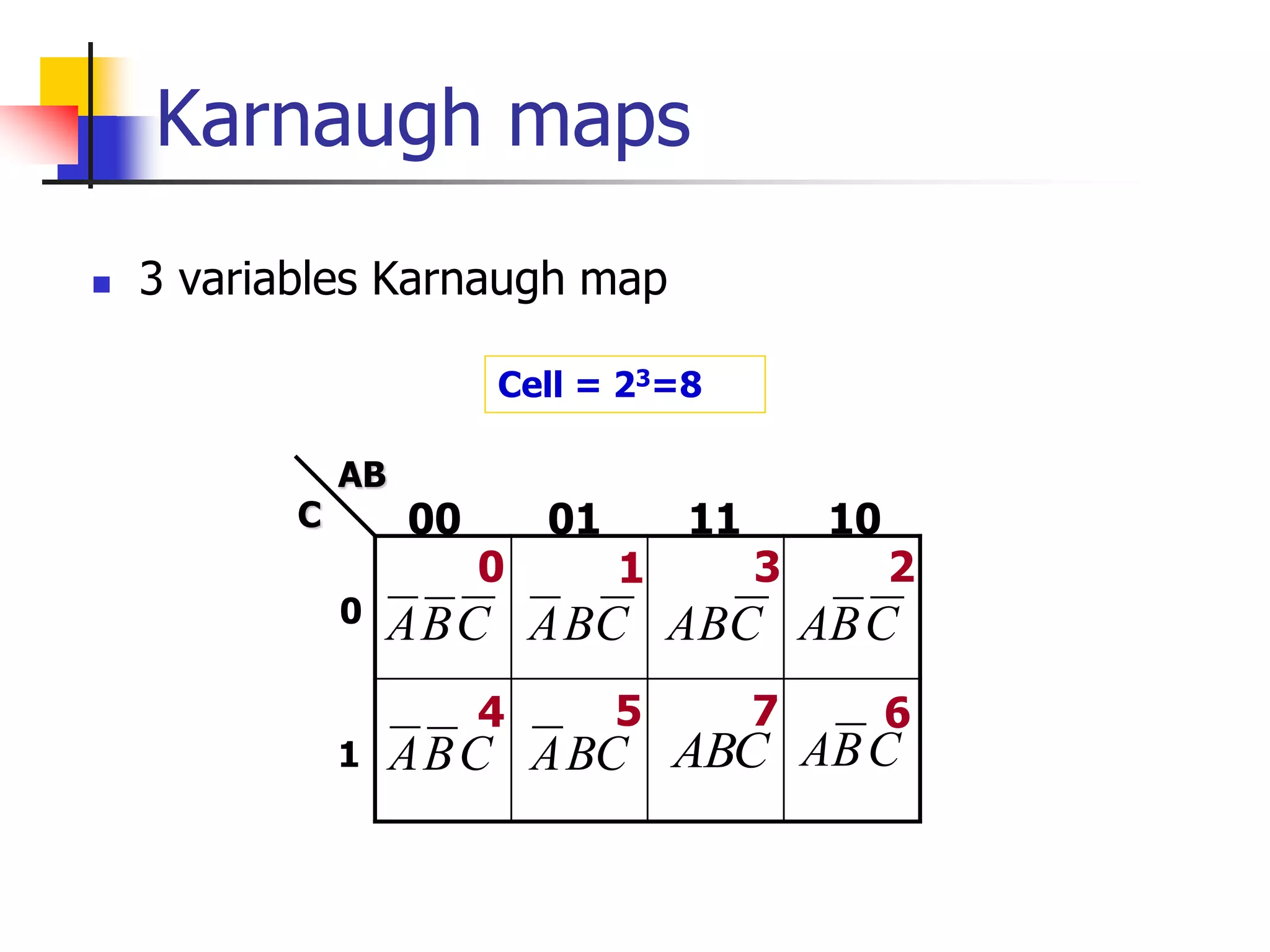

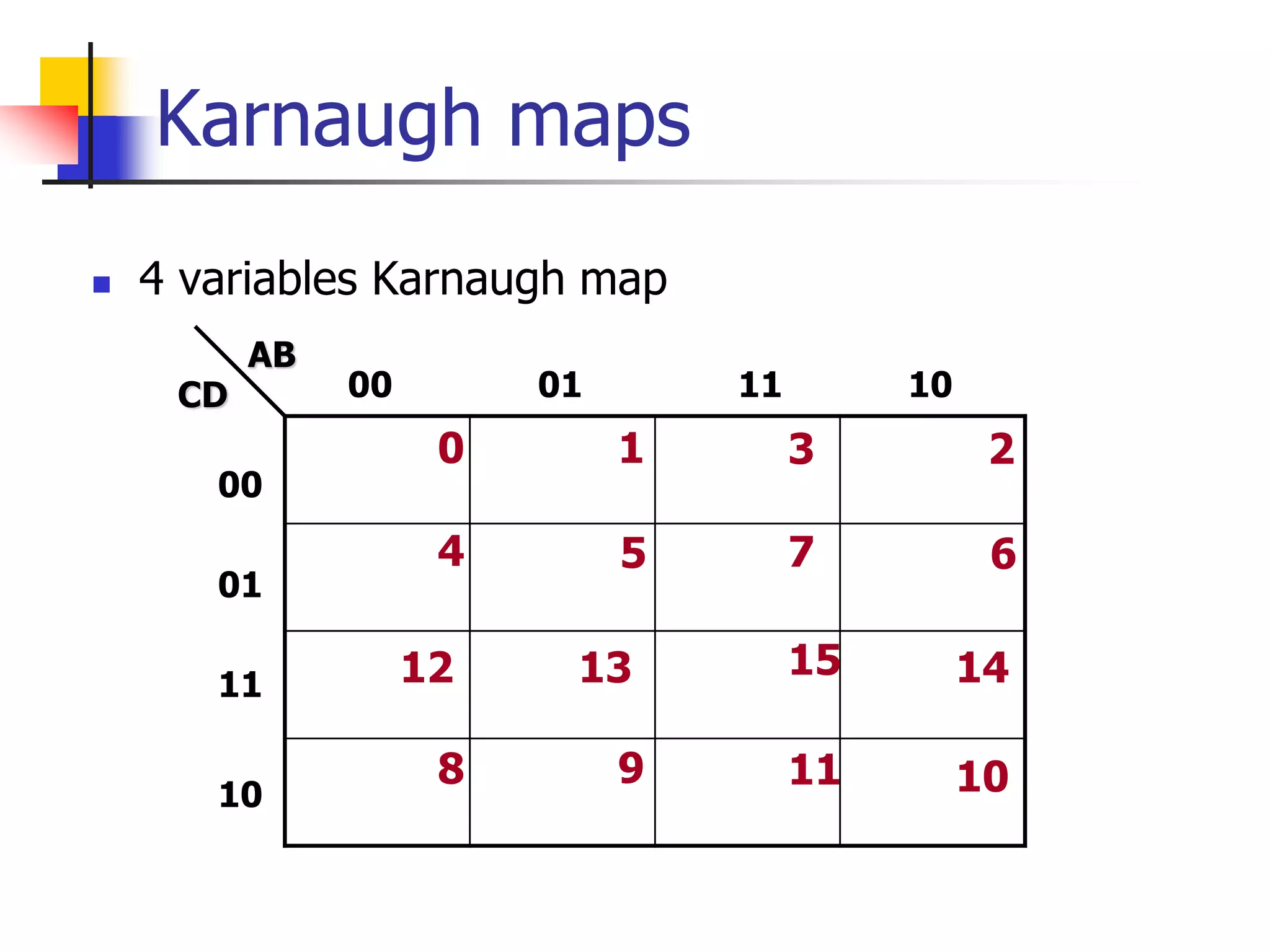

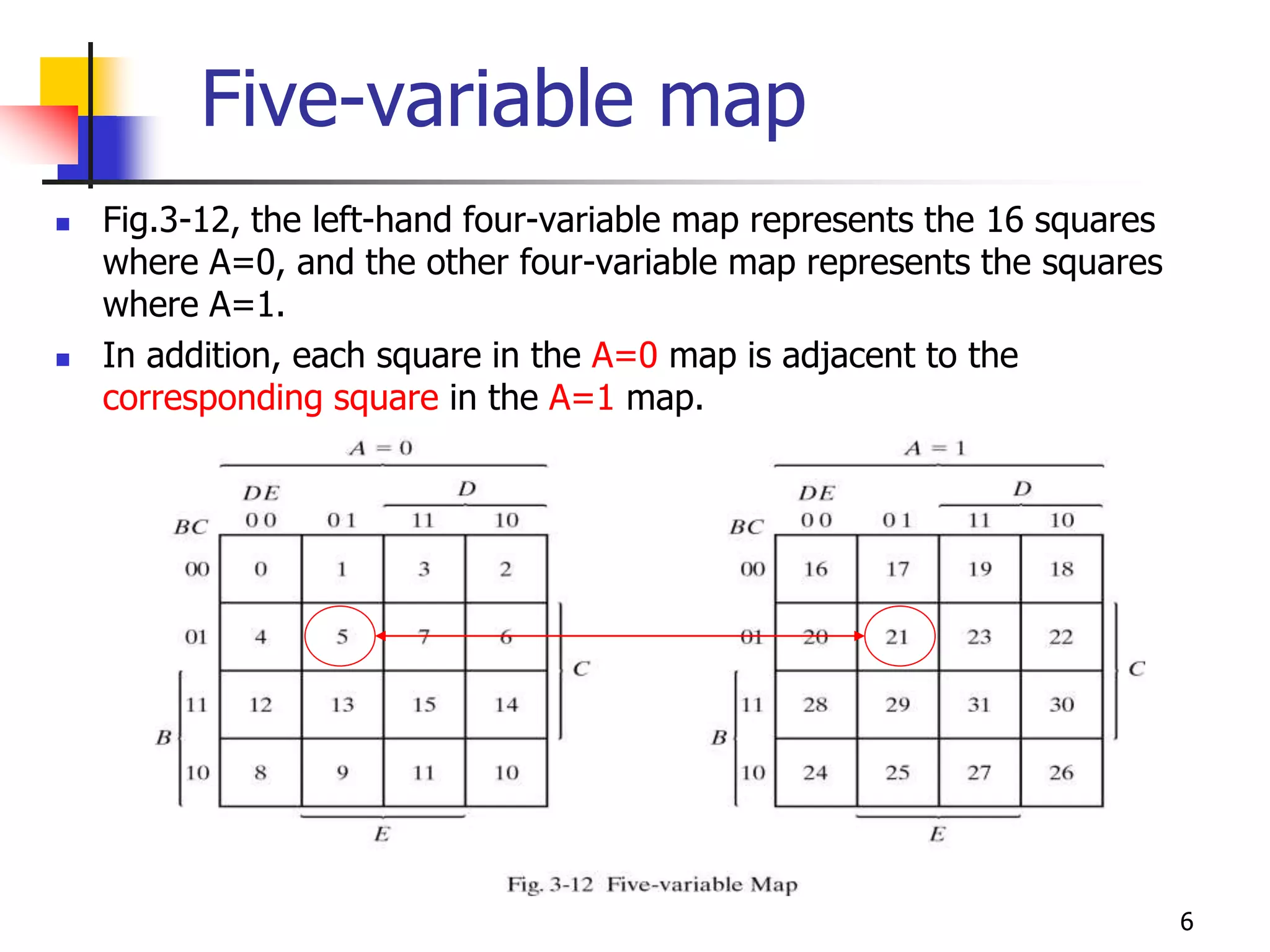

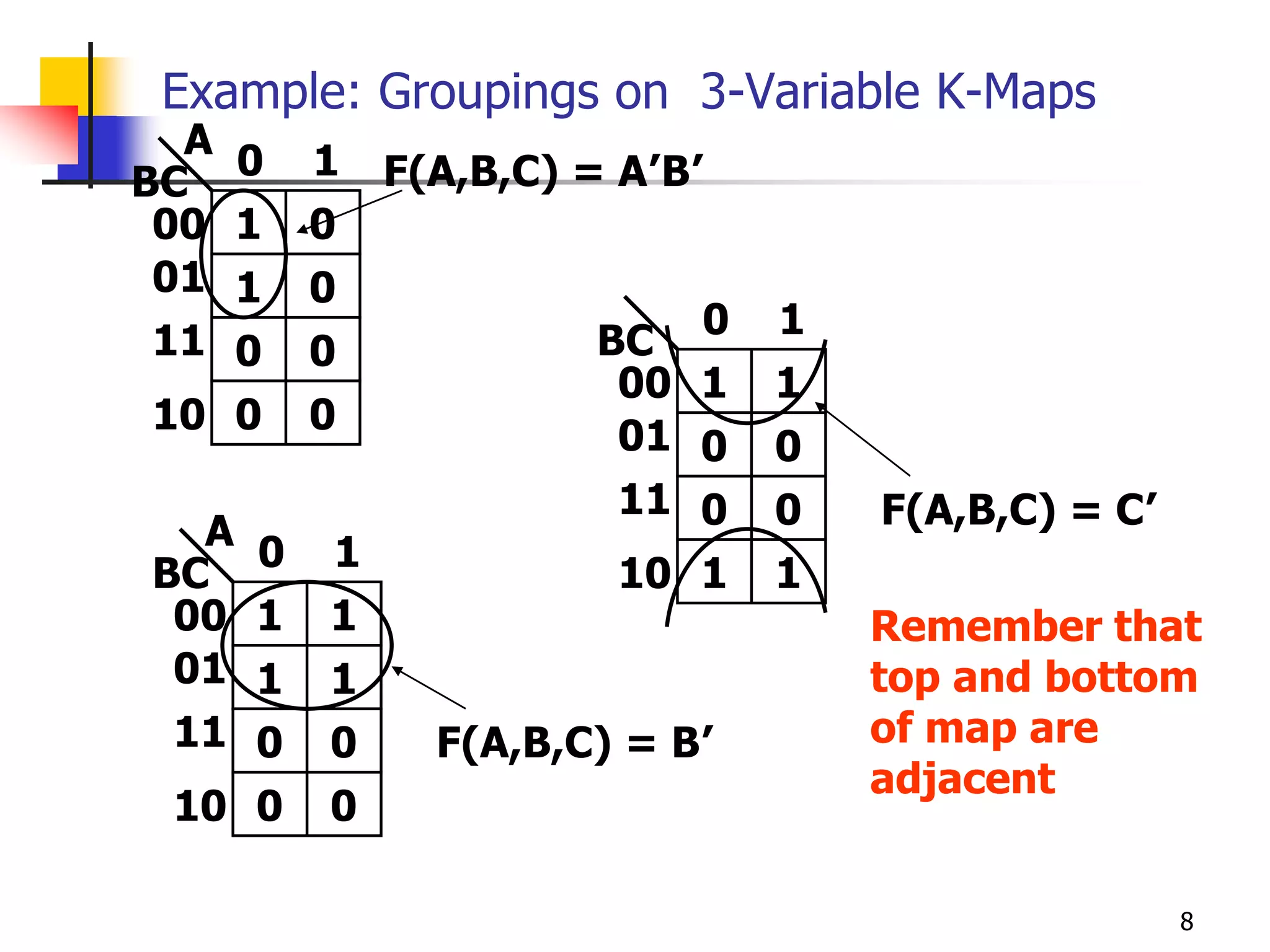

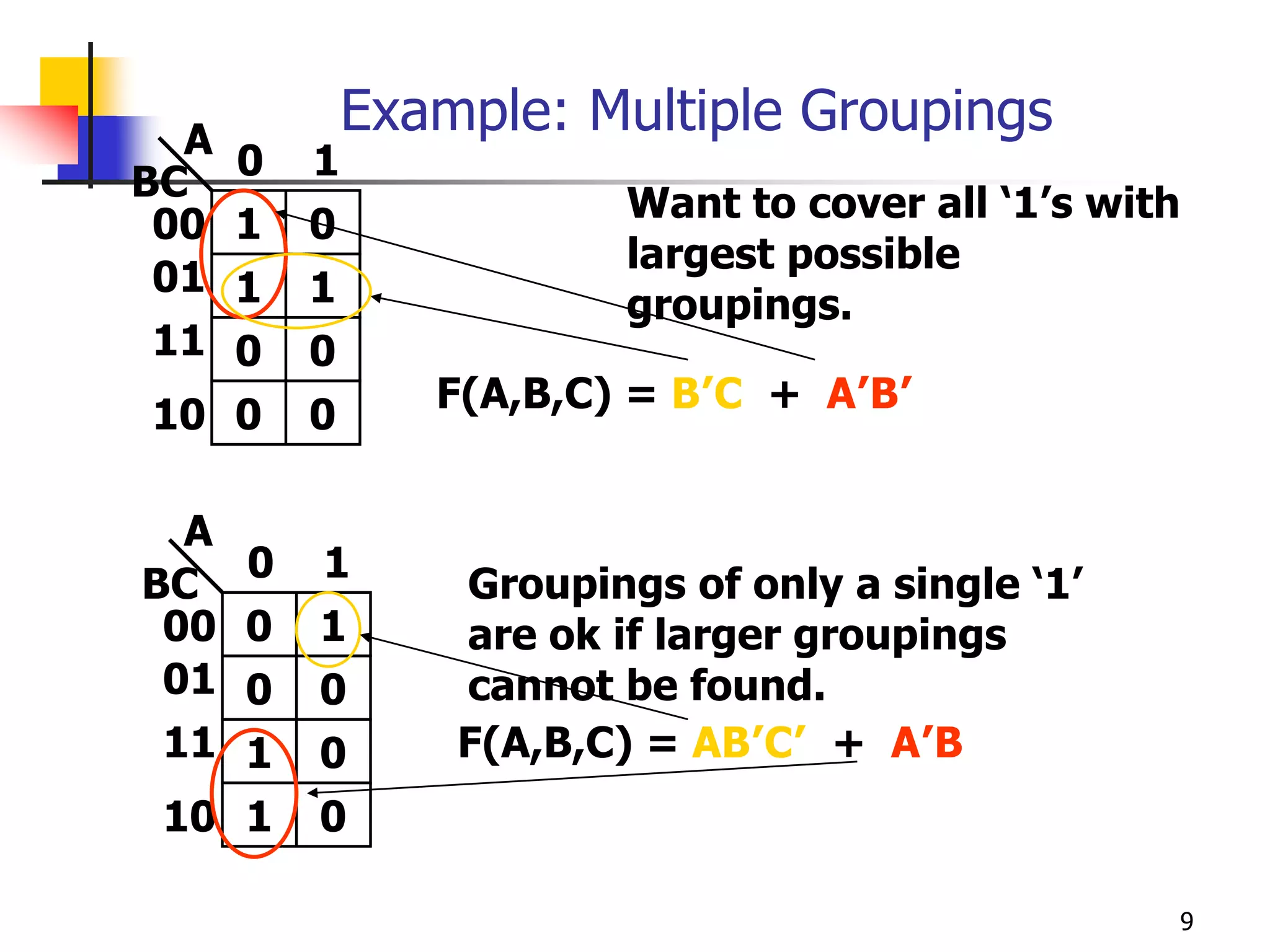

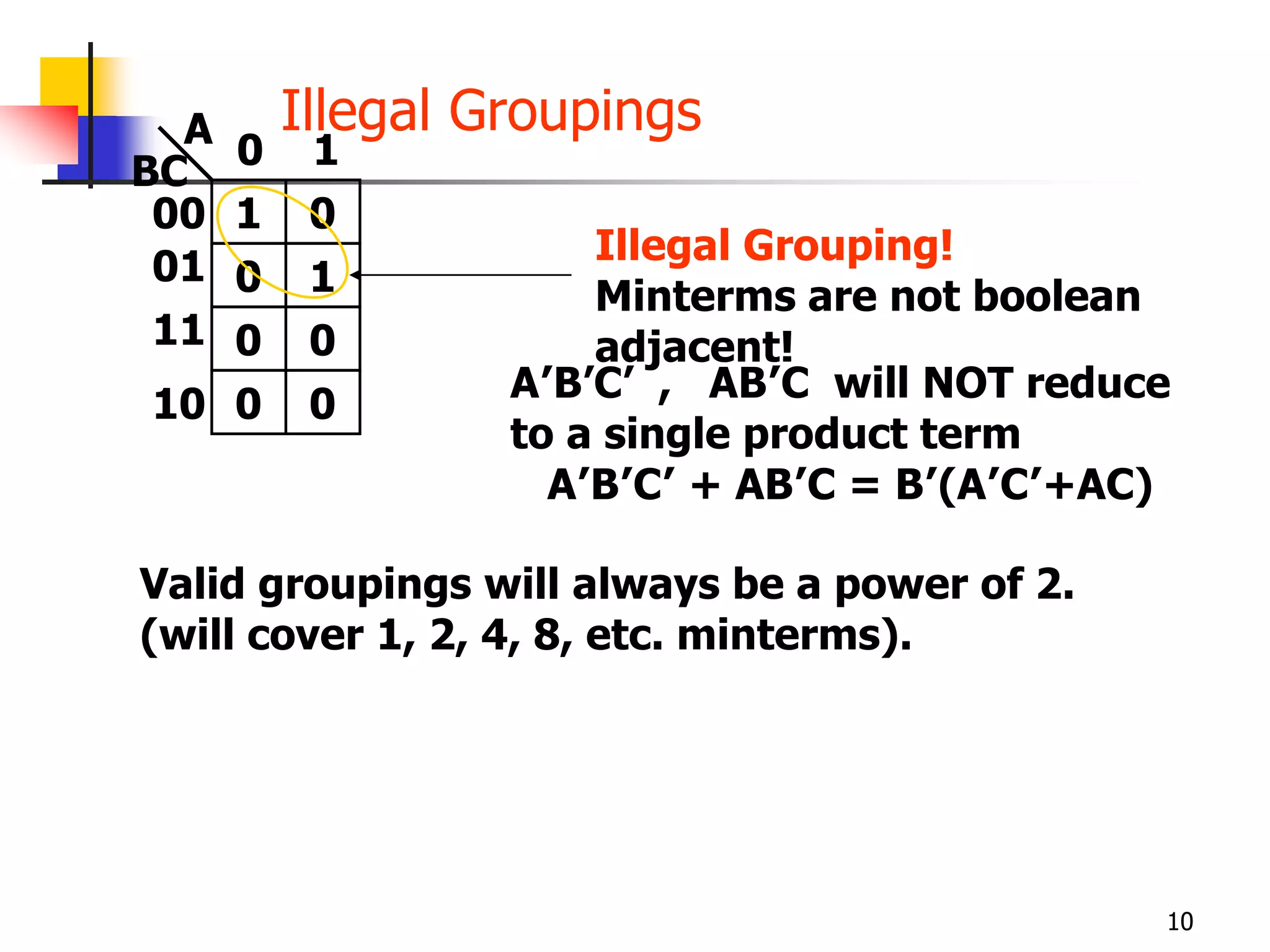

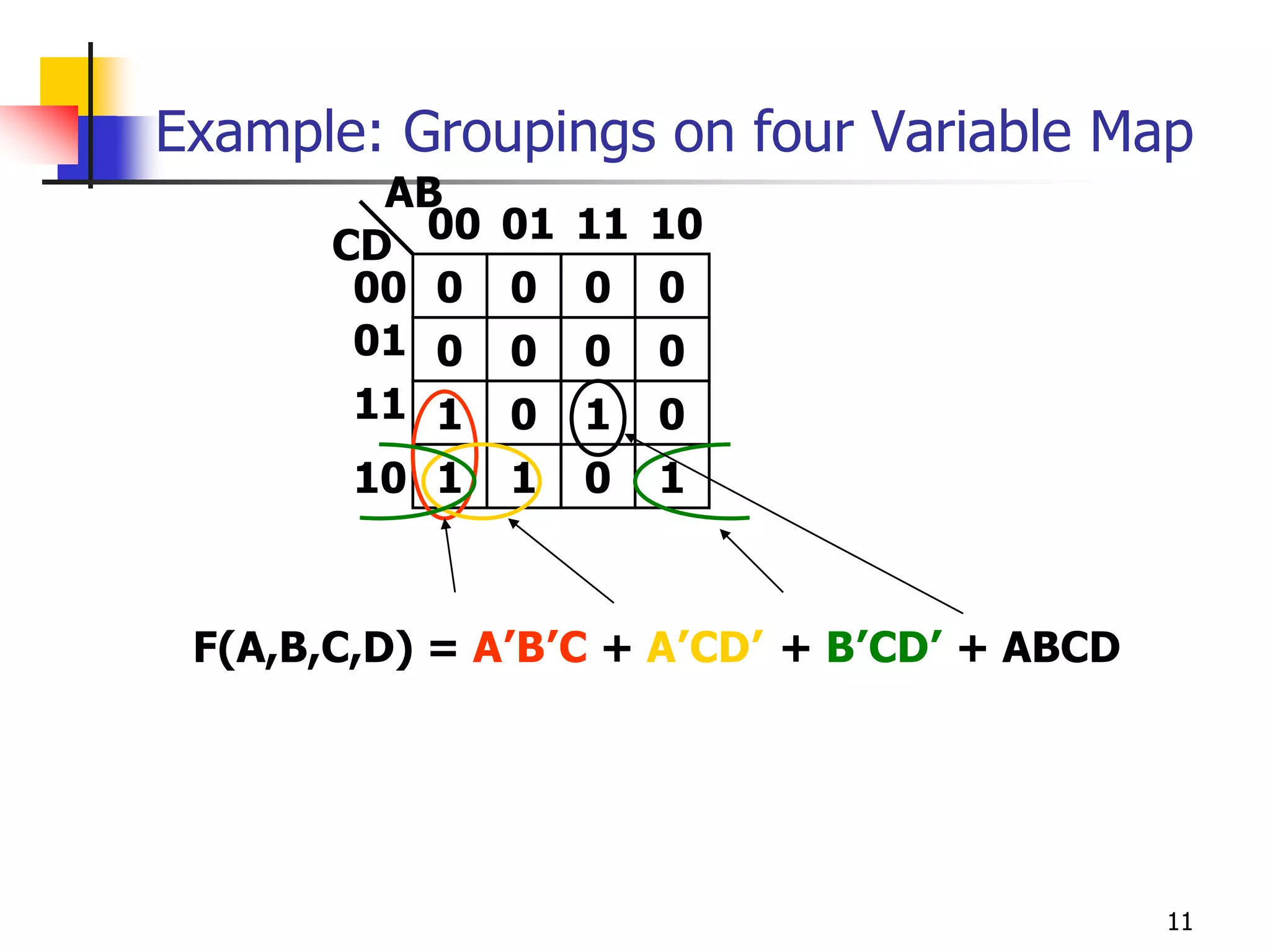

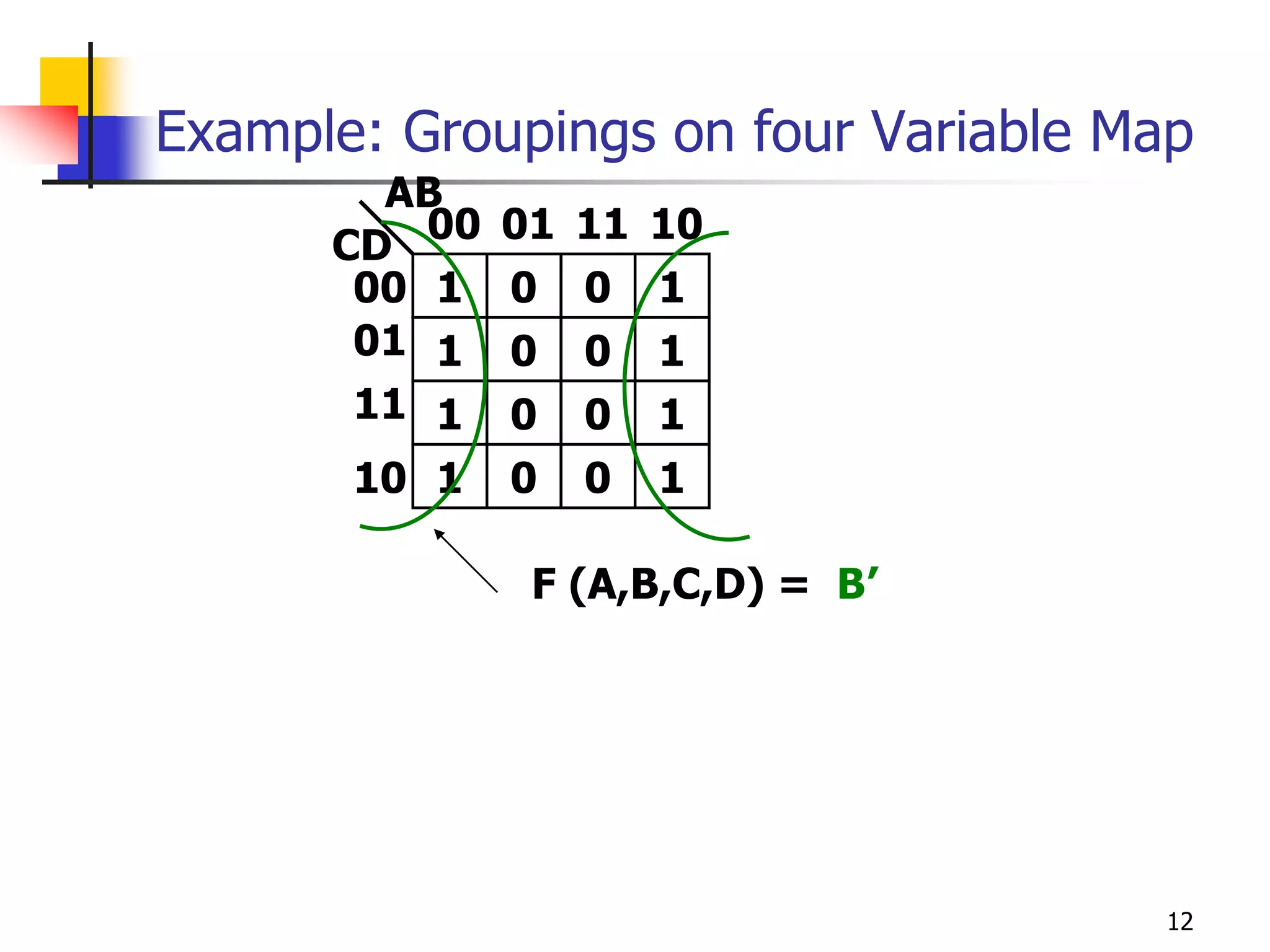

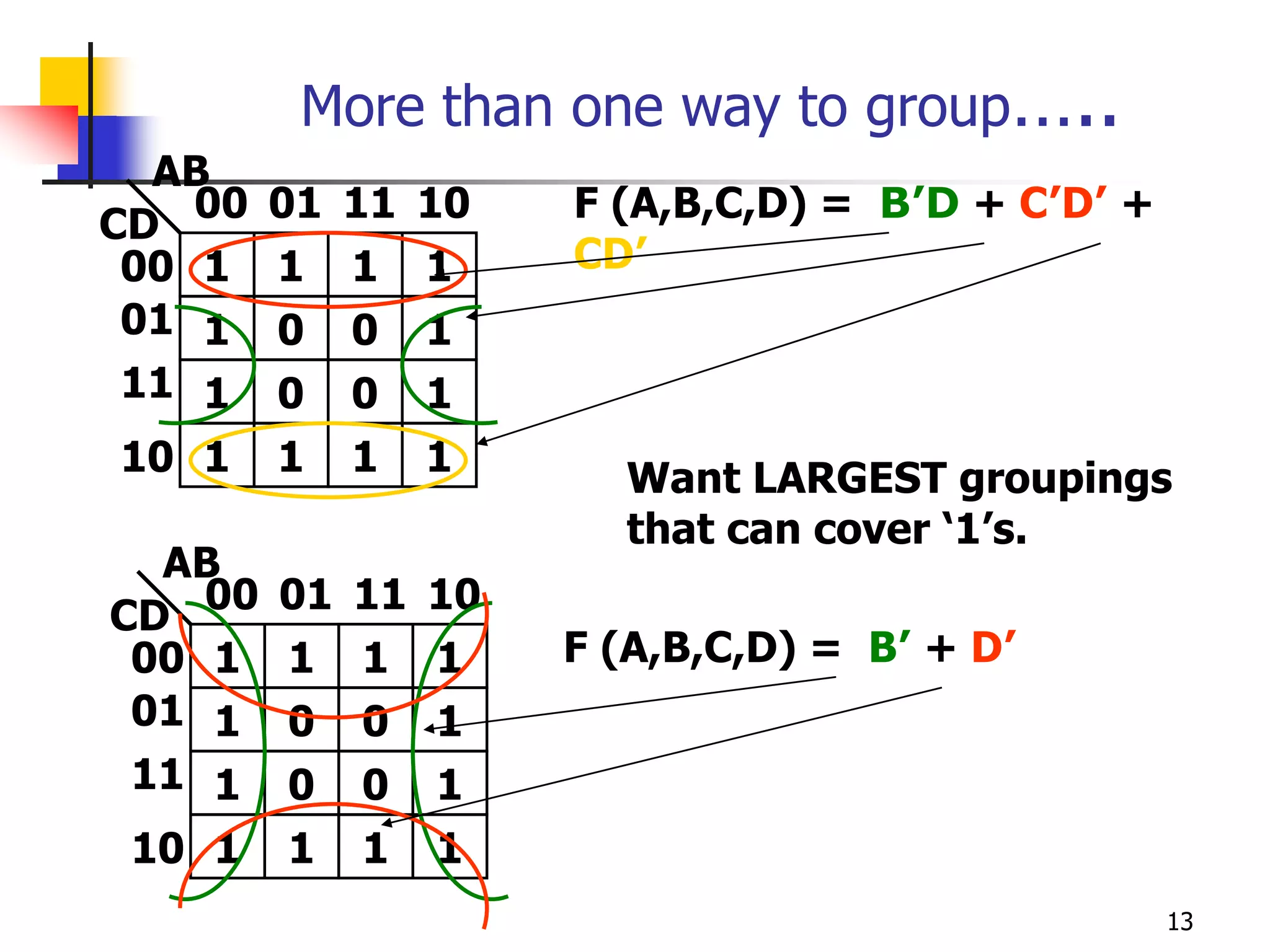

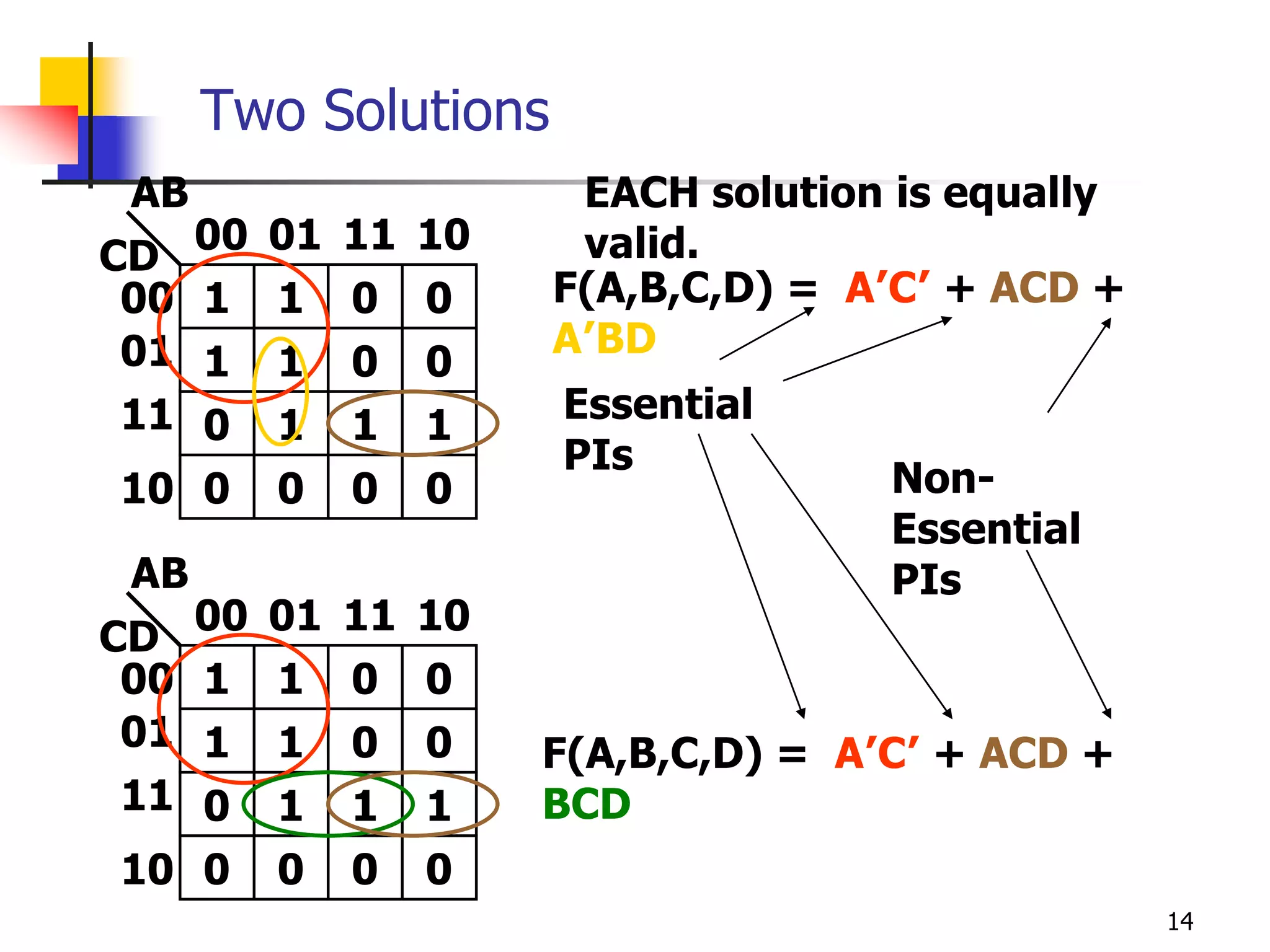

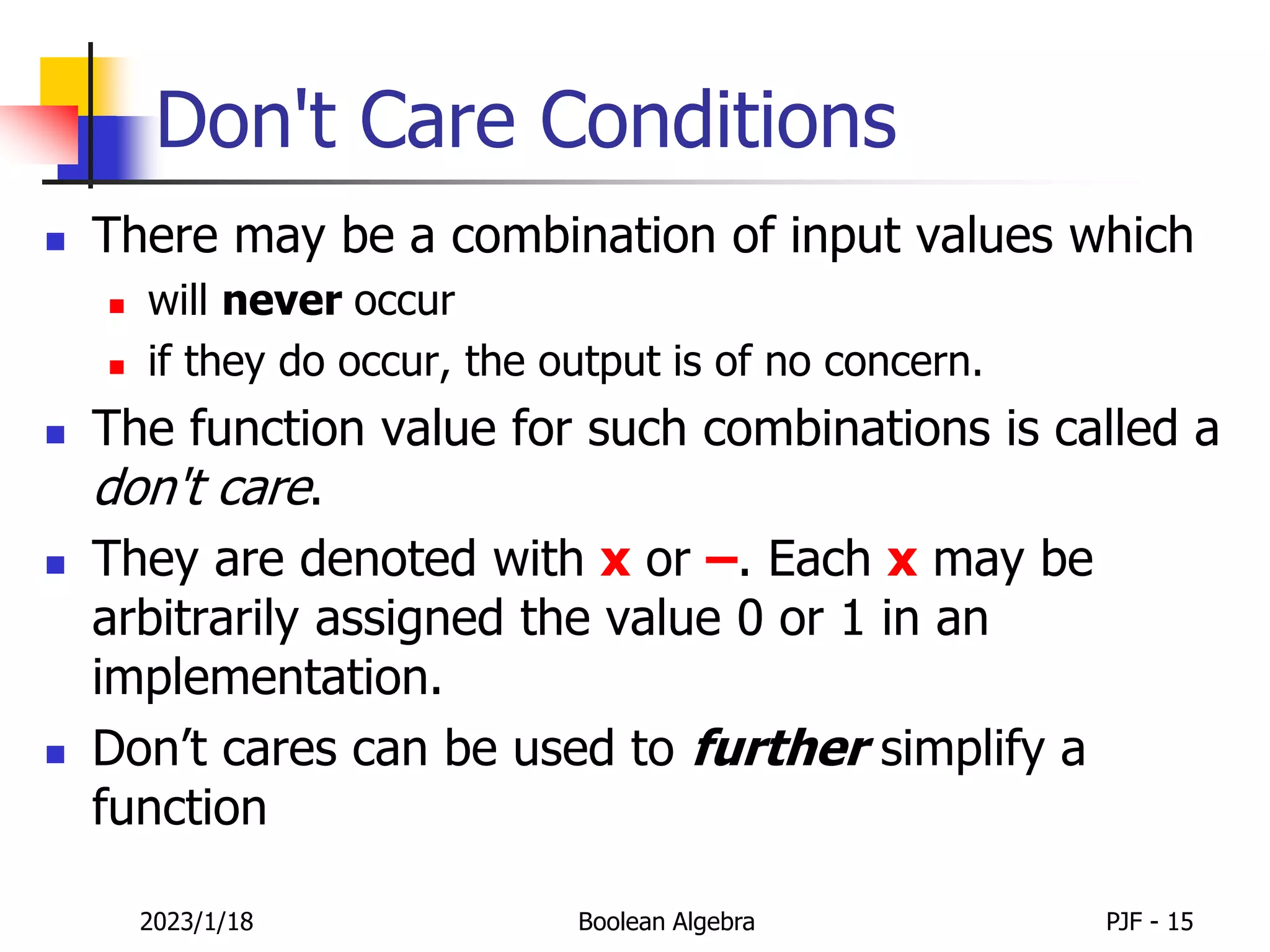

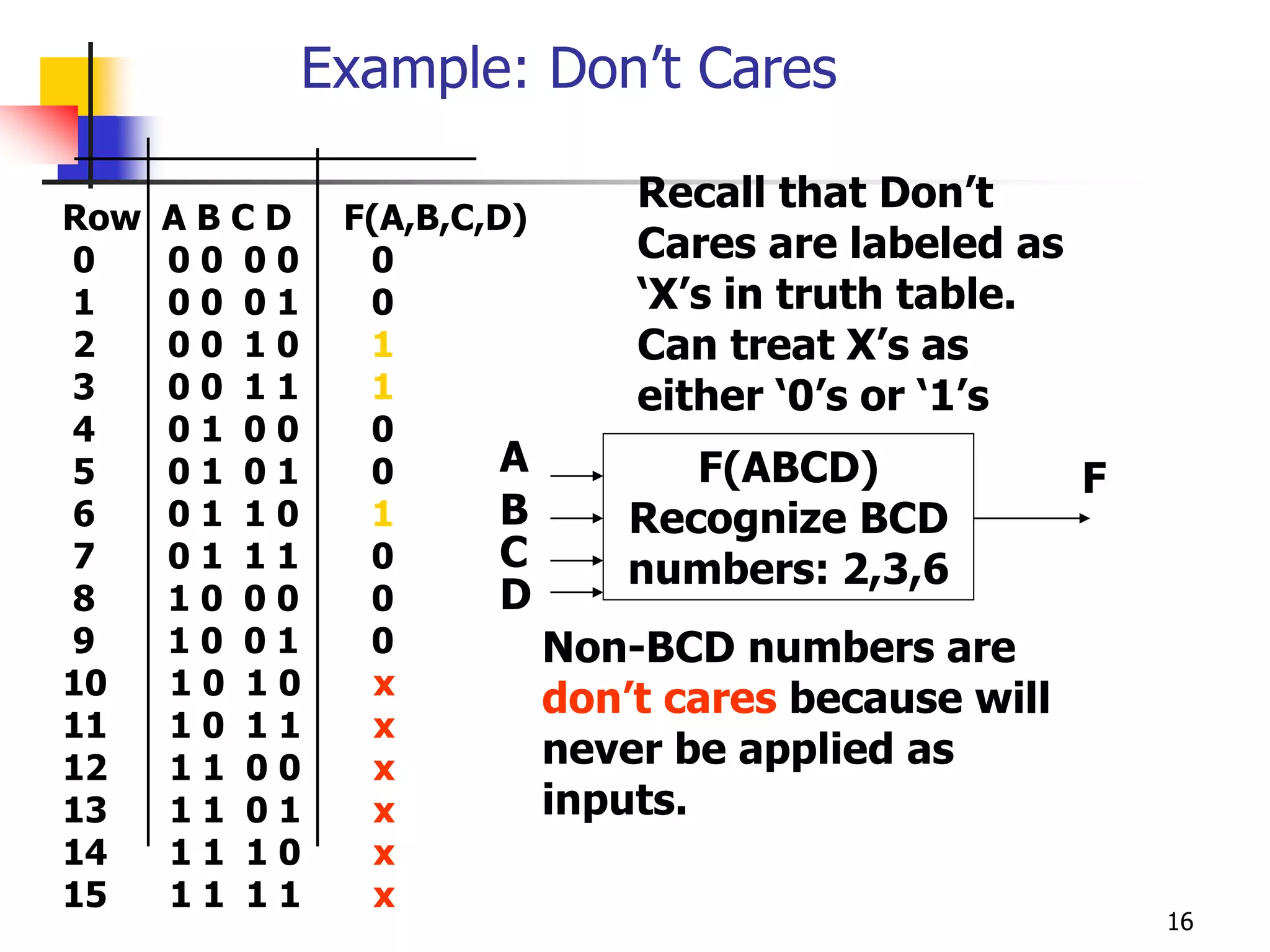

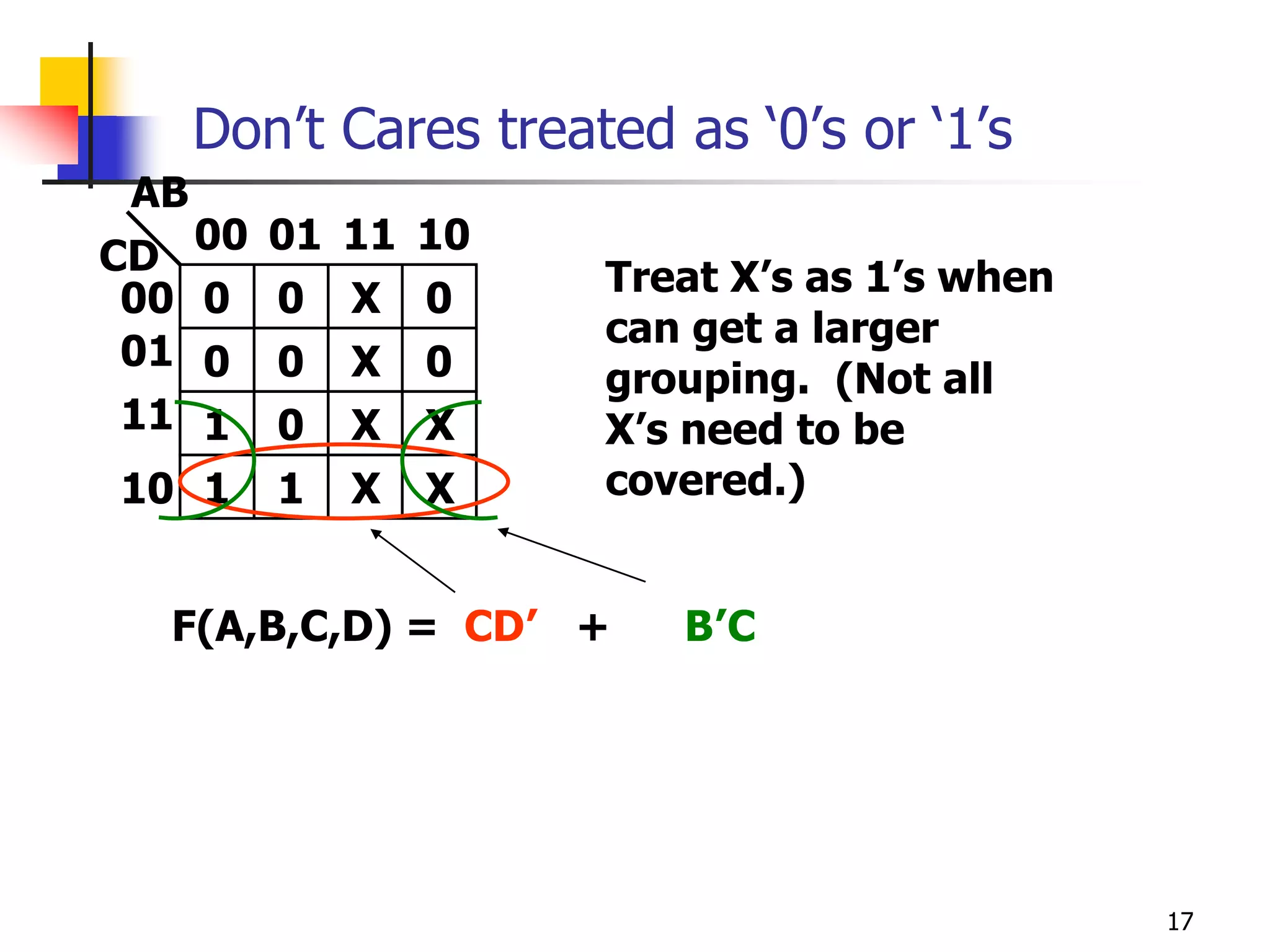

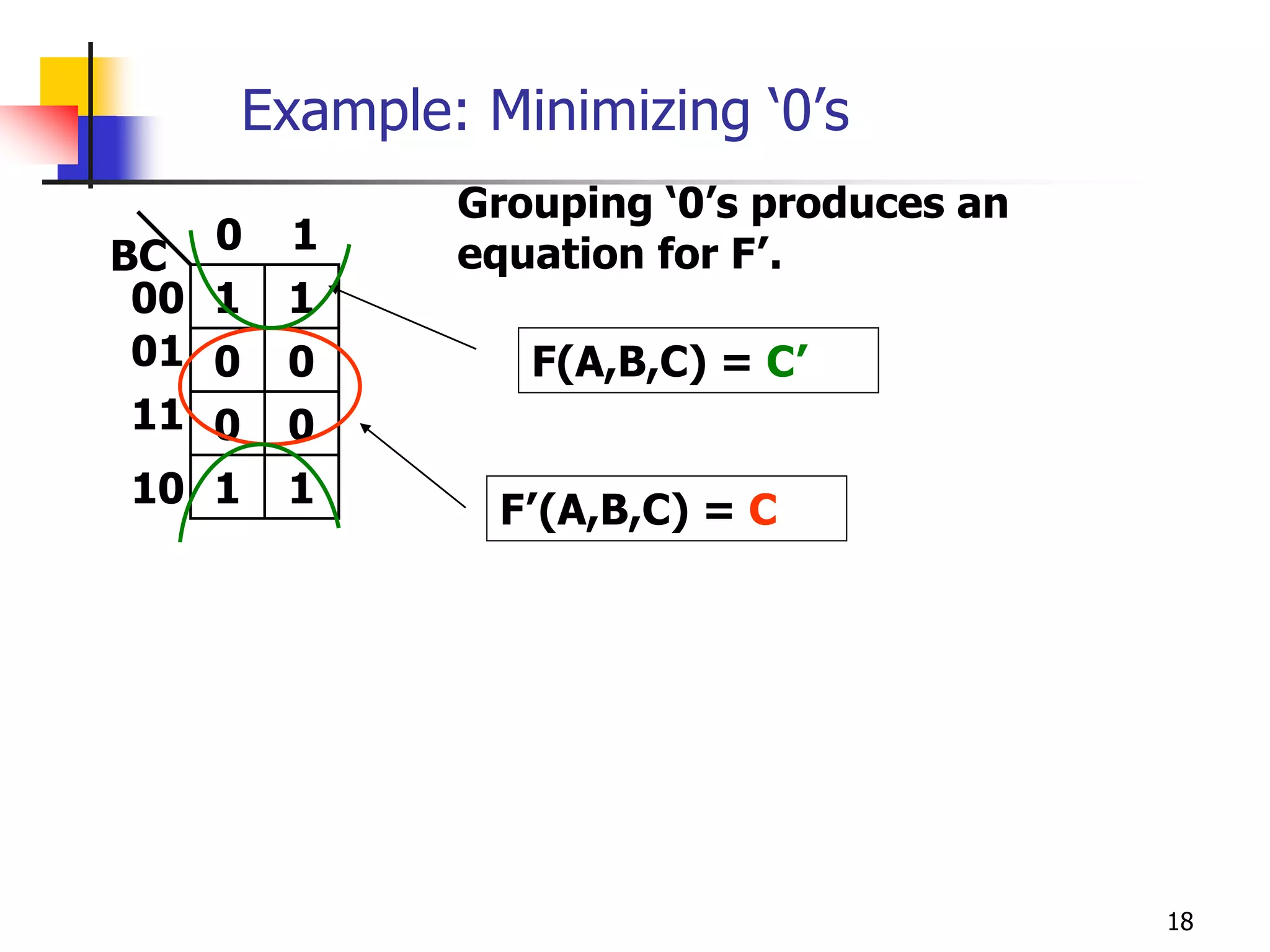

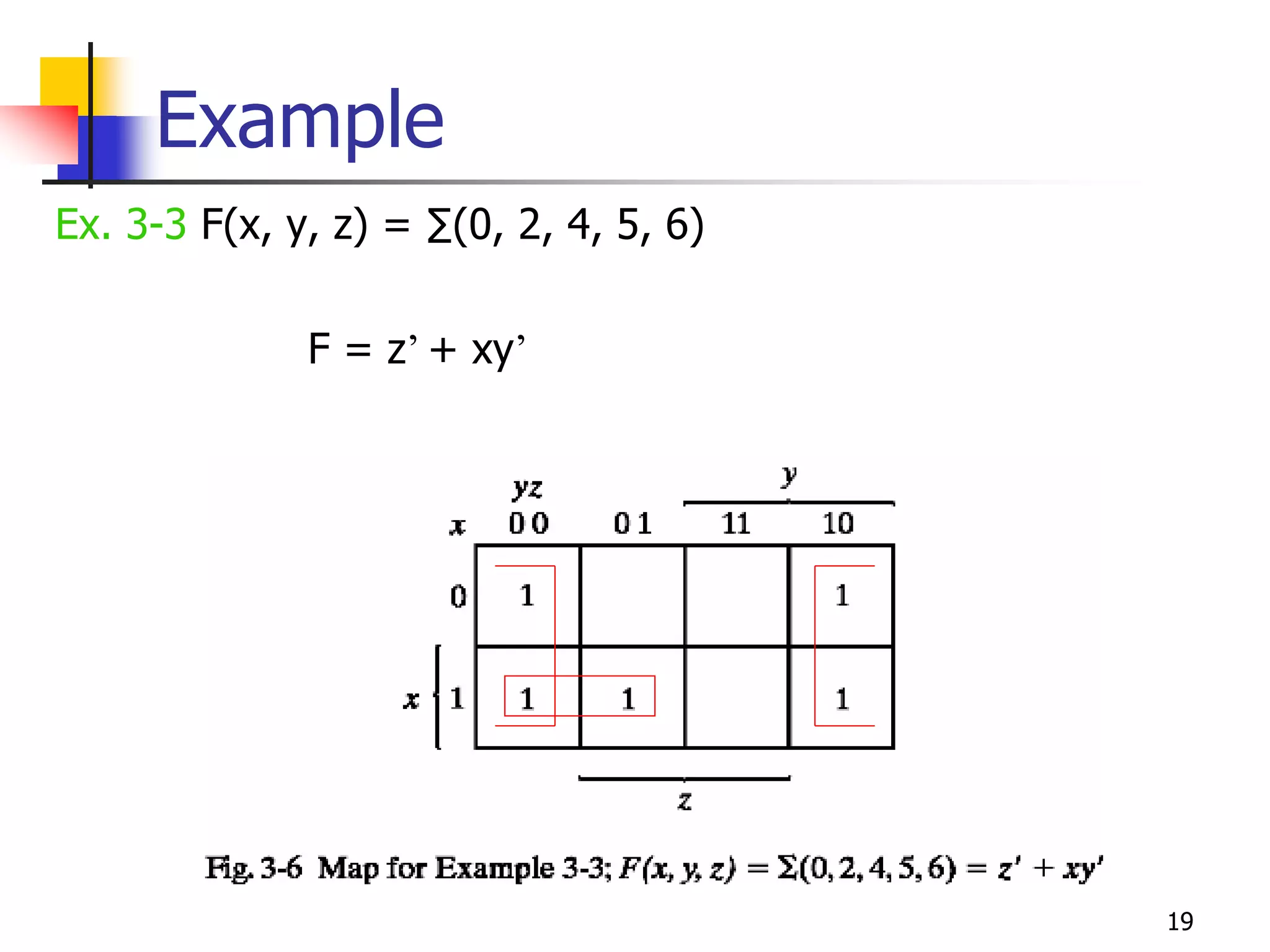

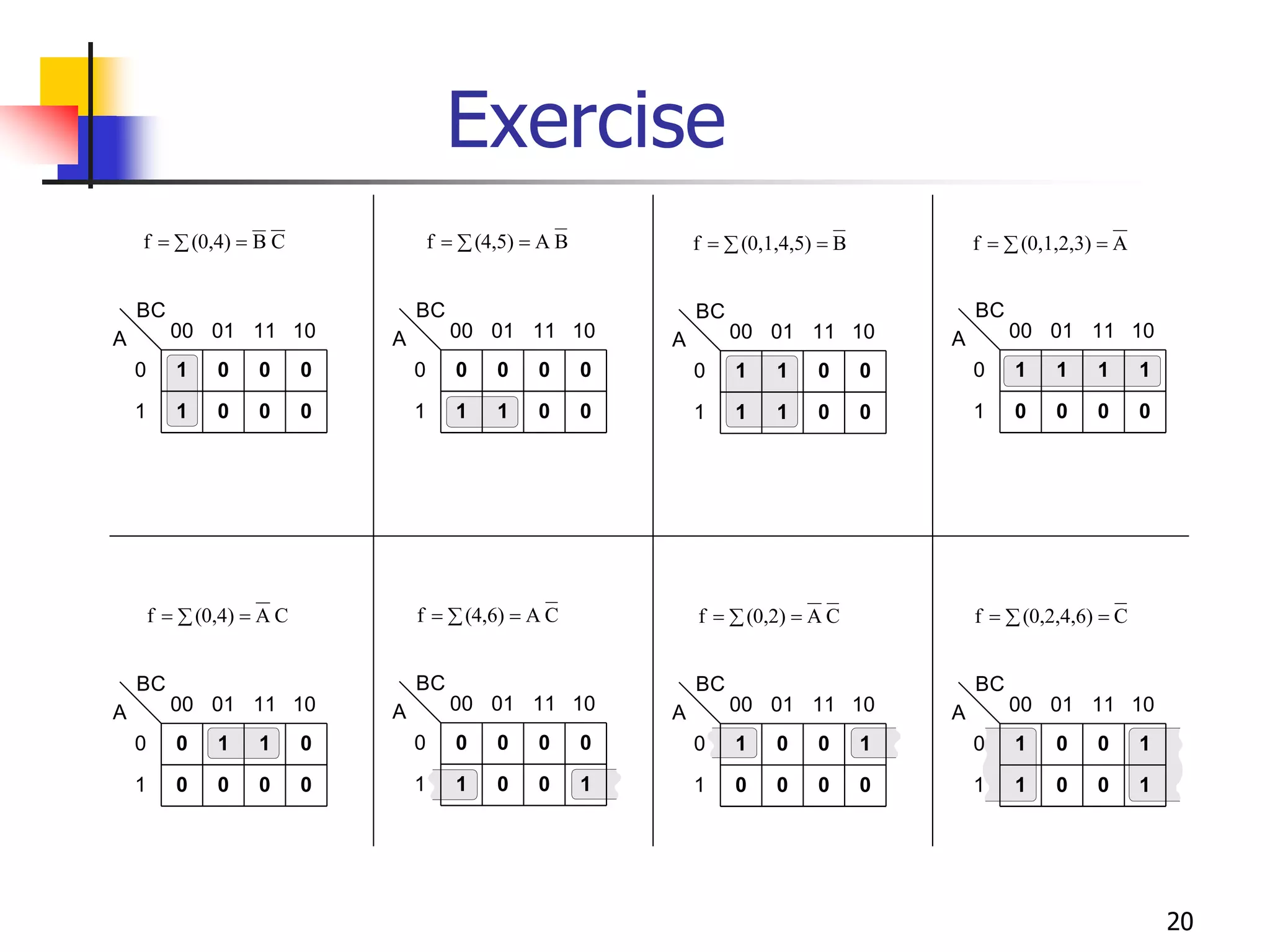

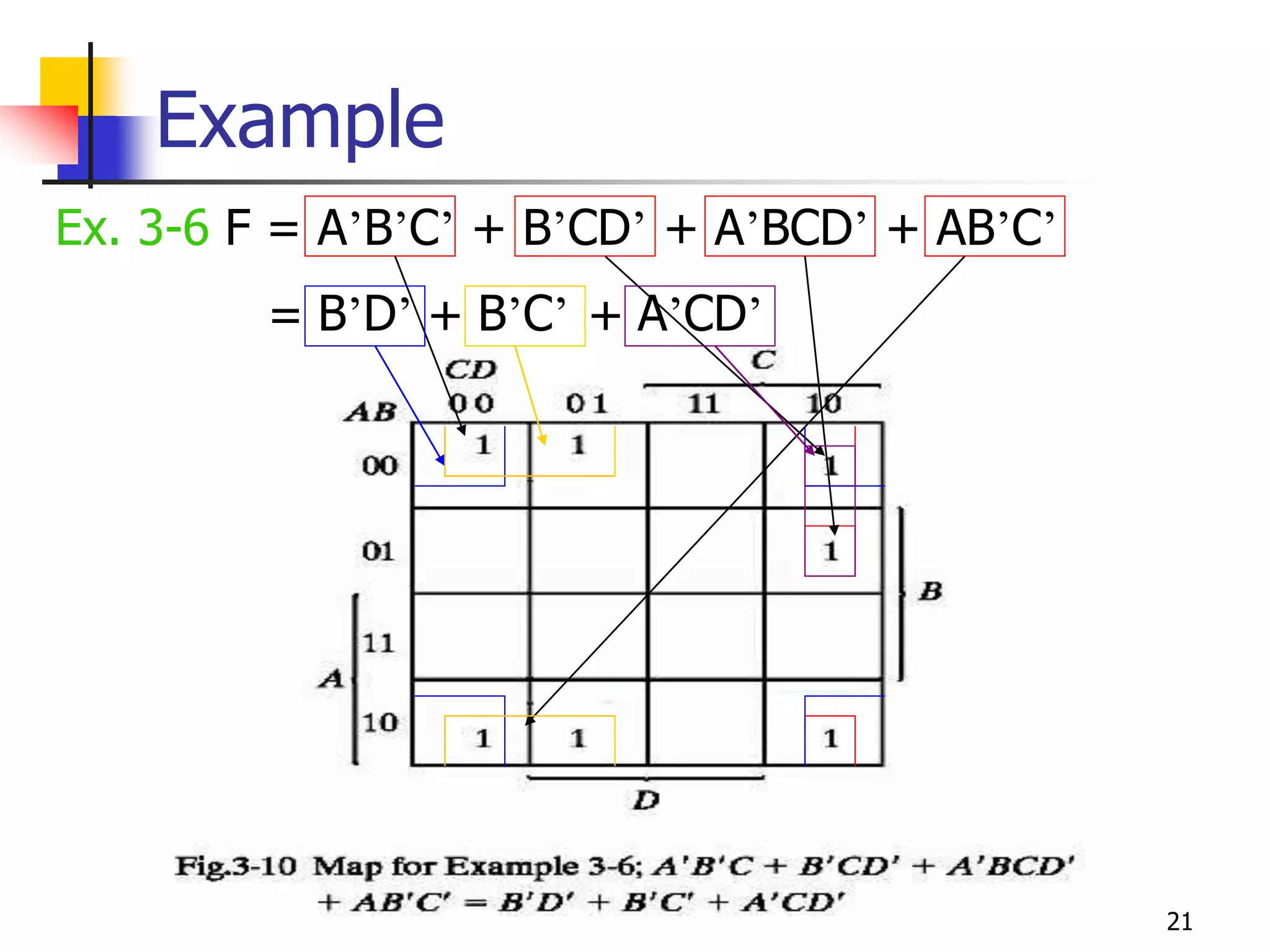

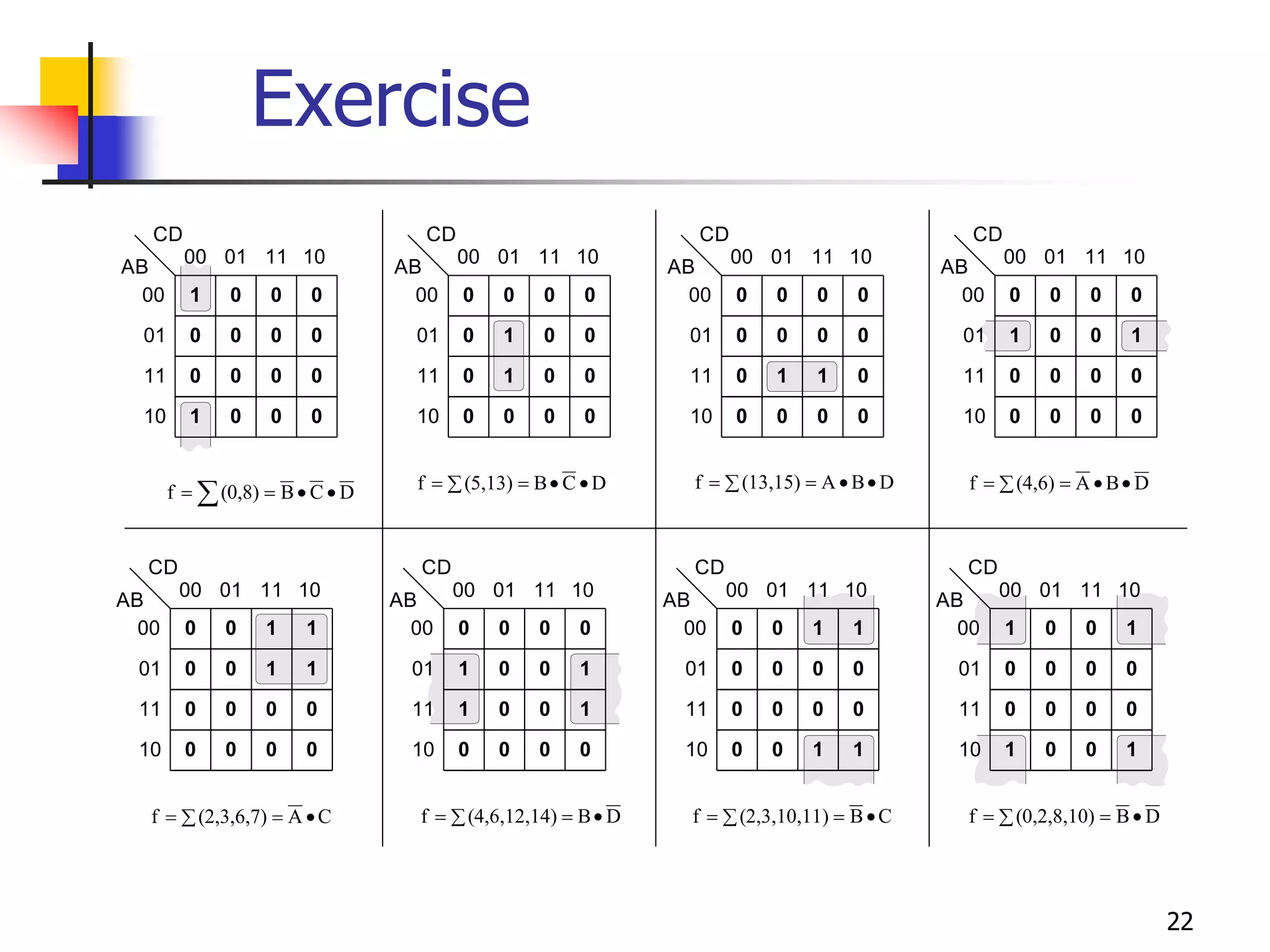

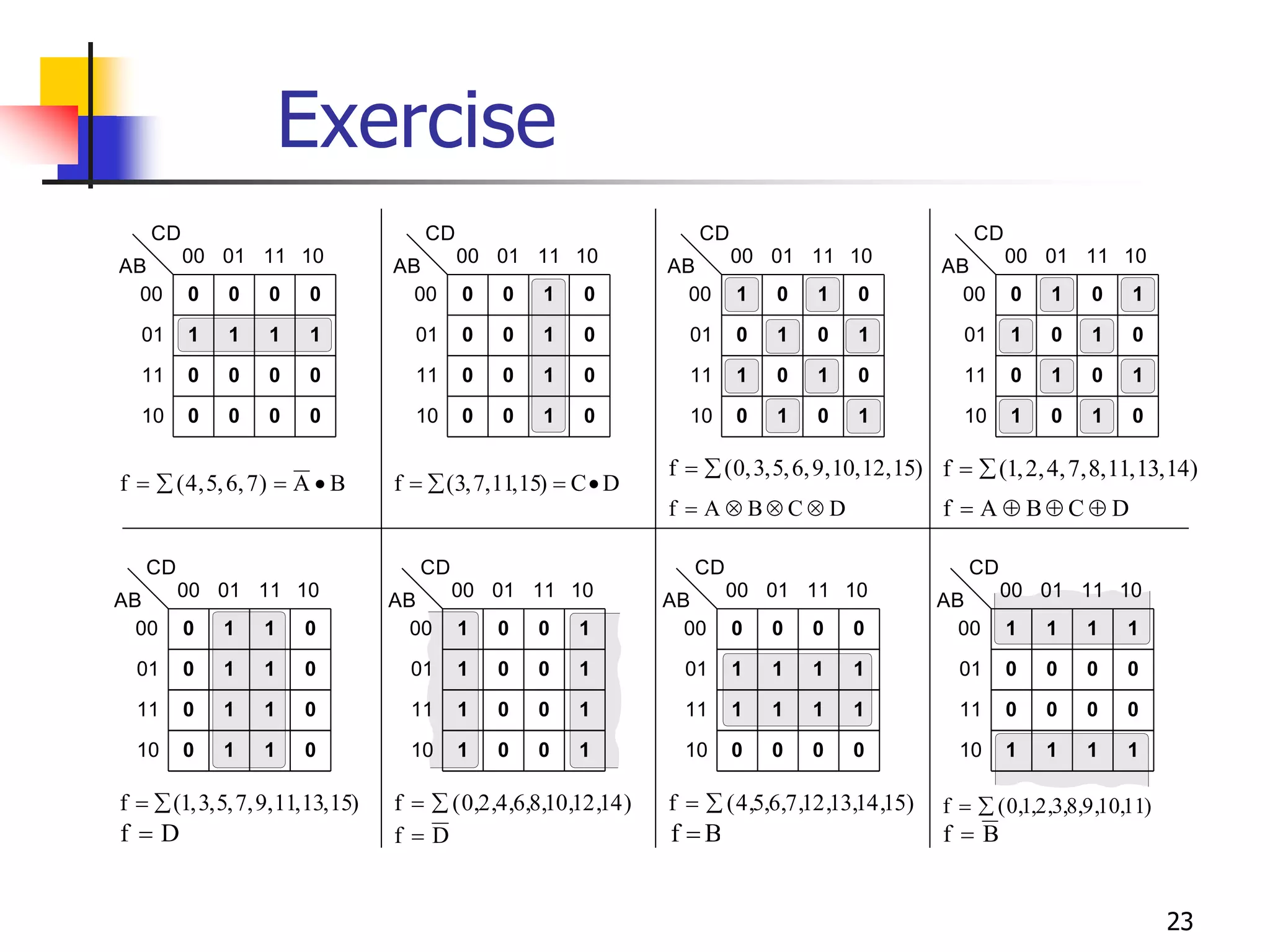

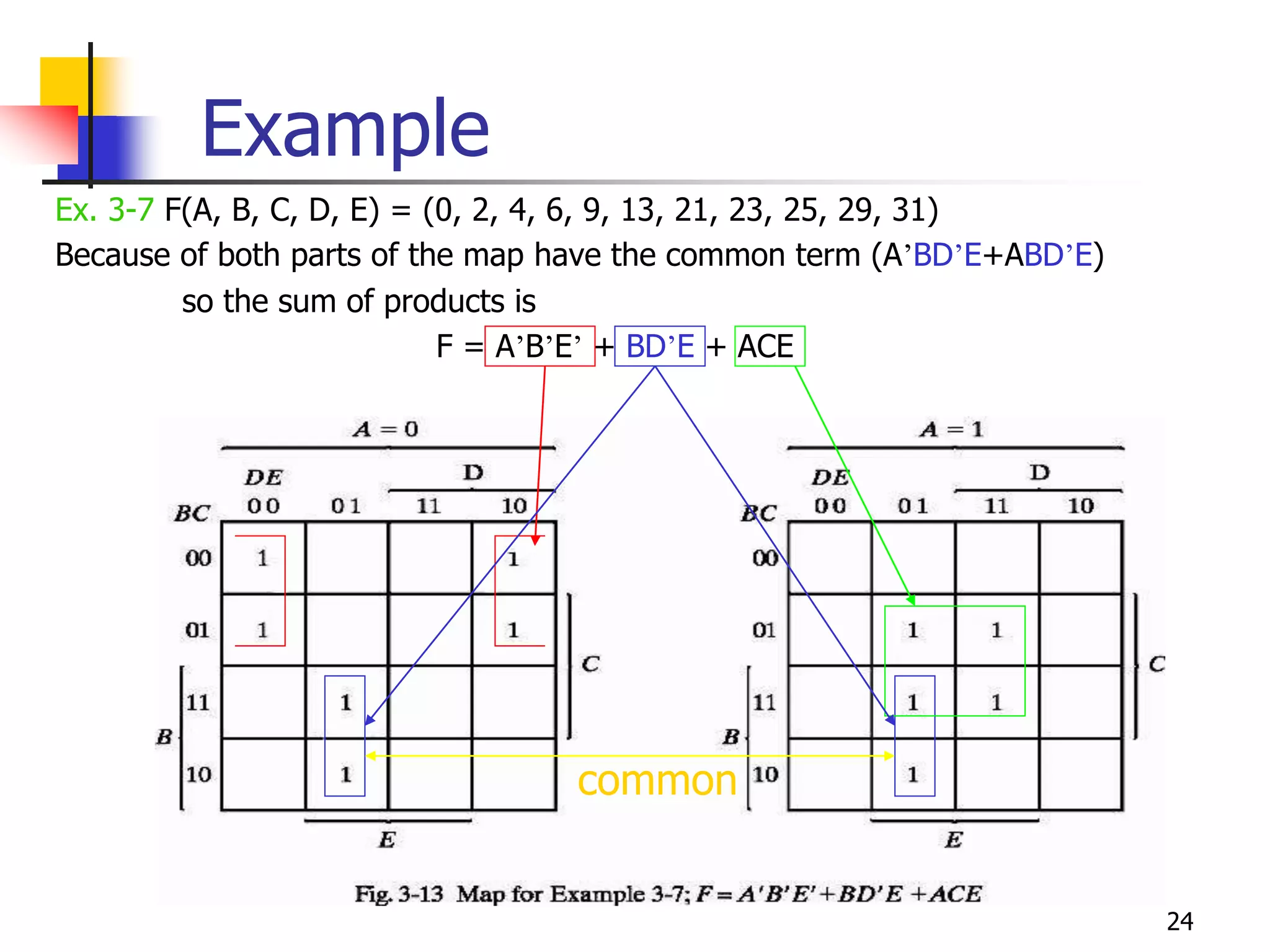

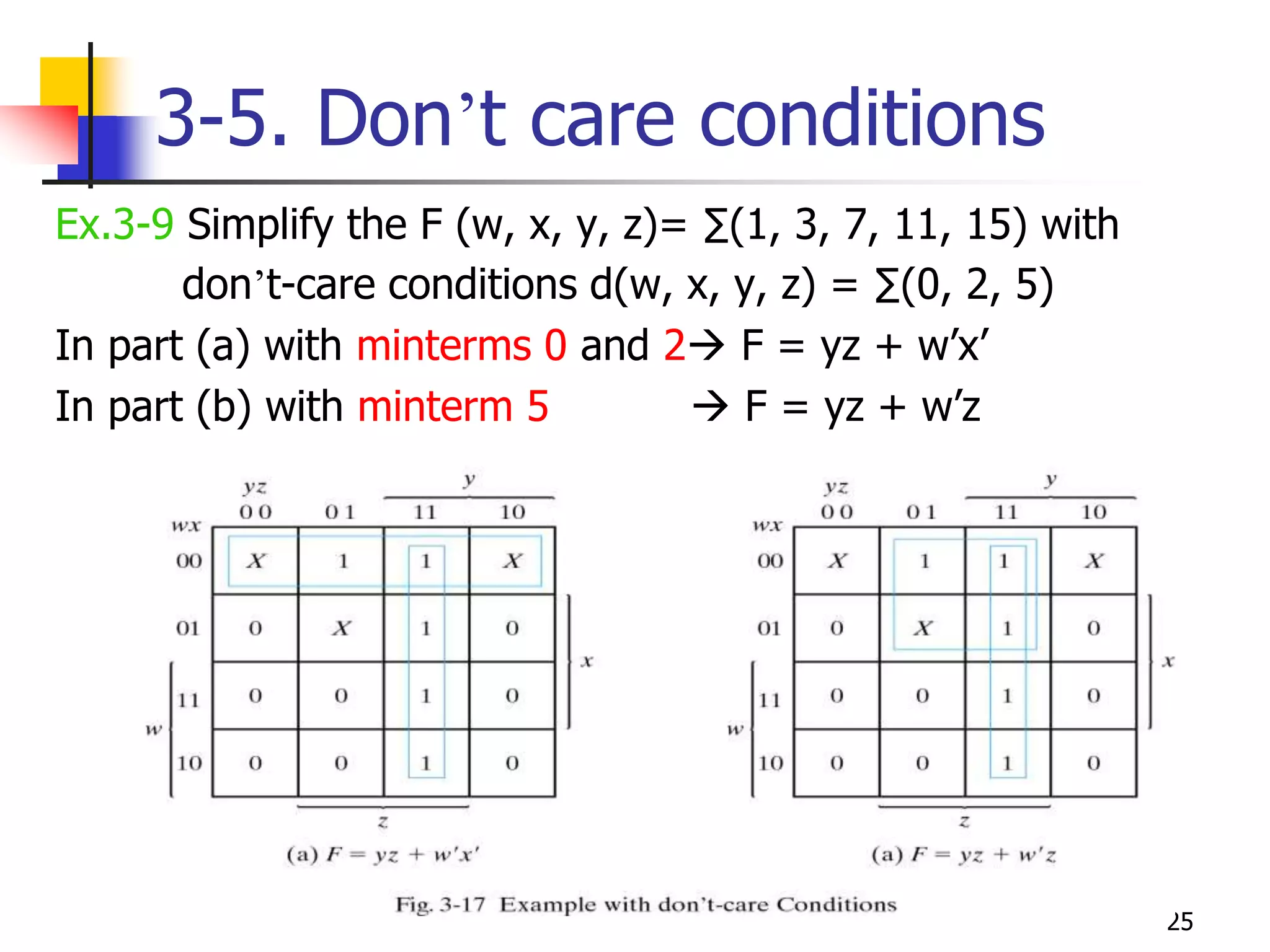

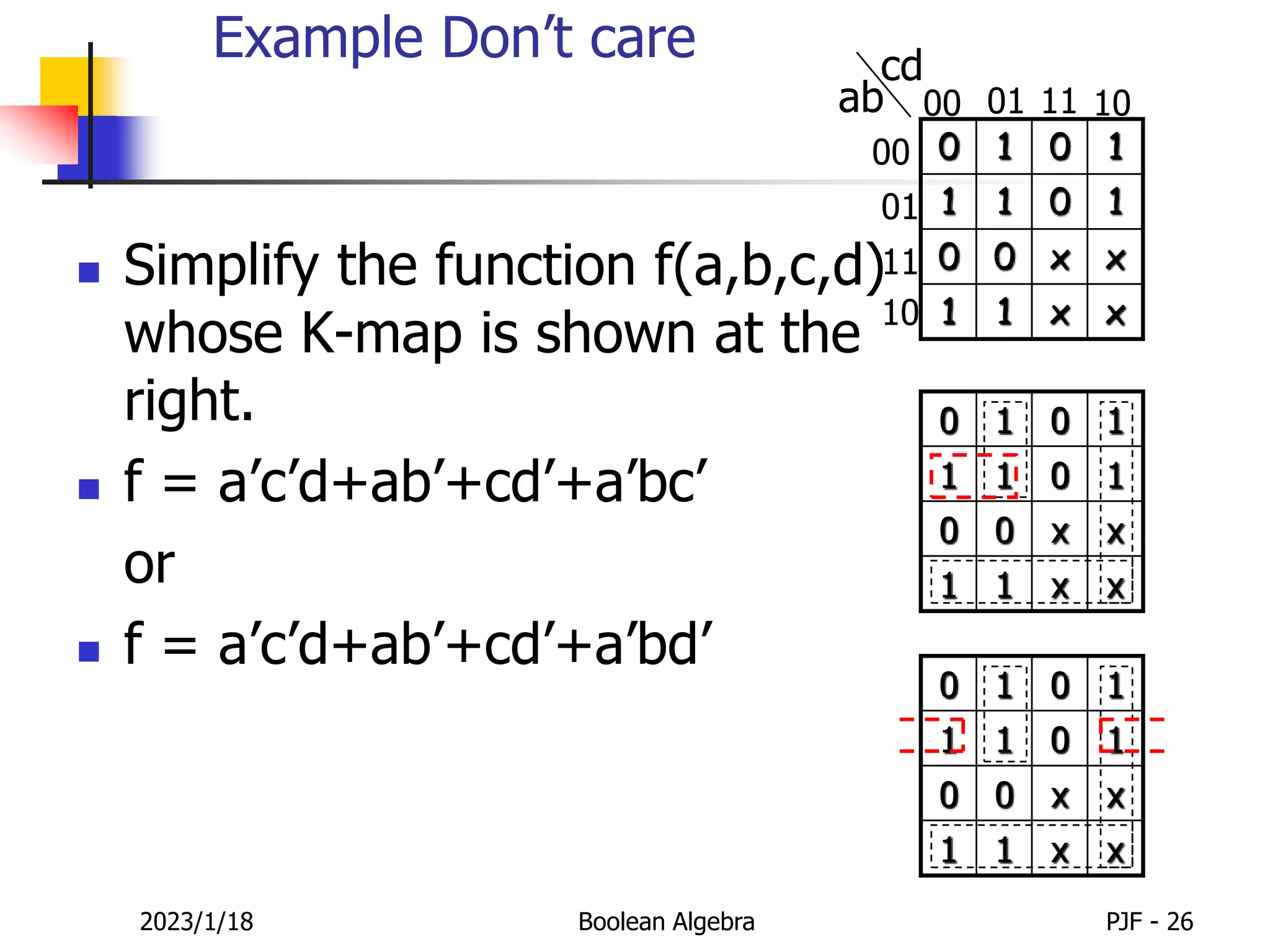

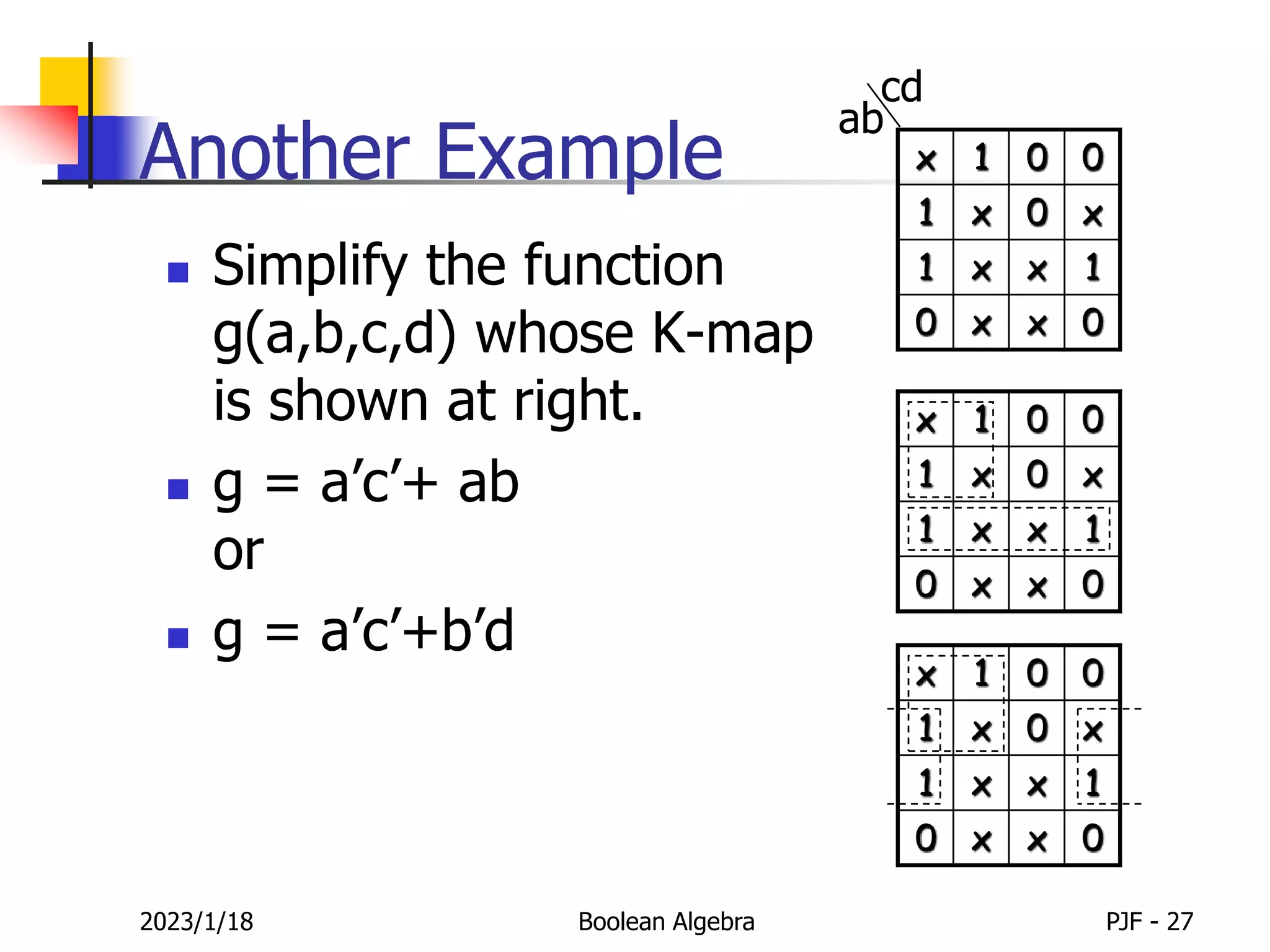

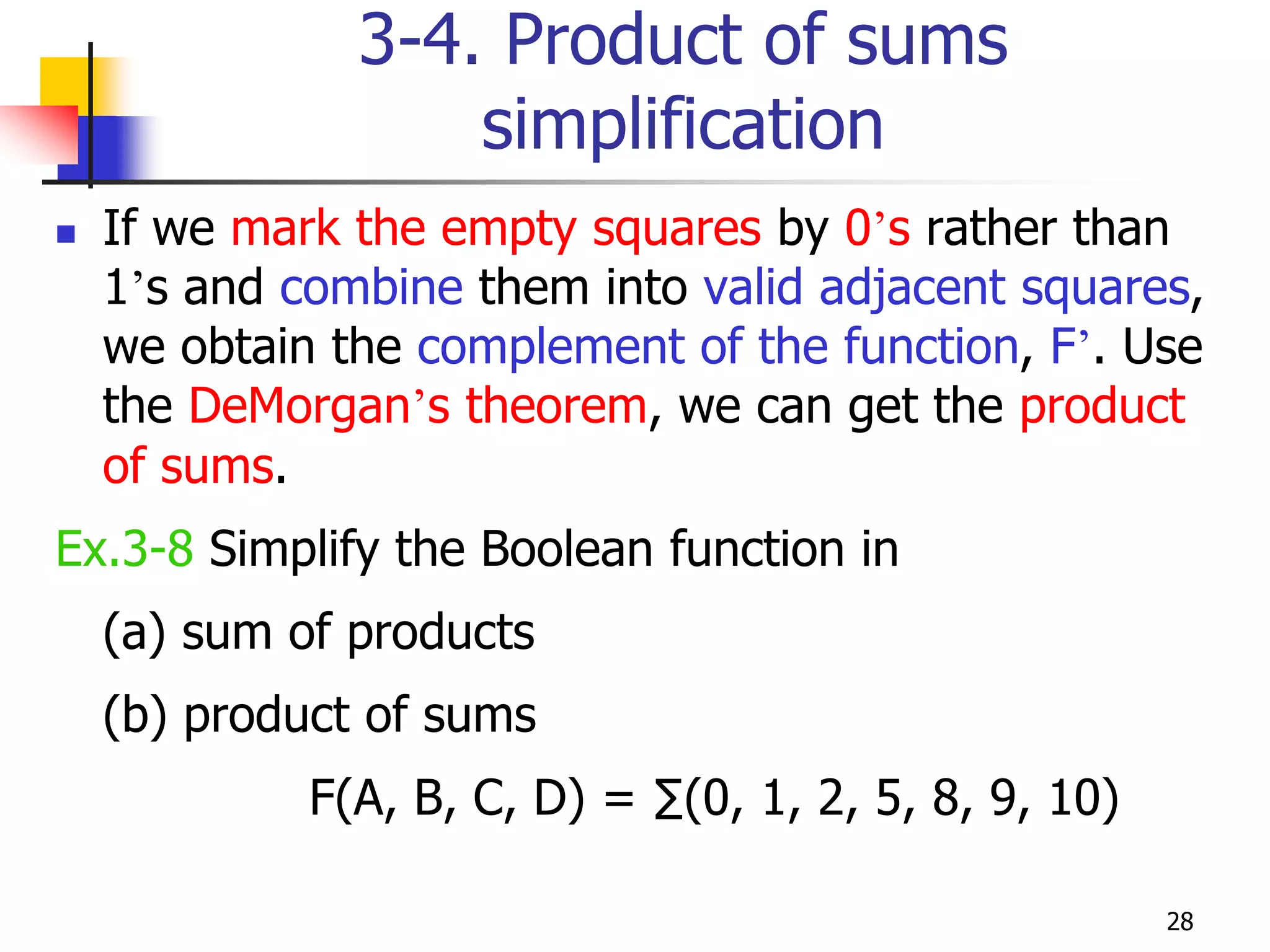

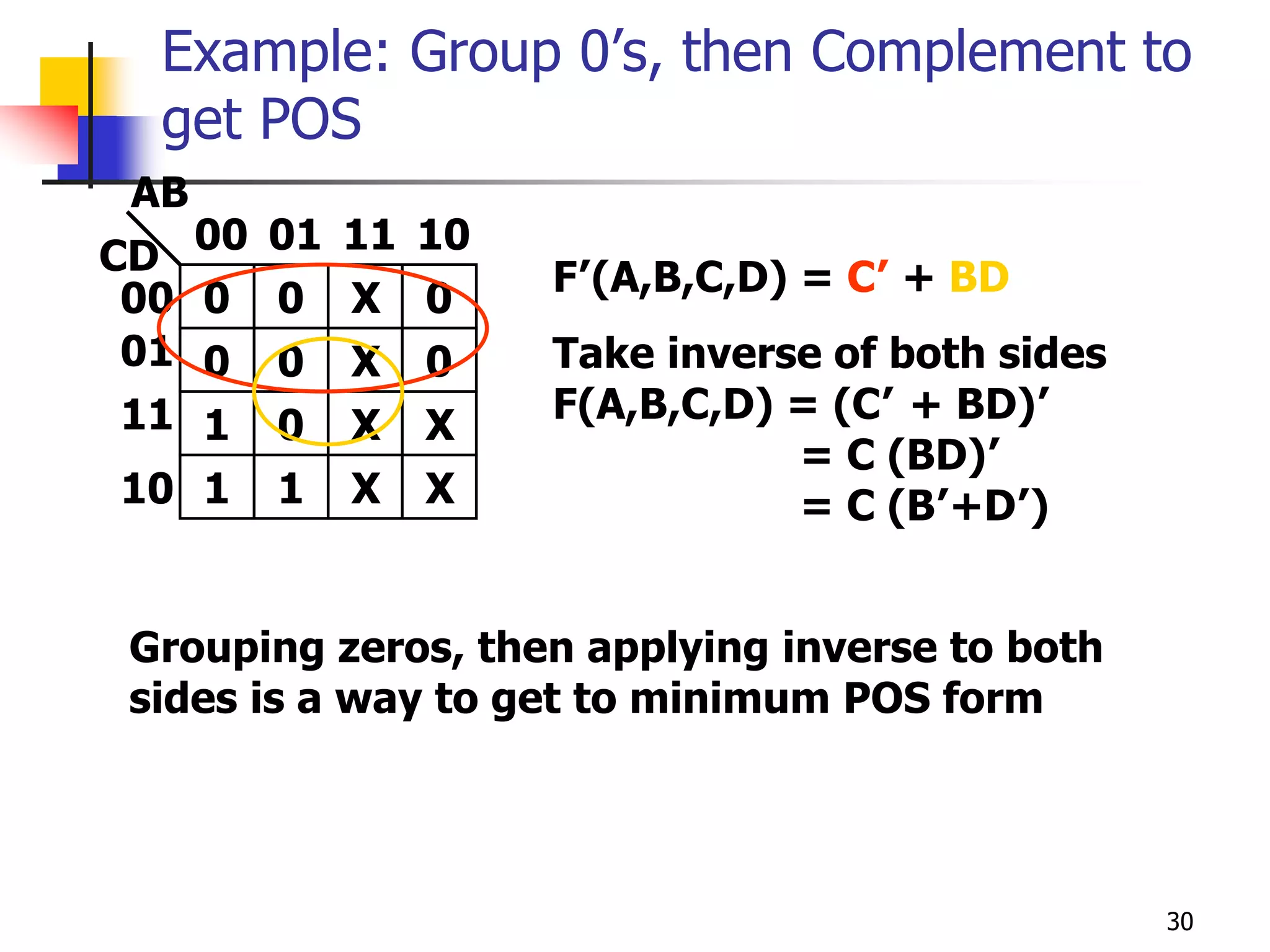

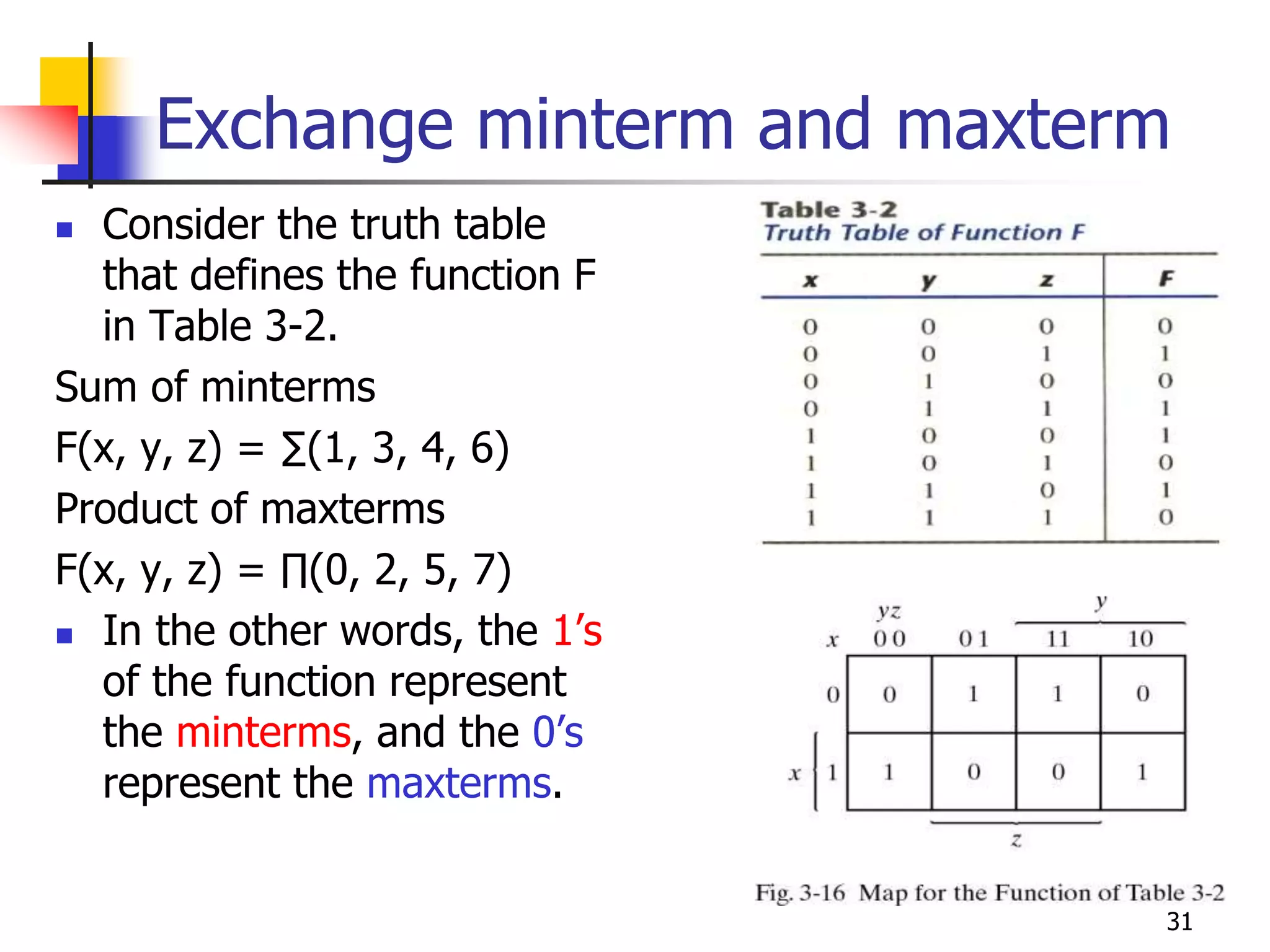

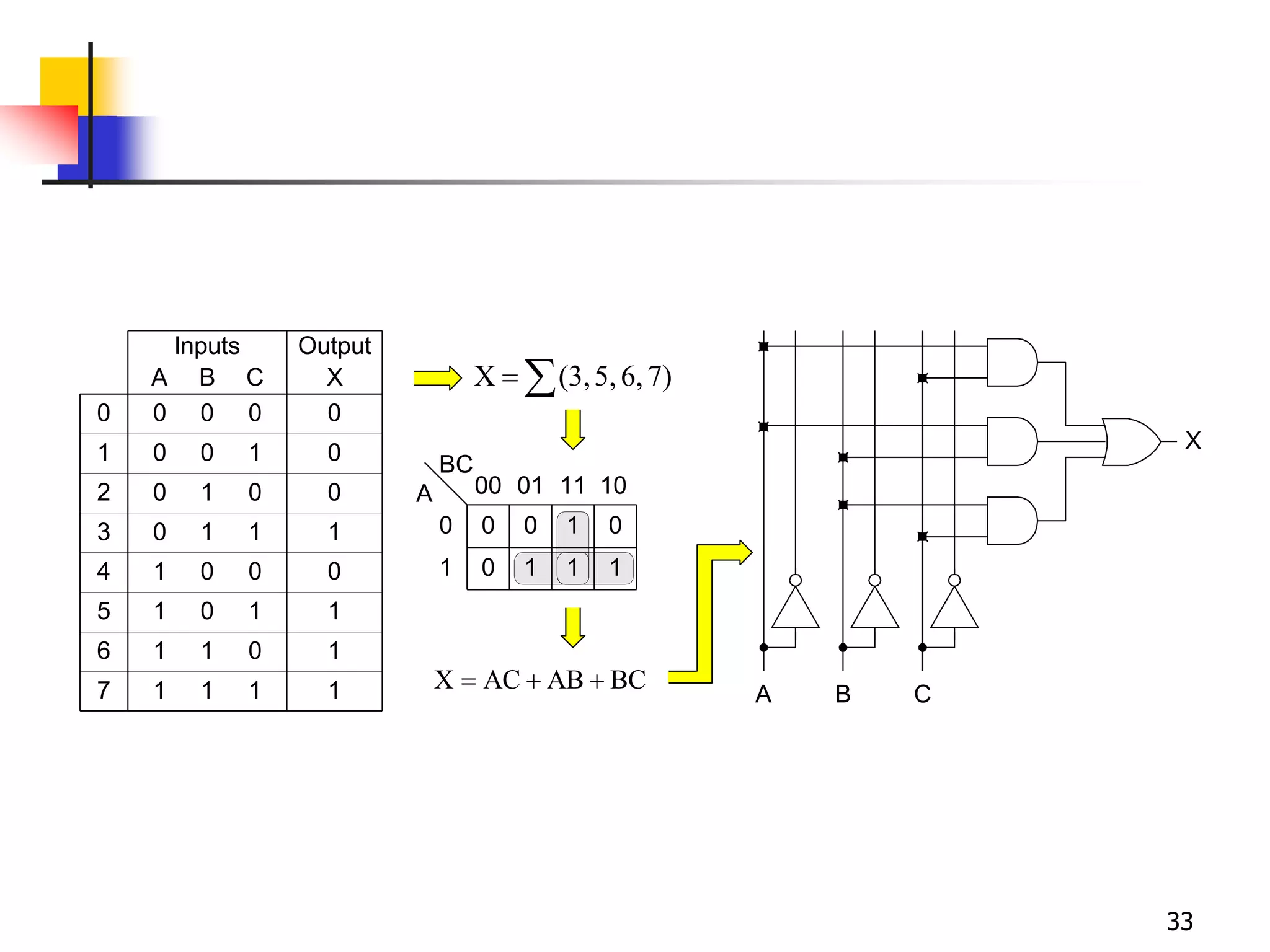

Karnaugh maps are a graphical method used to minimize logic functions. They arrange the minterms of a function in a grid based on the number of variables. Groupings of adjacent 1s in the map correspond to simplified logic terms. The largest possible groupings are used to find a minimum logic expression for the function. Don't cares can also be grouped and treated as 0s or 1s to further simplify expressions.