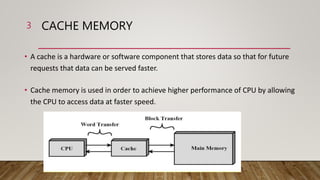

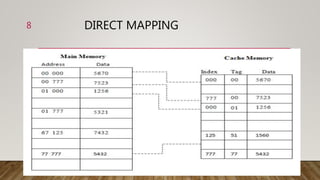

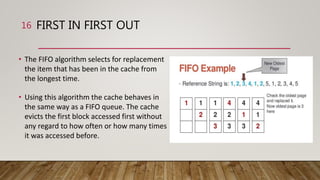

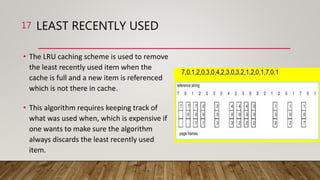

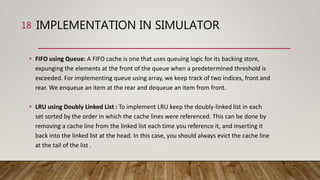

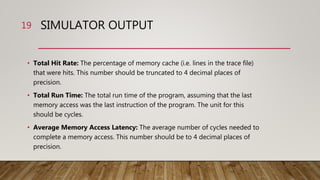

This document describes a cache simulator project. It discusses cache memory, types of cache including L1, L2 and L3 caches. It also describes cache mapping techniques like direct mapping, associative mapping, and set associative mapping. The document explains cache hits and misses. It covers write policies like write-back and write-through. Replacement algorithms like FIFO and LRU are also summarized. The cache simulator calculates metrics like hit rate, runtime, and memory access latency based on a memory access pattern file. It is implemented using data structures like queues for FIFO and doubly linked lists for LRU replacement.