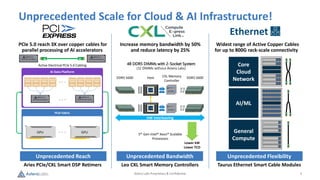

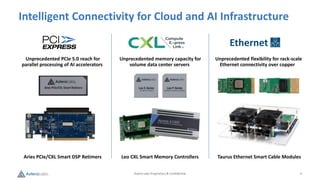

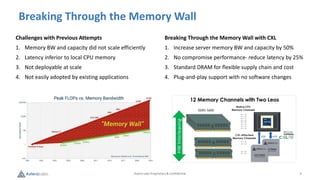

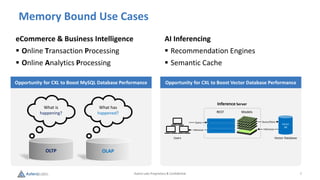

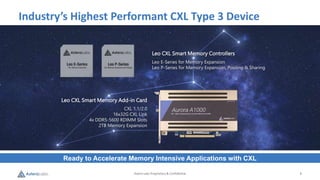

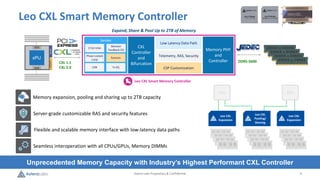

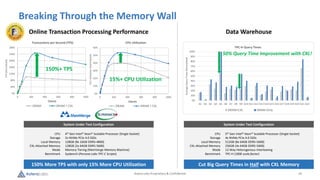

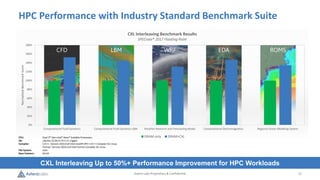

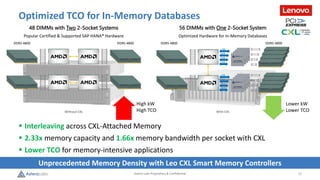

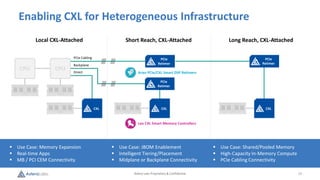

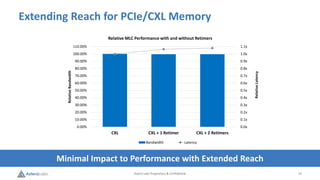

Astera Labs aims to enhance semiconductor connectivity solutions specifically for cloud and AI infrastructure, targeting significant improvements in memory bandwidth and latency. Their innovative technologies, including CXL smart memory controllers and active electrical cabling, facilitate unprecedented scalability and efficiency in data center applications. The document outlines various use cases, performance benchmarks, and the potential for transforming traditional data processing environments.

![Astera Labs Proprietary & Confidential 15

Calls to Action

Visit Check out how we smashed through

Memory

[OCP Map and where we are]

Learn More

www.asteralabs.com

CXL Resources

• Linux: https://pmem.io/ndctl/collab

• Interop:

https://www.asteralabs.com/interop

Ecosystem Alliance Contact:

• michael.ocampo@asteralabs.com

See the Demos at the

CXL Consortium & PCI-SIG Booths

Increase memory

bandwidth by 50% and

reduce latency by 25%

PCIe 5.0 reach 3X over

copper cables for parallel

processing of AI

accelerators](https://image.slidesharecdn.com/231113asteralabssc23cxlforumslides-231121003816-32919168/85/Astera-Labs-Intelligent-Connectivity-for-Cloud-and-AI-Infrastructure-15-320.jpg)