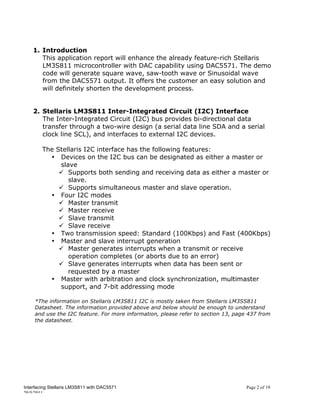

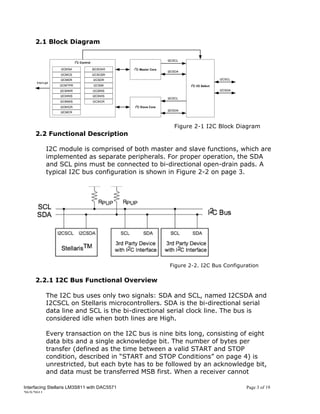

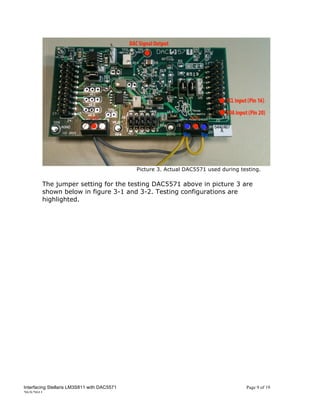

This document discusses interfacing the Stellaris LM3S811 microcontroller with the DAC5571 digital-to-analog converter over I2C. It provides an overview of the Stellaris I2C interface and how to establish communication with the DAC5571. Code examples are given to generate waveforms from the DAC5571 controlled by the Stellaris microcontroller over I2C.