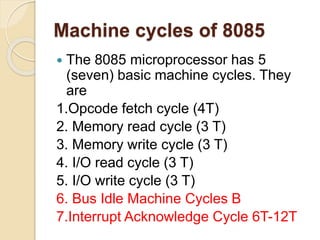

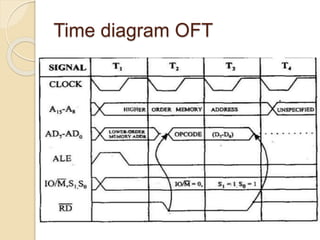

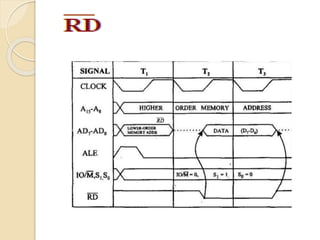

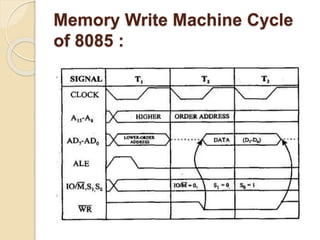

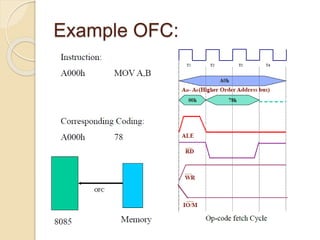

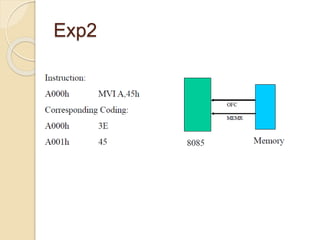

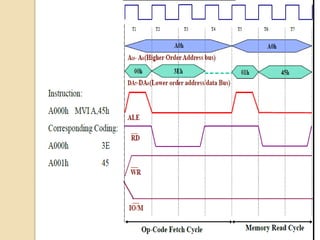

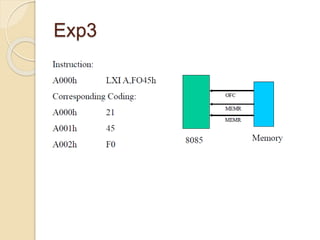

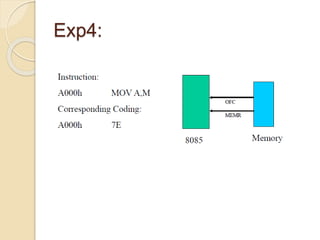

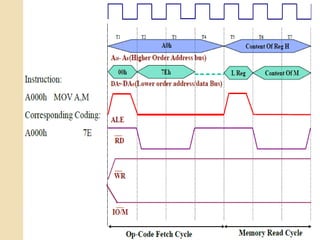

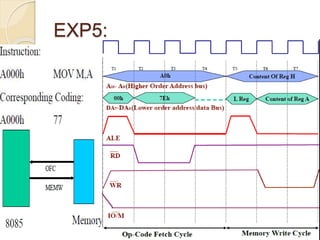

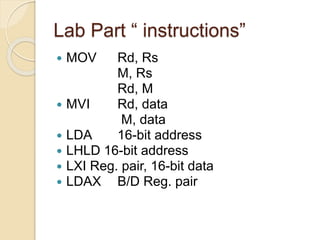

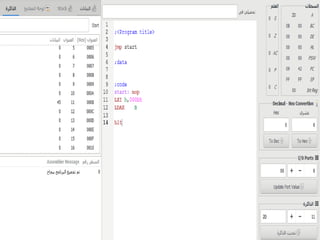

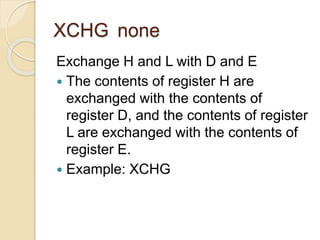

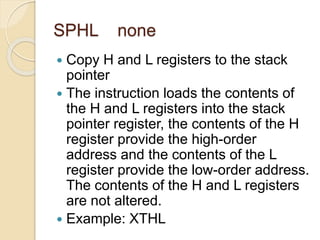

The document defines timing diagrams, machine cycles, and T-states. It then discusses the specific machine cycles of the 8085 microprocessor, including the opcode fetch cycle, memory read/write cycles, I/O read/write cycles, and interrupt acknowledge cycle. It provides examples of timing diagrams for various instructions like STA, INR, and discusses registers and instructions like STAX, MVI, LHLD.