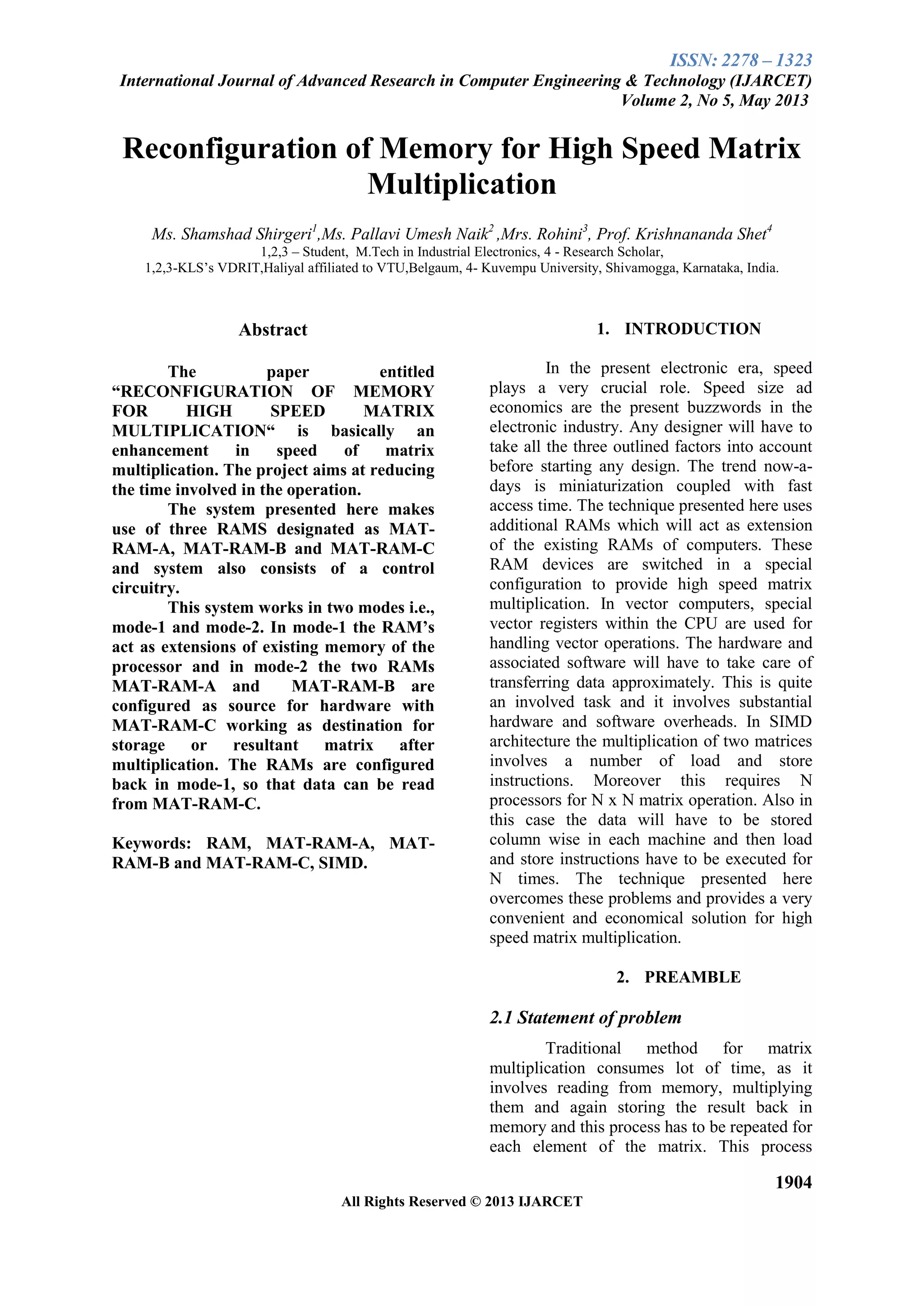

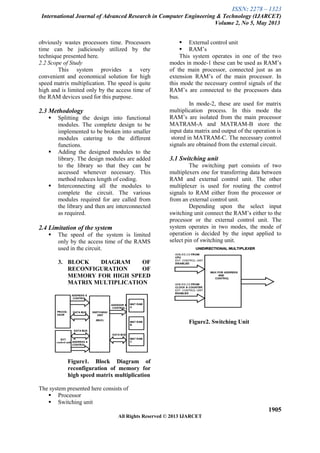

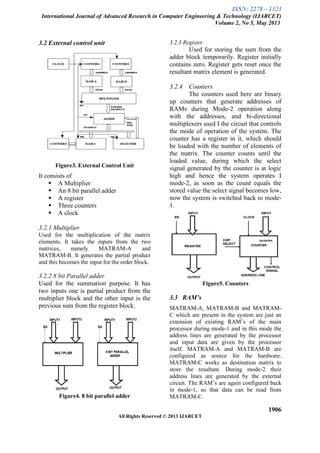

This document describes a system for reconfiguring memory to enable high-speed matrix multiplication. The system uses three RAMs (MAT-RAM-A, MAT-RAM-B, MAT-RAM-C) that can be configured in two modes: mode 1 where they act as extensions of the processor's memory, and mode 2 where MAT-RAM-A and MAT-RAM-B store input matrices and MAT-RAM-C stores the output matrix. In mode 2, an external control unit performs the multiplication and stores results directly in MAT-RAM-C, bypassing the processor to greatly increase speed compared to traditional methods. The RAMs are then switched back to mode 1 so results can be accessed normally.