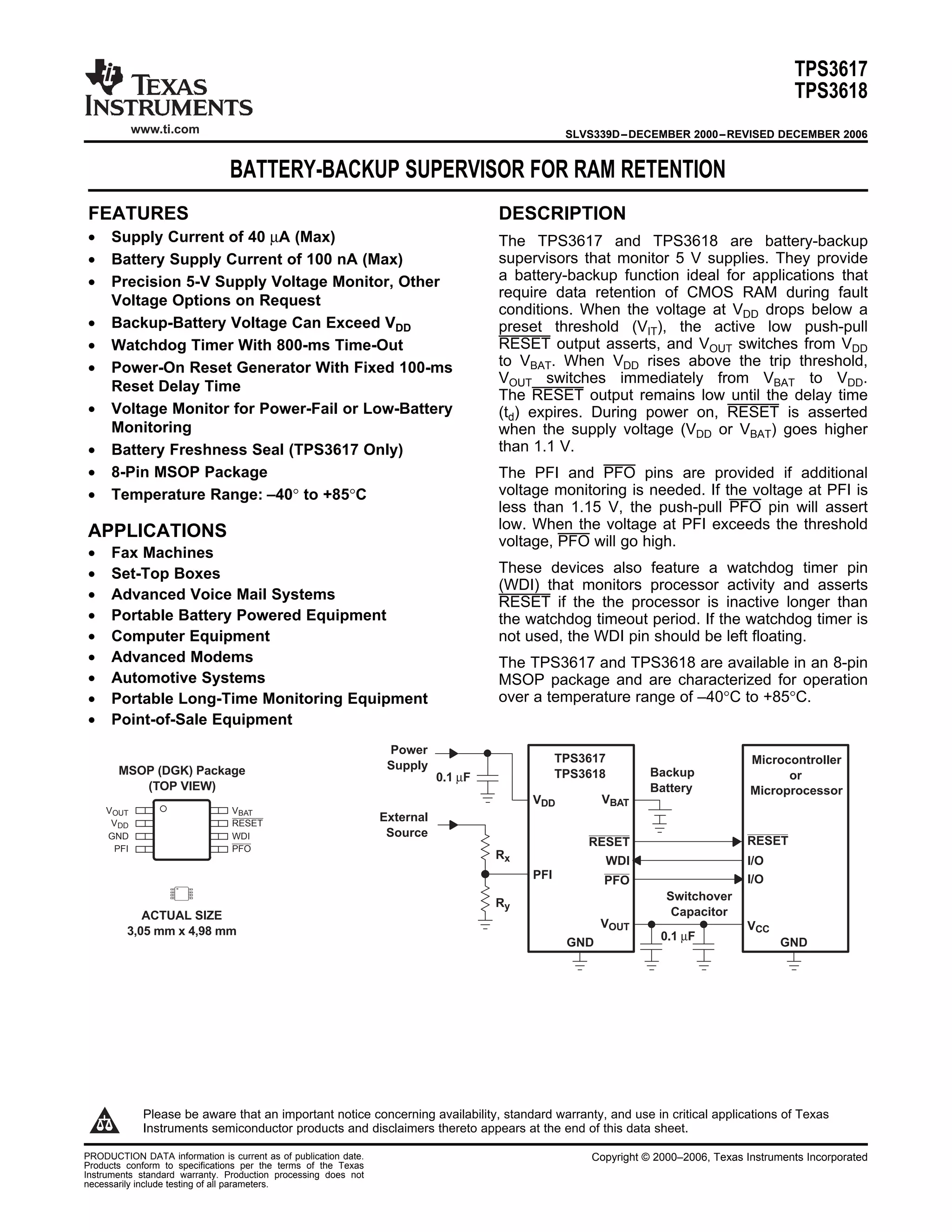

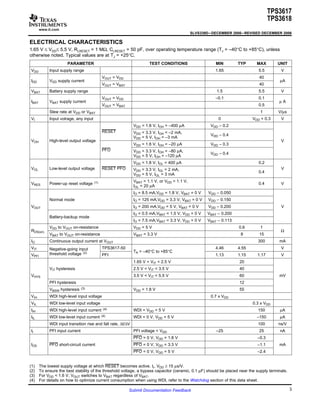

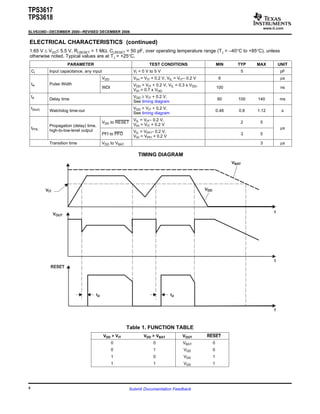

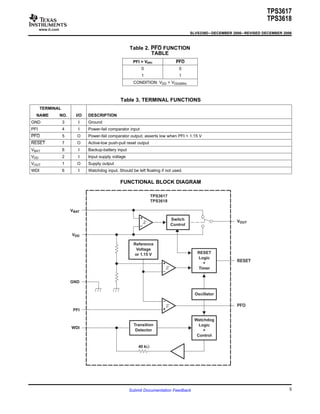

The document summarizes the TPS3617 and TPS3618 battery backup supervisors. The devices monitor a 5V supply and provide a battery backup function to retain RAM data during power faults. When the monitored voltage drops below a threshold, the output switches from the main supply to the backup battery. It also features a watchdog timer and power on reset. The devices are available in an 8-pin MSOP package and operate from -40°C to 85°C. Typical applications include set-top boxes, voice mail systems, portable equipment, and automotive systems.