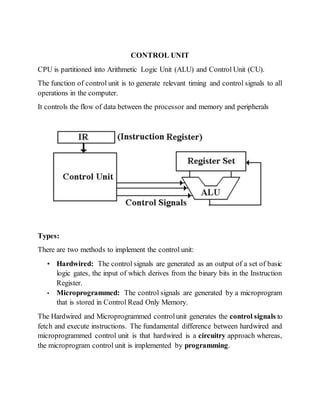

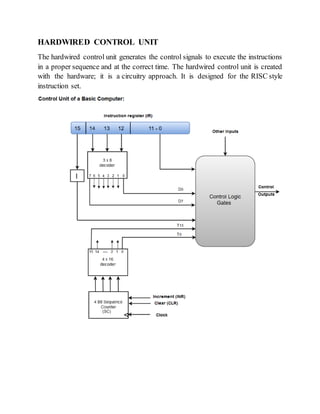

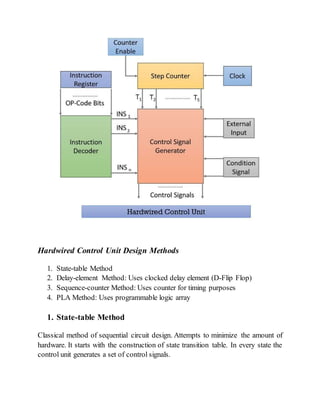

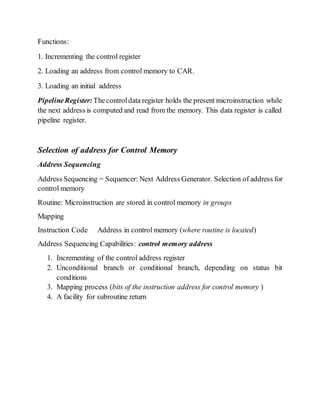

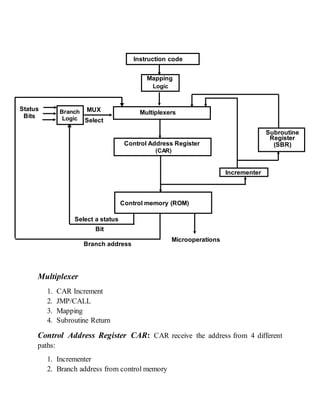

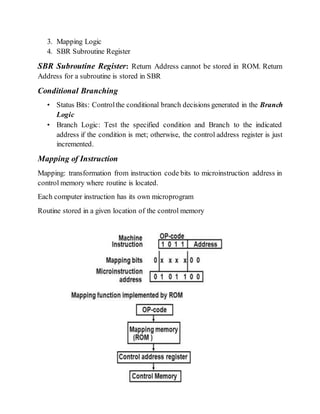

The document discusses control units in CPUs. There are two main methods for implementing control units: hardwired and microprogrammed. A hardwired control unit generates control signals through circuitry using logic gates, while a microprogrammed control unit generates control signals by executing a stored microprogram. Overall, hardwired control units are faster but less flexible, while microprogrammed control units are slower but more flexible and modifiable.