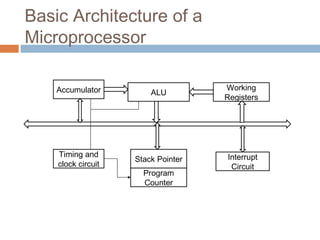

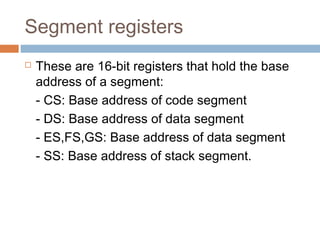

The document discusses the architecture and components of microprocessors, specifically the Intel 80386 microprocessor. It describes the basic components of a microprocessor including the ALU, registers, buses, and control unit. It then provides details on the architecture of the 80386 including its registers, operating modes, and signal types.