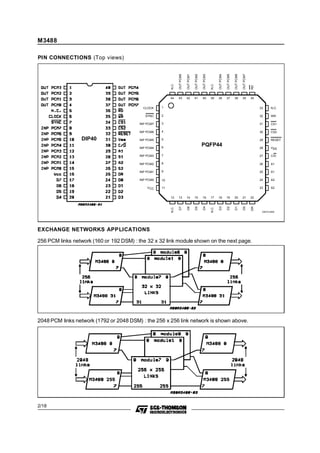

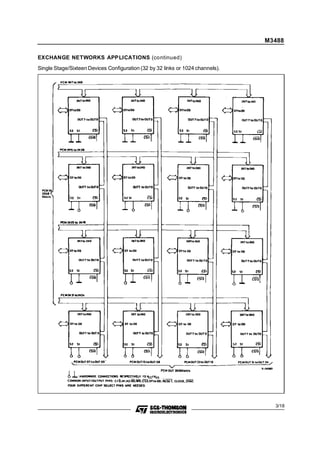

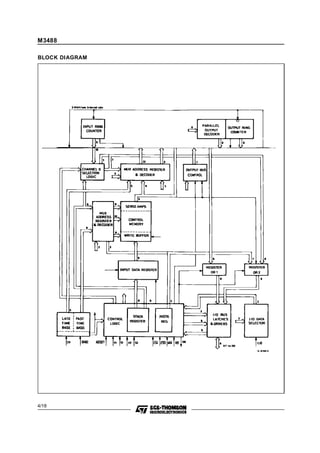

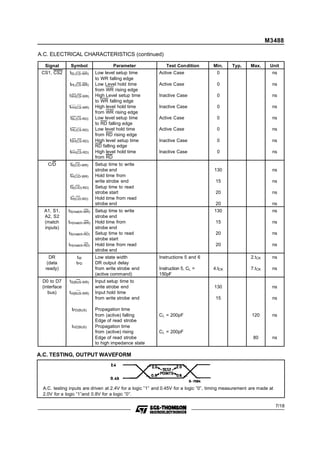

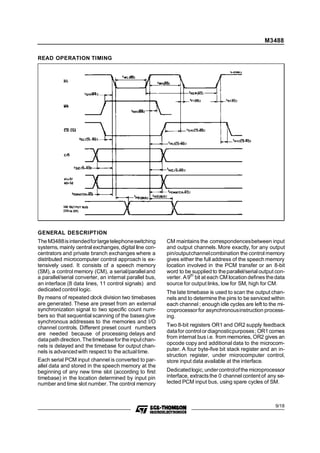

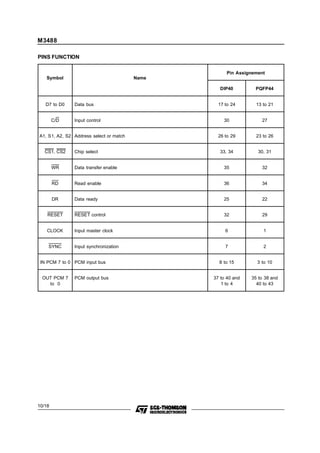

The document provides preliminary information on the M3488, a CMOS digital switching matrix designed for large capacity electronic exchanges with 256 input and output channels. It includes details on its compatibility with the PCM protocol, microprocessor interface capabilities, and maximum ratings. The device is intended for applications such as central exchanges and private branch exchanges, with specifications related to its electrical characteristics and pin configurations.