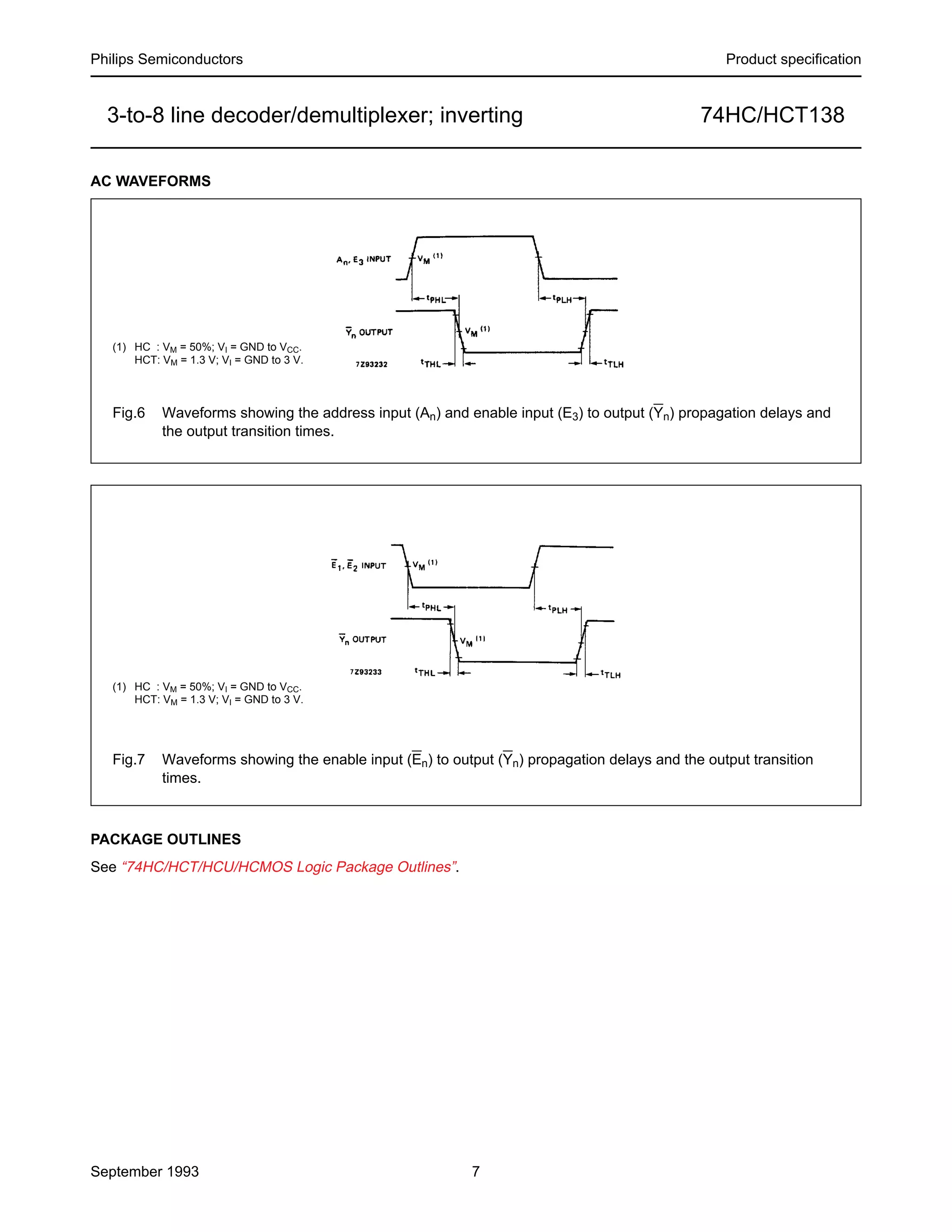

The document is a product specification for the 74HC/HCT138, a 3-to-8 line decoder/demultiplexer. It details the device's features, operational characteristics, pin configurations, and AC/DC specifications, emphasizing its compatibility with CMOS logic and its multiple enable functionality for easy expansion. The document also includes information on ordering, propagation delays, and package outlines.