Ieee 2015 16 vlsi @dreamweb techno solutions-trichy

•Download as DOCX, PDF•

0 likes•17 views

73/5,3rd Floor,Sri Kamatchi Complex Opp.City Hospital (Near Lakshmi Complex) Trichy- 620018, Contact No: 7200021403/04

Report

Share

Report

Share

Recommended

Selective Redundancy in Network-as-a-Service: Differentiated QoS in Multi-Ten...

Selective Redundancy in Network-as-a-Service: Differentiated QoS in Multi-Ten...Pradeeban Kathiravelu, Ph.D.

Recommended

Selective Redundancy in Network-as-a-Service: Differentiated QoS in Multi-Ten...

Selective Redundancy in Network-as-a-Service: Differentiated QoS in Multi-Ten...Pradeeban Kathiravelu, Ph.D.

Vlsi IEEE 2014 titles 2014_2015_CSE/IT/ECE/EEE/ STUDENTS IN CHENNAI (S3 INFO...

Vlsi IEEE 2014 titles 2014_2015_CSE/IT/ECE/EEE/ STUDENTS IN CHENNAI (S3 INFO...S3 Infotech IEEE Projects

More Related Content

What's hot

What's hot (9)

LXS Scanning presentation at the International Security Expo 2018

LXS Scanning presentation at the International Security Expo 2018

Digital Wave Formulation of Quasi-Static Partial Element Equivalent Circuit M...

Digital Wave Formulation of Quasi-Static Partial Element Equivalent Circuit M...

Ieee 2020 21 vlsi projects in pondicherry,ieee vlsi projects in chennai

Ieee 2020 21 vlsi projects in pondicherry,ieee vlsi projects in chennai

Similar to Ieee 2015 16 vlsi @dreamweb techno solutions-trichy

Vlsi IEEE 2014 titles 2014_2015_CSE/IT/ECE/EEE/ STUDENTS IN CHENNAI (S3 INFO...

Vlsi IEEE 2014 titles 2014_2015_CSE/IT/ECE/EEE/ STUDENTS IN CHENNAI (S3 INFO...S3 Infotech IEEE Projects

Similar to Ieee 2015 16 vlsi @dreamweb techno solutions-trichy (20)

Vlsi IEEE 2014 titles 2014_2015_CSE/IT/ECE/EEE/ STUDENTS IN CHENNAI (S3 INFO...

Vlsi IEEE 2014 titles 2014_2015_CSE/IT/ECE/EEE/ STUDENTS IN CHENNAI (S3 INFO...

Pantech vlsi [xilinx ise & spartan fpga] 2016-17![Pantech vlsi [xilinx ise & spartan fpga] 2016-17](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

![Pantech vlsi [xilinx ise & spartan fpga] 2016-17](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

Pantech vlsi [xilinx ise & spartan fpga] 2016-17

Pantech vlsi [xilinx ise & spartan fpga] 2016-17![Pantech vlsi [xilinx ise & spartan fpga] 2016-17](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

![Pantech vlsi [xilinx ise & spartan fpga] 2016-17](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

Pantech vlsi [xilinx ise & spartan fpga] 2016-17

2013 14-vlsi-project-titles-for-me-mtech-pantech-pro ed

2013 14-vlsi-project-titles-for-me-mtech-pantech-pro ed

2013 14-vlsi-project-titles-for-me-mtech-pantech-pro ed

2013 14-vlsi-project-titles-for-me-mtech-pantech-pro ed

VLSI Projects, IC Design, Low Power VLSI, Power Management, BIST, FPGA Projec...

VLSI Projects, IC Design, Low Power VLSI, Power Management, BIST, FPGA Projec...

Matlab IEEE 2015 2016 ieee project list (S3 Infotech-9884848198)

Matlab IEEE 2015 2016 ieee project list (S3 Infotech-9884848198)

VLSI ieee projects 2017-2018 | VLSI ieee projects Titles 2017-2018

VLSI ieee projects 2017-2018 | VLSI ieee projects Titles 2017-2018

More from subhu8430

More from subhu8430 (20)

Ieee 2015 16 vlsi @dreamweb techno solutions-trichy

Ieee 2015 16 vlsi @dreamweb techno solutions-trichy

Ieee 2015 16 ns2 @dreamweb techno solutions-trichy

Ieee 2015 16 ns2 @dreamweb techno solutions-trichy

Ieee 2015 16 matlab @dreamweb techno solutions-trichy

Ieee 2015 16 matlab @dreamweb techno solutions-trichy

Ieee 2015 16 embedded titles @dreamweb techno solutions-trichy

Ieee 2015 16 embedded titles @dreamweb techno solutions-trichy

Ieee 2015 16 java titles @dreamweb techno solutions-trichy

Ieee 2015 16 java titles @dreamweb techno solutions-trichy

Ieee 2015 16 vlsi @dreamweb techno solutions-trichy

Ieee 2015 16 vlsi @dreamweb techno solutions-trichy

Ieee 2015 16 ns2 @dreamweb techno solutions-trichy

Ieee 2015 16 ns2 @dreamweb techno solutions-trichy

Ieee 2015 16 matlab @dreamweb techno solutions-trichy

Ieee 2015 16 matlab @dreamweb techno solutions-trichy

Ieee 2015 16 embedded titles @dreamweb techno solutions-trichy

Ieee 2015 16 embedded titles @dreamweb techno solutions-trichy

Ieee 2015 16 java titles @dreamweb techno solutions-trichy

Ieee 2015 16 java titles @dreamweb techno solutions-trichy

Ieee 2015 16 vlsi @dreamweb techno solutions-trichy

Ieee 2015 16 vlsi @dreamweb techno solutions-trichy

Ieee 2015 16 ns2 @dreamweb techno solutions-trichy

Ieee 2015 16 ns2 @dreamweb techno solutions-trichy

Ieee 2015 16 matlab @dreamweb techno solutions-trichy

Ieee 2015 16 matlab @dreamweb techno solutions-trichy

Ieee 2015 16 embedded titles @dreamweb techno solutions-trichy

Ieee 2015 16 embedded titles @dreamweb techno solutions-trichy

Ieee 2015 16 java titles @dreamweb techno solutions-trichy

Ieee 2015 16 java titles @dreamweb techno solutions-trichy

Ieee 2015 16 vlsi @dreamweb techno solutions-trichy

Ieee 2015 16 vlsi @dreamweb techno solutions-trichy

Recently uploaded

★ CALL US 9953330565 ( HOT Young Call Girls In Badarpur delhi NCR

★ CALL US 9953330565 ( HOT Young Call Girls In Badarpur delhi NCR9953056974 Low Rate Call Girls In Saket, Delhi NCR

College Call Girls Nashik Nehal 7001305949 Independent Escort Service Nashik

College Call Girls Nashik Nehal 7001305949 Independent Escort Service NashikCall Girls in Nagpur High Profile

9953056974 Call Girls In South Ex, Escorts (Delhi) NCR.pdf

9953056974 Call Girls In South Ex, Escorts (Delhi) NCR.pdf9953056974 Low Rate Call Girls In Saket, Delhi NCR

Call Girls in Nagpur Suman Call 7001035870 Meet With Nagpur Escorts

Call Girls in Nagpur Suman Call 7001035870 Meet With Nagpur EscortsCall Girls in Nagpur High Profile

Recently uploaded (20)

Roadmap to Membership of RICS - Pathways and Routes

Roadmap to Membership of RICS - Pathways and Routes

★ CALL US 9953330565 ( HOT Young Call Girls In Badarpur delhi NCR

★ CALL US 9953330565 ( HOT Young Call Girls In Badarpur delhi NCR

Model Call Girl in Narela Delhi reach out to us at 🔝8264348440🔝

Model Call Girl in Narela Delhi reach out to us at 🔝8264348440🔝

Gfe Mayur Vihar Call Girls Service WhatsApp -> 9999965857 Available 24x7 ^ De...

Gfe Mayur Vihar Call Girls Service WhatsApp -> 9999965857 Available 24x7 ^ De...

College Call Girls Nashik Nehal 7001305949 Independent Escort Service Nashik

College Call Girls Nashik Nehal 7001305949 Independent Escort Service Nashik

9953056974 Call Girls In South Ex, Escorts (Delhi) NCR.pdf

9953056974 Call Girls In South Ex, Escorts (Delhi) NCR.pdf

(ANVI) Koregaon Park Call Girls Just Call 7001035870 [ Cash on Delivery ] Pun...![(ANVI) Koregaon Park Call Girls Just Call 7001035870 [ Cash on Delivery ] Pun...](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

![(ANVI) Koregaon Park Call Girls Just Call 7001035870 [ Cash on Delivery ] Pun...](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

(ANVI) Koregaon Park Call Girls Just Call 7001035870 [ Cash on Delivery ] Pun...

(PRIYA) Rajgurunagar Call Girls Just Call 7001035870 [ Cash on Delivery ] Pun...![(PRIYA) Rajgurunagar Call Girls Just Call 7001035870 [ Cash on Delivery ] Pun...](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

![(PRIYA) Rajgurunagar Call Girls Just Call 7001035870 [ Cash on Delivery ] Pun...](data:image/gif;base64,R0lGODlhAQABAIAAAAAAAP///yH5BAEAAAAALAAAAAABAAEAAAIBRAA7)

(PRIYA) Rajgurunagar Call Girls Just Call 7001035870 [ Cash on Delivery ] Pun...

Sheet Pile Wall Design and Construction: A Practical Guide for Civil Engineer...

Sheet Pile Wall Design and Construction: A Practical Guide for Civil Engineer...

Processing & Properties of Floor and Wall Tiles.pptx

Processing & Properties of Floor and Wall Tiles.pptx

Call Girls in Nagpur Suman Call 7001035870 Meet With Nagpur Escorts

Call Girls in Nagpur Suman Call 7001035870 Meet With Nagpur Escorts

HARDNESS, FRACTURE TOUGHNESS AND STRENGTH OF CERAMICS

HARDNESS, FRACTURE TOUGHNESS AND STRENGTH OF CERAMICS

Decoding Kotlin - Your guide to solving the mysterious in Kotlin.pptx

Decoding Kotlin - Your guide to solving the mysterious in Kotlin.pptx

Ieee 2015 16 vlsi @dreamweb techno solutions-trichy

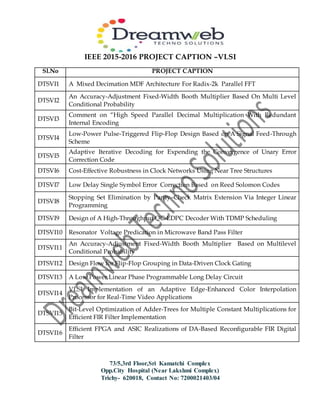

- 1. IEEE 2015-2016 PROJECT CAPTION –VLSI 73/5,3rd Floor,Sri Kamatchi Complex Opp.City Hospital (Near Lakshmi Complex) Trichy- 620018, Contact No: 7200021403/04 Sl.No PROJECT CAPTION DTSVI1 A Mixed Decimation MDF Architecture For Radix-2k Parallel FFT DTSVI2 An Accuracy-Adjustment Fixed-Width Booth Multiplier Based On Multi Level Conditional Probability DTSVI3 Comment on “High Speed Parallel Decimal Multiplication With Redundant Internal Encoding DTSVI4 Low-Power Pulse-Triggered Flip-Flop Design Based on A Signal Feed-Through Scheme DTSVI5 Adaptive Iterative Decoding for Expending the Convergence of Unary Error Correction Code DTSVI6 Cost-Effective Robustness in Clock Networks Using Near Tree Structures DTSVI7 Low Delay Single Symbol Error Correction Based on Reed Solomon Codes DTSVI8 Stopping Set Elimination by Parity–Check Matrix Extension Via Integer Linear Programming DTSVI9 Design of A High-Throughput QC-LDPC Decoder With TDMP Scheduling DTSVI10 Resonator Voltage Predication in Microwave Band Pass Filter DTSVI11 An Accuracy-Adjustment Fixed-Width Booth Multiplier Based on Multilevel Conditional Probability DTSVI12 Design Flow for Flip-Flop Grouping in Data-Driven Clock Gating DTSVI13 A Low Power Linear Phase Programmable Long Delay Circuit DTSVI14 VLSI Implementation of an Adaptive Edge-Enhanced Color Interpolation Processor for Real-Time Video Applications DTSVI15 Bit-Level Optimization of Adder-Trees for Multiple Constant Multiplications for Efficient FIR Filter Implementation DTSVI16 Efficient FPGA and ASIC Realizations of DA-Based Reconfigurable FIR Digital Filter

- 2. IEEE 2015-2016 PROJECT CAPTION –VLSI 73/5,3rd Floor,Sri Kamatchi Complex Opp.City Hospital (Near Lakshmi Complex) Trichy- 620018, Contact No: 7200021403/04 DTSVI17 An Efficient VLSI Architecture of A Reconfigurable Pulse-Shaping FIR Interpolation Filter for Multi Standard DUC DTSVI18 Low Power FSK Receiver Using an Oscillator-Based Injection-Locked Frequency Divider DTSVI19 Low-Power High-Throughput LDPC Decoder Using Non-Refresh Embedded DRAM DTSVI20 SIFT Hardware Implementation for Real-Time Image Features Extraction DTSVI21 An Efficient Denoising Architecture for Removal of Impulse Noise in Image DTSVI22 Modeling, Control and Implementation of DC-DC Converter for Variable Frequency Operation DTSVI23 An FPGA-Based Fully Synchronized Design of a bilateral Filter for Real-Time Image Denoising DTSVI24 Modified Gradient Search for Level Set Based Image Segmentation FPGA Implementation of Pipelined Architecture for SPIHT Algorithm DTSVI25 Shadow Removal for Background Subtraction Using Illumination Invariant Measures DTSVI26 Segmentation and Location of Abnormality in Brain MR Images Using Distributed Estimation DTSVI27 Background Subtraction Based on Threshold Detection Using Modified K-Means Algorithm DTSVI28 16 Bit Microprocessors Design and Simulation in VHDL DTSVI29 Real Time Background Generation and Foreground Object Segmentation for High Definition Color Video Stream in FPGA Device DTSVI30 VLSI Implementation of A Low-Cost High Quality Image Scaling Processor