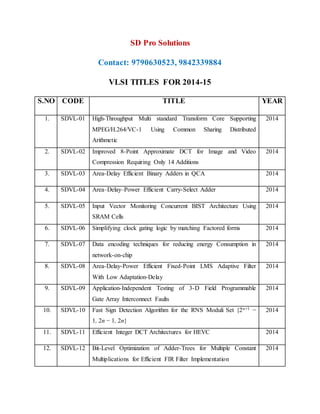

Vlsi titles for 2014 15

- 1. SD Pro Solutions Contact: 9790630523, 9842339884 VLSI TITLES FOR 2014-15 S.NO CODE TITLE YEAR 1. SDVL-01 High-Throughput Multi standard Transform Core Supporting MPEG/H.264/VC-1 Using Common Sharing Distributed Arithmetic 2014 2. SDVL-02 Improved 8-Point Approximate DCT for Image and Video Compression Requiring Only 14 Additions 2014 3. SDVL-03 Area-Delay Efficient Binary Adders in QCA 2014 4. SDVL-04 Area–Delay–Power Efficient Carry-Select Adder 2014 5. SDVL-05 Input Vector Monitoring Concurrent BIST Architecture Using SRAM Cells 2014 6. SDVL-06 Simplifying clock gating logic by matching Factored forms 2014 7. SDVL-07 Data encoding techniques for reducing energy Consumption in network-on-chip 2014 8. SDVL-08 Area-Delay-Power Efficient Fixed-Point LMS Adaptive Filter With Low Adaptation-Delay 2014 9. SDVL-09 Application-Independent Testing of 3-D Field Programmable Gate Array Interconnect Faults 2014 10. SDVL-10 Fast Sign Detection Algorithm for the RNS Moduli Set {2n+1 − 1, 2n − 1, 2n} 2014 11. SDVL-11 Efficient Integer DCT Architectures for HEVC 2014 12. SDVL-12 Bit-Level Optimization of Adder-Trees for Multiple Constant Multiplications for Efficient FIR Filter Implementation 2014

- 2. 13. SDVL-13 Design of Efficient Binary Comparators in Quantum-Dot Cellular Automata 2014 14. SDVL-14 Reverse Converter Design via Parallel-Prefix Adders: Novel Components, Methodology, and Implementations 2014 15. SDVL-15 Low-Complexity Low-Latency Architecture for Matching of Data Encoded With Hard Systematic Error-Correcting Codes 2014 16. SDVL-16 Multifunction Residue Architectures for Cryptography 2014 17. SDVL-17 Defense Against Primary User Emulation Attacks in Cognitive Radio Networks Using Advanced Encryption Standard 2014 18. SDVL-18 Aging-Aware Reliable Multiplier Design With Adaptive Hold Logic 2014 19. SDVL-19 Critical-Path Analysis and Low-Complexity Implementation of the LMS Adaptive Algorithm 2014 20. SDVL-20 Eliminating Synchronization Latency Using Sequenced Latching 2014 21. SDVL-21 Precise VLSI Architecture for AI Based 1-D/ 2-D Daub-6 Wavelet Filter Banks With Low Adder-Count 2014 22. SDVL-22 Gate Mapping Automation for Asynchronous NULL Convention Logic Circuits 2014 23. SDVL-23 Efficient FPGA and ASIC Realizations of DA-Based Reconfigurable FIR Digital Filter 2014 24. SDVL-24 Non binary LDPC Decoder Based on Simplified Enhanced Generalized Bit-Flipping Algorithm 2014 25. SDVL-25 Efficient Algorithm and Architecture for Elliptic Curve Cryptography for Extremely Constrained Secure Applications 2014 26. SDVL-26 An Optimized Modified Booth Recoder for Efficient Design of the Add-Multiply Operator 2014 27. SDVL-27 Efficie nt VLSI Implementation of Neural Networks With Hyperbolic Tangent Activation Function 2014 28. SDVL-28 Design of Digit-Serial FIR Filters: Algorithms, Architectures, 2013

- 3. and a CAD Tool 29. SDVL-29 Parallel AES Encryption Engines for Many-Core Processor Arrays 2013 30. SDVL-30 Design of Testable Reversible Sequential Circuits 2013 31. SDVL-31 Test Patterns of Multiple SIC Vectors: Theory and Application in BIST Schemes 2013 32. SDVL-32 A Novel Modulo Adder for 2n-2k- 1Residue Number System 2013 33. SDVL-33 Improvement of the Security of ZigBee by a New Chaotic Algorithm 2013 34. SDVL-34 CORDIC Based Fast Radix-2 DCT Algorithm 2013 35. SDVL-35 Split Radix Algorithm for Length 6mDFT 2013 36. SDVL-36 Low-Complexity Multiplier for GF(2m) Based on All-One Polynomials 2013 37. SDVL-37 Low-Power, High-Throughput, and Low-Area Adaptive FIR Filter Based on Distributed Arithmetic 2013 38. SDVL-38 Multicarrier Systems Based on Multistage Layered IFFT Structure 2013 39. SDVL-39 Design of an Error Detection and Data Recovery Architecture for Motion Estimation Testing Applications 2012 40. SDVL-40 Period Extension and Randomness Enhancement Using High- Throughput Reseeding-Mixing PRNG 2012 41. SDVL-41 Area-Efficient Parallel FIR Digital Filter Structures for Symmetric Convolutions Based on Fast FIR Algorithm 2012 42. SDVL-42 Measurement and Evaluation of Power Analysis Attacks on Asynchronous S-Box 2012 43. SDVL-43 Low-Power and Area-Efficient Carry Select Adder 2012 44. SDVL-44 A Low-Power Single-Phase Clock Multiband Flexible Divider 2012 Contact: 9790630523, 9842339884