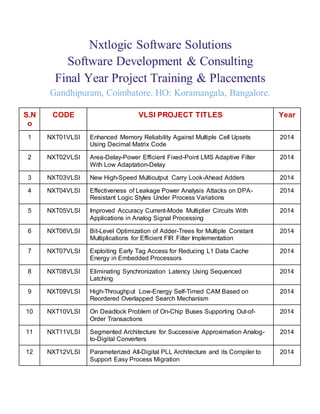

Vlsi ieee 2014 project titles

- 1. Nxtlogic Software Solutions Software Development & Consulting Final Year Project Training & Placements Gandhipuram, Coimbatore. HO: Koramangala, Bangalore. S.N o CODE VLSI PROJECT TITLES Year 1 NXT01VLSI Enhanced Memory Reliability Against Multiple Cell Upsets Using Decimal Matrix Code 2014 2 NXT02VLSI Area-Delay-Power Efficient Fixed-Point LMS Adaptive Filter With Low Adaptation-Delay 2014 3 NXT03VLSI New High-Speed Multioutput Carry Look-Ahead Adders 2014 4 NXT04VLSI Effectiveness of Leakage Power Analysis Attacks on DPA-Resistant Logic Styles Under Process Variations 2014 5 NXT05VLSI Improved Accuracy Current-Mode Multiplier Circuits With Applications in Analog Signal Processing 2014 6 NXT06VLSI Bit-Level Optimization of Adder-Trees for Multiple Constant Multiplications for Efficient FIR Filter Implementation 2014 7 NXT07VLSI Exploiting Early Tag Access for Reducing L1 Data Cache Energy in Embedded Processors 2014 8 NXT08VLSI Eliminating Synchronization Latency Using Sequenced Latching 2014 9 NXT09VLSI High-Throughput Low-Energy Self-Timed CAM Based on Reordered Overlapped Search Mechanism 2014 10 NXT10VLSI On Deadlock Problem of On-Chip Buses Supporting Out-of- Order Transactions 2014 11 NXT11VLSI Segmented Architecture for Successive Approximation Analog-to- Digital Converters 2014 12 NXT12VLSI Parameterized All-Digital PLL Architecture and its Compiler to Support Easy Process Migration 2014

- 2. 13 NXT13VLSI Mapping Loop Structures onto Parameterized Hardware Pipelines 2014 14 NXT14VLSI Design for Testability Support for Launch and Capture Power Reduction in Launch-Off-Shift and Launch-Off-Capture Testing 2014 15 NXT15VLSI Data Encoding Techniques for Reducing Energy Consumption in Network-on-Chip 2014 16 NXT16VLSI Thwarting Scan-Based Attacks on Secure-ICs With On-Chip Comparison 2014 17 NXT17VLSI An Optimized Modified Booth Recoder for Efficient Design of the Add-Multiply Operator 2014 18 NXT18VLSI Power-Reduction Technique Using a Single Edge-Tracking Clock for Multiphase Clock and Data Recovery Circuits 2014 19 NXT19VLSI Low-Latency Successive-Cancellation Polar Decoder Architectures Using 2-Bit Decoding 2014 20 NXT20VLSI 32 Bit×32 Bit Multiprecision Razor-Based Dynamic Voltage Scaling Multiplier With Operands Scheduler 2014 21 NXT21VLSI Area-Delay Efficient Binary Adders in QCA 2014 22 NXT22VLSI Software/Hardware Parallel Long-Period Random Number Generation Framework Based on the WELL Method 2014 23 NXT23VLSI Low-Power Digital Signal Processor Architecture for Wireless Sensor Nodes 2014 24 NXT24VLSI Parallel Interleaver Design for a High Throughput HSPA /LTE Multi-Standard Turbo Decoder 2014 25 NXT25VLSI Low-Complexity Reconfigurable Fast Filter Bank for Multi- Standard Wireless Receivers 2014 26 NXT26VLSI LASIC: Loop-Aware Sleepy Instruction Caches Based on STT-RAM Technology 2014 27 NXT27VLSI A Look-Ahead Clock Gating Based on Auto-Gated Flip-Flops 2014 28 NXT28VLSI High-Resolution All-Digital Duty-Cycle Corrector in 65-nm CMOS Technology 2014 29 NXT29VLSI VLSI Design of a Large-Number Multiplier for Fully Homomorphic Encryption 2014

- 3. 30 NXT30VLSI Design of Reversible Synchronous Sequential Circuits Using Pseudo Reed-Muller Expressions 2014 31 NXT31VLSI Low-Power Diagnostic Test Sets for Transition Faults Based on Functional Broadside Tests 2014 32 NXT32VLSI A Fine-Grain Dynamically Reconfigurable Architecture Aimed at Reducing the FPGA-ASIC Gaps 2014 33 NXT33VLSI Low-Cost Control Flow Protection via Available Redundancies in the Microprocessor Pipeline 2014 34 NXT34VLSI A 5.8-GHz Wideband TSPC Divide-by-16/17 Dual Modulus Prescaler 2014 35 NXT35VLSI An Accuracy-Adjustment Fixed-Width Booth Multiplier Based on Multilevel Conditional Probability 2014 36 NXT36VLSI Reliable Low-Power Multiplier Design Using Fixed-Width Replica Redundancy Block 2014 37 NXT37VLSI Exploiting Same Tag Bits to Improve the Reliability of the Cache Memories 2014 38 NXT38VLSI Z-TCAM: An SRAM-based Architecture for TCAM 2014 39 NXT39VLSI A Synergetic Use of Bloom Filters for Error Detection and Correction 2014 40 NXT40VLSI Implementation of a High-Throughput Modified Merge Sort in MIMO Detection Systems 2014 41 NXT41VLSI A Low-Cost Low-Power All-Digital Spread-Spectrum Clock Generator 2014 42 NXT42VLSI Low-Power Test Generation by Merging of Functional Broadside Test Cubes 2014 43 NXT43VLSI Low-Complexity Low-Latency Architecture for Matching of Data Encoded With Hard Systematic Error-Correcting Codes 2014 44 NXT44VLSI Area–Delay–Power Efficient Carry-Select Adder 2014 45 NXT45VLSI Aging-Aware Reliable Multiplier Design With Adaptive Hold Logic 2014 46 NXT46VLSI Input Vector Monitoring Concurrent BIST Architecture Using SRAM Cells 2014

- 4. 47 NXT47VLSI Test Compaction by Sharing of Transparent-Scan Sequences Among Logic Blocks 2014 48 NXT48VLSI An FPGA-Based Fully Synchronized Design of a Bilateral Filter for Real-Time Image Denoising 2014 49 NXT49VLSI Low-Power Pulse-Triggered Flip-Flop Design Based on a Signal Feed-Through Scheme 2014 50 NXT50VLSI Fully Reused VLSI Architecture of FM0/Manchester Encoding Using SOLS Technique for DSRC Applications 2014 ADDRESS Nxtlogic Software Solutions 273, Peranaidu Layout, Ram Nagar, Gandhipurm, Coimbatore - 641 009. Mobile: 98 946 94 339, 99 52 52 84 51. Phone: 0422 - 4342339. E- Mail : nxtlogic@gmail.com Website: www.nxtlogic.com www.studentprojectsincoimbatore.com STUDENT PROJECT TRAINING AND SERVICES ❖ Training By Corporate Trainers ❖ Live Application Environment

- 5. ❖ Coding Explanation ❖ Will Provide Full Source Code Of The Project ❖ Full Documentation And Diagrams (Min 80 Pages) ❖ Some Of Q&A Based On Final Viva ❖ Journal Publications / Conference Publications ❖ Study Materials & Certification ❖ Printing & Binding. ❖ Aptitude and Soft Skill Training. ❖ 100% Placement Assistance. ❖ Full Time/Part Time Job Assistance During Your Project ❖ Own Project Idea Also Welcome